ADC32RF5x 是一款單核 14 位、2.6 GSPS 至 3 GSPS、雙通道模數(shù)轉(zhuǎn)換器 (ADC),支持輸入頻率高達(dá) 3 GHz 的射頻采樣。該設(shè)計(jì)最大限度地提高了信噪比 (SNR),并提供 -155 dBFS/Hz 的噪聲頻譜密度。使用額外的內(nèi)部 ADC 和片上信號(hào)平均,噪聲密度提高到 -161 dBFS/Hz。

每個(gè)ADC通道都可以使用支持相位相干跳頻的48位NCO連接到四頻數(shù)字下變頻器(DDC)。使用GPIO引腳進(jìn)行NCO頻率控制,可以在不到1 μs的時(shí)間內(nèi)實(shí)現(xiàn)跳頻。

*附件:adc32rf55.pdf

該ADC32RF54和ADC32RF55支持具有子類 1 確定性延遲的 JESD204B 串行數(shù)據(jù)接口,數(shù)據(jù)速率高達(dá) 13 Gbps。

高能效ADC架構(gòu)在3 Gsps時(shí)功耗為2.1 W/ch,并以較低的采樣率提供功率擴(kuò)展。

特性

- 14位、雙通道2.6至3GSPS ADC

- 噪聲頻譜密度:

- NSD = -155.6 dBFS/Hz(無(wú)平均值)

- NSD = -158.1 dBFS/Hz(2x 平均)

- NSD = -160.4 dBFS/Hz(4 個(gè)平均值)

- 單核(非交錯(cuò))ADC架構(gòu)

- 孔徑抖動(dòng):50 fs

- 低近距離殘余相位噪聲:

- 10 kHz 偏移時(shí)為 -127 dBc/Hz

- 頻譜性能(f IN = 1 GHz,-4 dBFS):

- 2 倍內(nèi)部平均

- 信噪比:62.3 dBFS

- SFDR HD2,3:63 dBc

- SFDR 最差雜散:85 dBFS

- 頻譜性能(f IN = 1.8 GHz,-4 dBFS):

- 2 倍內(nèi)部平均

- 信噪比:63 dBFS

- SFDR HD2,3:68 dBc

- SFDR 最差雜散:86 dBFS

- 輸入滿量程:1.1 至 1.35 Vpp(2 至 3.5 dBm)

- 代碼錯(cuò)誤率 (CER):10 -15

- 全功率輸入帶寬 (-3 dB):2.75 GHz

- JESD204B串行數(shù)據(jù)接口

- 最大通道速率:13 Gbps

- 支持子類 1 確定性延遲

- 數(shù)字下變頻器

- 每個(gè)ADC通道最多4個(gè)DDC

- 復(fù)輸出:4 倍至 128 倍抽取

- 48 位 NCO 相位相干跳頻

- 快速跳頻:< 1 us

- 功耗:2.6 W/通道(2x AVG)

- 電源:1.8 V、1.2 V

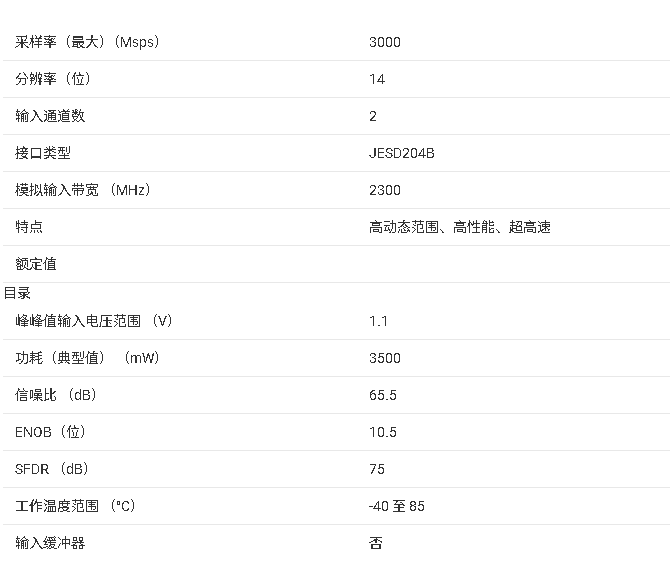

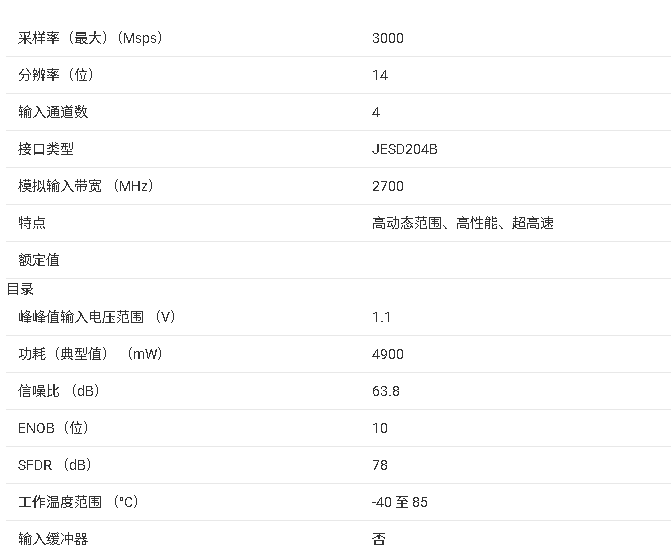

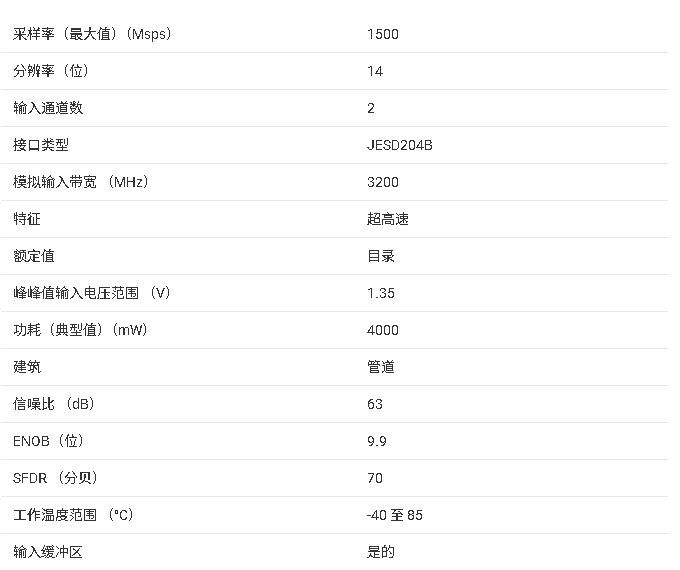

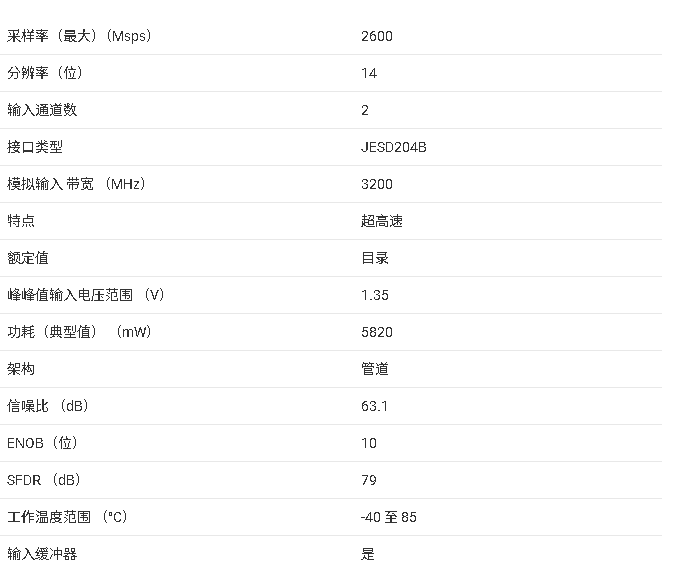

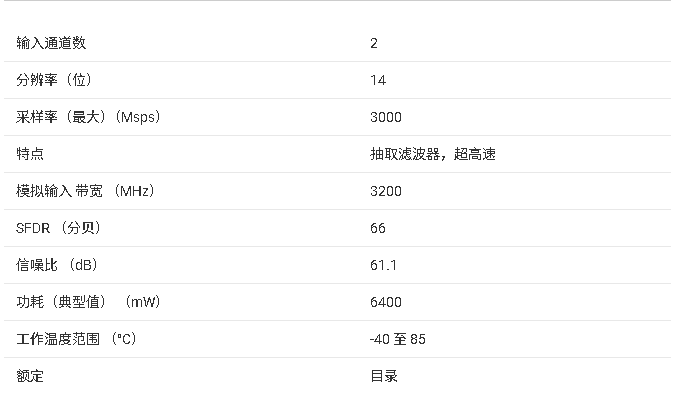

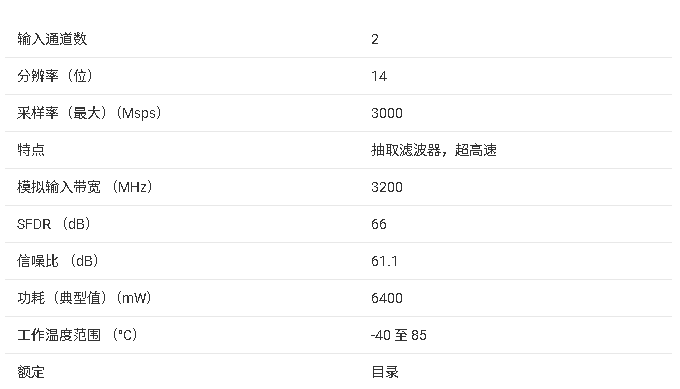

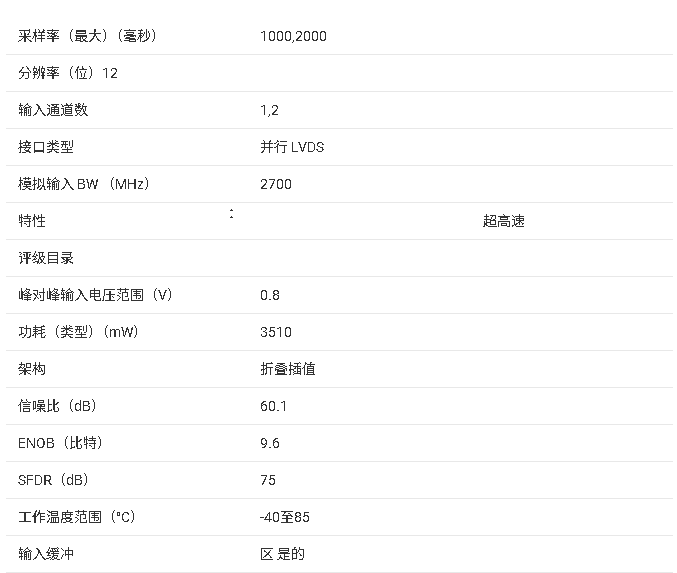

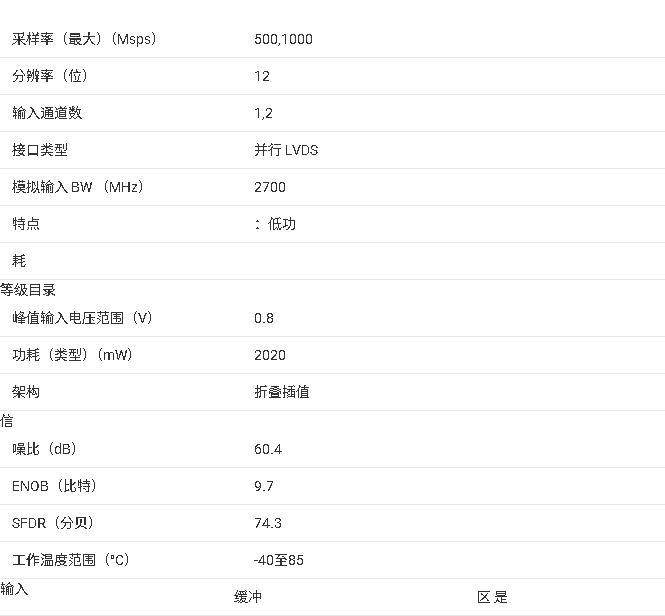

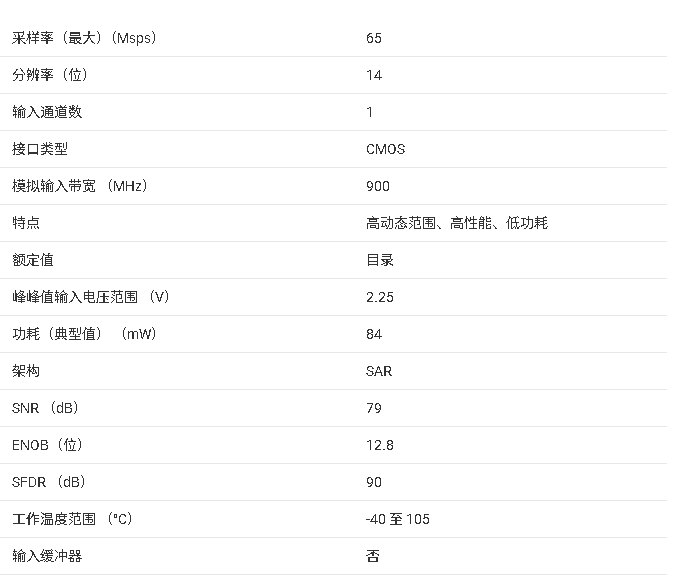

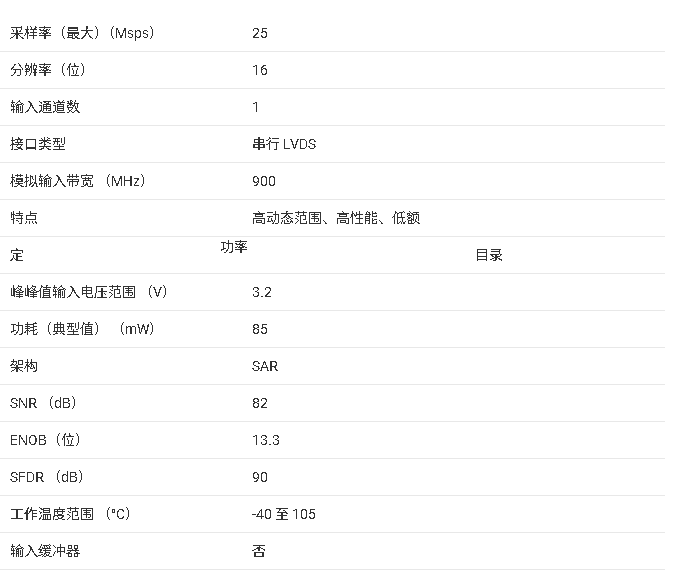

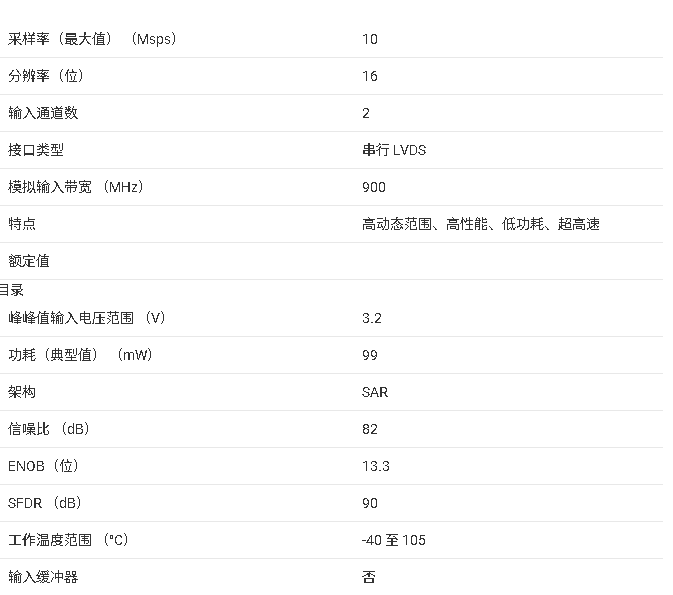

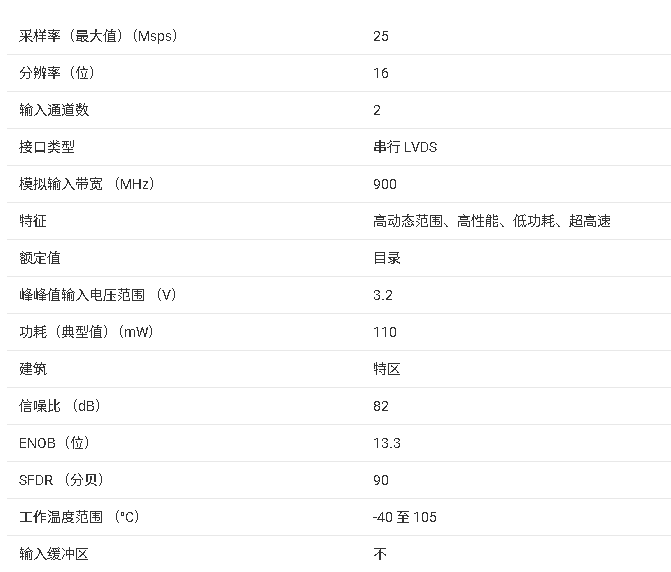

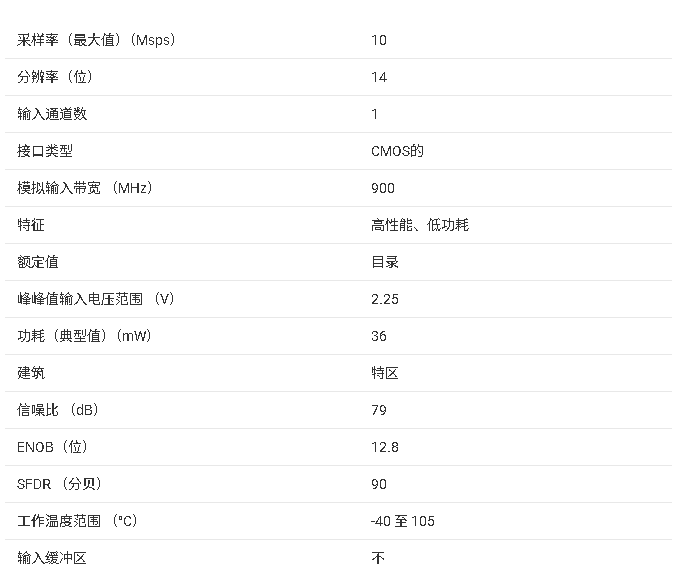

參數(shù)

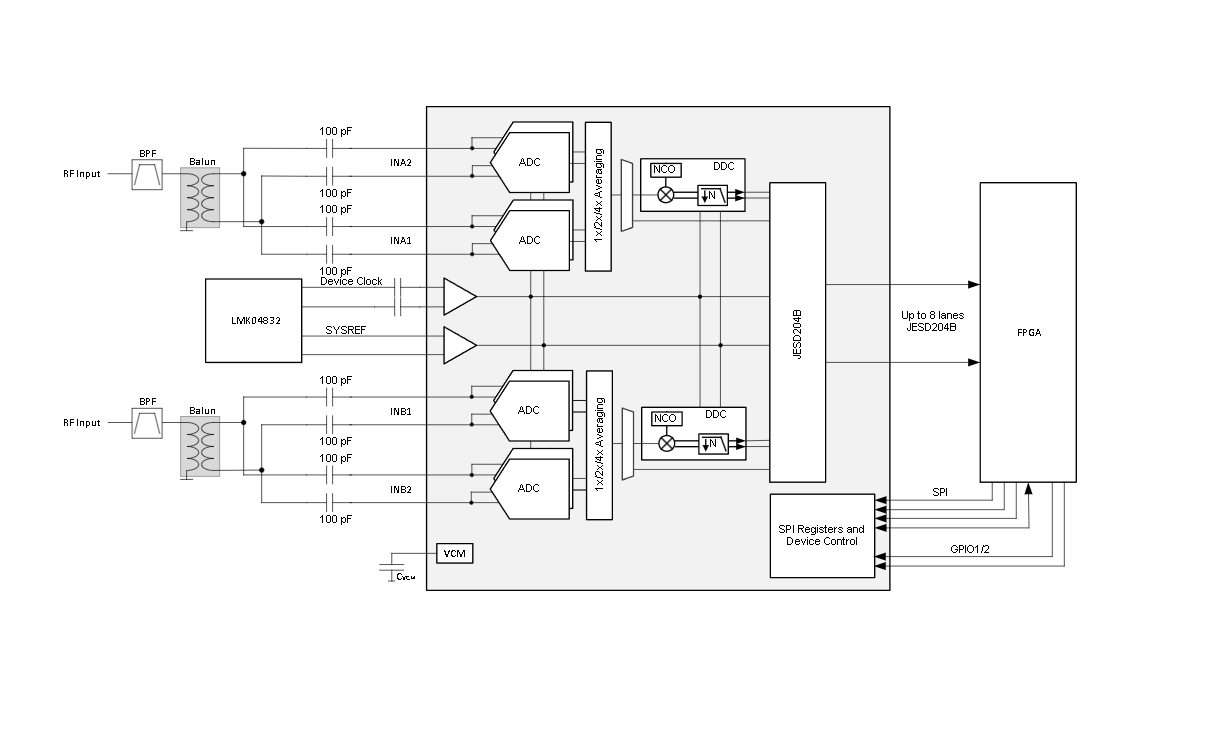

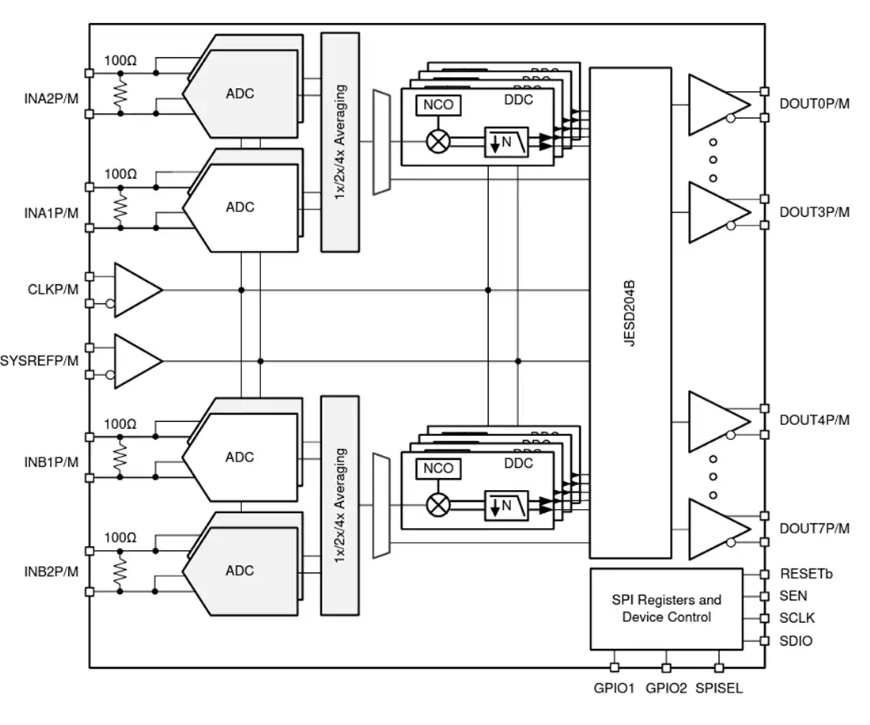

方框圖

一、產(chǎn)品概述與型號(hào)差異

ADC32RF5x 系列是專為射頻采樣設(shè)計(jì)的高性能雙通道 ADC,通過(guò)單核心(非交錯(cuò))架構(gòu)、內(nèi)部信號(hào)平均、可編程 DDC 等技術(shù),平衡高采樣率、低噪聲與靈活信號(hào)處理能力。兩款型號(hào)僅采樣速率不同,其他功能與封裝完全兼容,便于根據(jù)系統(tǒng)帶寬需求選型。

1. 型號(hào)核心差異

| 型號(hào) | 最高采樣速率 | 核心應(yīng)用場(chǎng)景 | 關(guān)鍵性能差異(典型值,TA=25℃) |

|---|---|---|---|

| ADC32RF54 | 2.6 GSPS | 中高頻段信號(hào)采集(如 L 波段) | 1GHz 輸入時(shí) SNR 62.3 dBFS,噪聲譜密度(NSD)-155.6 dBFS/Hz |

| ADC32RF55 | 3.0 GSPS | 超高頻段信號(hào)采集(如 S 波段) | 1.8GHz 輸入時(shí) SNR 63 dBFS,NSD-158.1 dBFS(2x 平均) |

2. 基礎(chǔ)參數(shù)總覽

| 類別 | 關(guān)鍵指標(biāo) | 說(shuō)明 |

|---|---|---|

| 封裝規(guī)格 | 9mm×9mm 64 引腳 VQFN(RTD 封裝) | 無(wú)鉛封裝,0.9mm 最大高度,底部熱焊盤(pán)(需接地),適配高密度射頻布局 |

| 工作溫度 | -40℃~+85℃ | 滿足工業(yè)級(jí)寬溫環(huán)境需求 |

| 供電范圍 | AVDD18:1.75V | 四組獨(dú)立供電,CLKVDD 需低噪聲電源,避免影響時(shí)鐘相位噪聲 |

| 靜態(tài)功耗 | 2.6 GSPS(2x 平均):5.25W;3.0 GSPS(4x 平均):7.1W | 功耗隨采樣率與平均模式線性增加,支持關(guān)斷未用通道降功耗 |

| 核心集成 | 14 位 ADC 核心 ×8(用于平均)、48 位 NCO、JESD204B 接口、內(nèi)部校準(zhǔn)模塊 | 減少外圍器件,簡(jiǎn)化射頻采樣系統(tǒng)設(shè)計(jì) |

二、核心功能與性能參數(shù)

1. 高速射頻采樣模塊

作為核心功能,ADC32RF5x 支持直接射頻采樣(輸入頻率最高 3GHz),通過(guò)內(nèi)部多 ADC 平均技術(shù)優(yōu)化噪聲性能,適配不同精度需求:

(1)性能參數(shù)

- 分辨率與精度 :

- 14 位分辨率,微分非線性(DNL)±0.85 LSB,積分非線性(INL)±3.5 LSB;

- 噪聲特性:無(wú)平均時(shí) NSD-155.6 dBFS/Hz,2x 平均時(shí) - 158.1 dBFS/Hz,4x 平均時(shí) - 160.4 dBFS/Hz;

- 孔徑抖動(dòng):典型 50 fs,近距殘余相位噪聲 - 127 dBc/Hz(10kHz 偏移),保障高頻采樣精度。

- 輸入特性 :

- 動(dòng)態(tài)性能 :

- 信噪比(SNR):1GHz 輸入、2x 平均時(shí) 62.3 dBFS,1.8GHz 輸入時(shí) 63 dBFS;

- 無(wú)雜散動(dòng)態(tài)范圍(SFDR):1GHz 輸入時(shí) 85 dBFS,二階諧波(HD2)63 dBc,三階諧波(HD3)68 dBc;

- 建立時(shí)間:65 ns(1/4~3/4 量程,±2 LSB),支持快速信號(hào)跳變捕獲。

(2)關(guān)鍵功能

- 多模式平均 :支持 1x(無(wú)平均)、2x、4x 內(nèi)部 ADC 平均,通過(guò)多核心并行采樣降低噪聲(每 2x 平均噪聲改善~3 dB),4x 平均時(shí)需將輸入信號(hào)分至 INx1/INx2 引腳;

- 模擬抖動(dòng)抑制 :可選模擬帶外抖動(dòng)(帶寬~20MHz,幅度 ±1024 碼),降低低階諧波失真,1GHz 輸入時(shí) SFDR 提升至 89 dBFS;

- 過(guò)范圍檢測(cè) :支持 GPIO 引腳快速指示(延遲~6 時(shí)鐘周期)或 JESD 數(shù)據(jù)流嵌入(替換 LSB),過(guò)范圍標(biāo)志可通過(guò) SPI 清零,適配故障安全設(shè)計(jì)。

2. 數(shù)字下變頻器(DDC)模塊

每個(gè) ADC 通道集成 4 個(gè)可編程 DDC,支持復(fù)雜信號(hào)下變頻與抽取,減少后端處理器數(shù)據(jù)帶寬壓力:

(1)性能參數(shù)

- 抽取范圍 :4x~128x 復(fù)雜抽取,支持單頻段(1 個(gè) DDC)、雙頻段(2 個(gè) DDC)、四頻段(4 個(gè) DDC)模式;

- NCO 精度 :48 位相位累加器,頻率分辨率 ±0.001 Hz(3GSPS 采樣時(shí)),支持相位相干跳頻,跳頻時(shí)間 < 1μs;

- 濾波特性 :復(fù)雜抽取模式下通帶帶寬~80%,阻帶抑制≥85 dB;實(shí)抽取模式下通帶帶寬~40%,無(wú)頻率偏移。

(2)關(guān)鍵功能

- 靈活頻段配置 :?jiǎn)晤l段模式支持 4x 抽取(帶寬 750MHz@3GSPS),四頻段模式支持 128x 抽取(帶寬 23.4MHz@3GSPS),適配寬窄帶信號(hào)并行處理;

- 相位相干跳頻 :通過(guò) SYSREF 信號(hào)同步 NCO 相位,多次跳頻后相位連續(xù),無(wú)相位突變導(dǎo)致的雜散;

- 動(dòng)態(tài)模式切換 :支持單頻段與四頻段模式動(dòng)態(tài)切換(無(wú)需重啟 JESD 接口),切換時(shí)保持 SerDes 速率與 lanes 數(shù)不變,適配多帶寬場(chǎng)景。

3. JESD204B 高速接口模塊

集成 JESD204B 串行數(shù)據(jù)接口,支持高速數(shù)據(jù)傳輸與確定性延遲,適配 FPGA / 處理器后端處理:

(1)性能參數(shù)

- 傳輸速率 :最高 13 Gbps/lane,支持 8 lanes 并行,總帶寬 104 Gbps(3GSPS 時(shí));

- 延遲特性 :子類 1 確定性延遲,抽取 4x 時(shí)延遲 456 時(shí)鐘周期,支持多器件同步;

- 信號(hào)完整性 :輸出擺幅 700 mVpp(差分),隨機(jī)抖動(dòng)(RJ)0.6 ps RMS(12.8 Gbps),確定性抖動(dòng)(DJ)14.7 ps pp。

(2)關(guān)鍵功能

- 多幀配置 :支持 LMFS(L=M=F=S)靈活配置,如 8-2-8-20(8 lanes、2 轉(zhuǎn)換器、8 字節(jié) / 幀、20 幀 / 多幀),適配不同數(shù)據(jù)壓縮需求;

- 初始 lane 對(duì)齊(ILA) :自動(dòng)發(fā)送 K28.5 逗號(hào)字符實(shí)現(xiàn)碼組同步,支持 4 個(gè)多幀的 ILA 序列,保障多 lane 數(shù)據(jù)對(duì)齊;

- 測(cè)試模式 :支持 PRBS(2^7-1 至 2^31-1)、 Ramp、交替碼型輸出,簡(jiǎn)化接口調(diào)試,無(wú)需接入實(shí)際模擬信號(hào)。

4. 校準(zhǔn)與同步模塊

(1)Foreground 校準(zhǔn)

- 校準(zhǔn)對(duì)象 :補(bǔ)償 ADC 增益 / 偏移誤差、溫度漂移,支持單通道 / 雙通道同時(shí)校準(zhǔn);

- 校準(zhǔn)方式 :通過(guò) SPI 觸發(fā)或 GPIO1 引腳觸發(fā),校準(zhǔn)時(shí)間~23 ms×3GSPS / 實(shí)際采樣率,校準(zhǔn)后 INL 改善至 ±2 LSB;

- 后臺(tái)校準(zhǔn) :支持連續(xù)校準(zhǔn)模式,切換備用 ADC 核心時(shí)輸出幅度波動(dòng) < 0.05 dB,相位變化 < 0.01°,無(wú)數(shù)據(jù)丟失。

(2)系統(tǒng)同步(SYSREF)

- 同步功能 :外部 SYSREF 信號(hào)(差分輸入,100Ω 端接)用于復(fù)位 NCO、DDC 與 JESD 接口,實(shí)現(xiàn)多 ADC 相位同步;

- 捕獲窗口 :內(nèi)置 ±50 ps SYSREF 捕獲窗口監(jiān)測(cè),避免時(shí)鐘滑移導(dǎo)致的同步誤差,支持 AC/DC 耦合配置;

- 多器件同步 :SYSREF 頻率需為內(nèi)部多幀時(shí)鐘(LMFC)的子諧波,支持 16 個(gè) SYSREF 脈沖后自動(dòng)停止捕獲,適配大規(guī)模多芯片系統(tǒng)。

三、功能架構(gòu)與典型應(yīng)用

1. 核心架構(gòu)

采用 “模擬采樣 - 數(shù)字處理 - 高速傳輸” 三層架構(gòu),模塊協(xié)同實(shí)現(xiàn)高可靠性射頻采樣:

- 模擬采樣層 :雙通道獨(dú)立 ADC 核心(每通道含 4 個(gè)內(nèi)部 ADC 用于平均),支持 100Ω/50Ω 輸入端接,模擬抖動(dòng)抑制;

- 數(shù)字處理層 :每通道 4 個(gè) DDC(含 48 位 NCO)、抽取濾波器、過(guò)范圍檢測(cè)邏輯,實(shí)現(xiàn)信號(hào)下變頻與帶寬壓縮;

- 高速傳輸層 :JESD204B 接口(8 lanes)、SerDes 輸出 MUX(支持 lane 重排序)、測(cè)試模式生成器,保障數(shù)據(jù)高速傳輸與調(diào)試。

2. 典型應(yīng)用場(chǎng)景:寬帶射頻采樣接收機(jī)

(1)應(yīng)用原理

ADC32RF55 直接采樣 3GHz 以下射頻信號(hào),通過(guò) 2x 內(nèi)部平均降低噪聲(NSD-158.1 dBFS/Hz),DDC 將信號(hào)下變頻至中頻(如 75MHz)并 16x 抽取,數(shù)據(jù)通過(guò) JESD204B 接口傳輸至 FPGA(如 Xilinx UltraScale+)進(jìn)行后續(xù)信號(hào)處理:

- 核心電路 :射頻信號(hào)經(jīng) Balun 變壓器(如 Marki BAL-0009SMG)轉(zhuǎn)換為差分信號(hào),AC 耦合至 INx1 引腳;采樣時(shí)鐘由低噪聲時(shí)鐘源(如 LMK04832)提供,SYSREF 信號(hào)同步多 ADC;

- 關(guān)鍵參數(shù) :3GSPS 采樣、4x 抽取時(shí),有效帶寬 750MHz,SNR 65 dBFS,滿足相控陣?yán)走_(dá)多通道信號(hào)采集需求。

(2)設(shè)計(jì)要點(diǎn)

- 電源設(shè)計(jì) :AVDD18/AVDD12/CLKVDD/DVDD 需獨(dú)立供電,CLKVDD 采用低噪聲 LDO(如 TPS7A8400),各電源引腳就近并 0.1μF 陶瓷電容 + 10μF 鉭電容,抑制射頻噪聲;

- 布局建議 :模擬輸入(INx1/INx2)與時(shí)鐘(CLKP/M)采用 100Ω 差分布線,長(zhǎng)度匹配誤差 < 5 mil;數(shù)字信號(hào)(JESD lanes)與模擬信號(hào)分區(qū)隔離,模擬地與數(shù)字地單點(diǎn)連接;

- 同步設(shè)計(jì) :SYSREF 信號(hào)與采樣時(shí)鐘邊緣對(duì)齊,使用 50Ω 阻抗匹配,布線長(zhǎng)度短于 10cm,避免同步延遲導(dǎo)致的相位偏差。

四、電氣特性與設(shè)計(jì)建議

1. 關(guān)鍵電氣特性(典型值,TA=25℃,VDD=1.8V/1.2V)

| 參數(shù)類別 | 指標(biāo)(ADC32RF55,3GSPS,2x 平均) | 指標(biāo)(ADC32RF54,2.6GSPS,1x 平均) |

|---|---|---|

| 靜態(tài)精度 | INL±3.5 LSB,DNL±0.85 LSB,增益誤差 ±0.2 dB | INL±3.2 LSB,DNL±0.8 LSB,增益誤差 ±0.3 dB |

| 動(dòng)態(tài)特性 | SNR 63 dBFS(1.8GHz 輸入),SFDR 86 dBFS | SNR 62.3 dBFS(1GHz 輸入),SFDR 85 dBFS |

| 電源抑制比 | AC -68 dB(50Hz/60Hz),DC 0.25 mV/V | AC -65 dB(50Hz/60Hz),DC 0.3 mV/V |

| 功耗 | AVDD18 電流 370mA,DVDD 電流 2440mA,總功耗 5.25W | AVDD18 電流 230mA,DVDD 電流 1550mA,總功耗 3.4W |

2. 設(shè)計(jì)建議

(1)電源與時(shí)鐘設(shè)計(jì)

- 電源隔離 :AVDD12/CLKVDD 與 DVDD 不可共地,避免數(shù)字開(kāi)關(guān)噪聲耦合至模擬電路;推薦采用 “開(kāi)關(guān)電源 + LDO” 兩級(jí)供電,開(kāi)關(guān)電源(如 LMS3635)提供高效率,LDO 抑制開(kāi)關(guān)噪聲;

- 時(shí)鐘優(yōu)化 :采樣時(shí)鐘幅度需 > 1 Vpp(差分),使用帶通濾波器(如 Mini-Circuits TCM2-43X+)濾除時(shí)鐘雜散,時(shí)鐘線與模擬輸入線間距 > 2mm,減少串?dāng)_。

(2)PCB 布局

- 分區(qū)設(shè)計(jì) :將模擬區(qū)(INx1/INx2、CLKP/M、VREF)、數(shù)字區(qū)(JESD lanes、SPI)、電源區(qū)(LDO、濾波電容)嚴(yán)格分區(qū),模擬區(qū)鋪銅厚度≥2oz,降低阻抗;

- 熱設(shè)計(jì) :底部熱焊盤(pán)通過(guò) 4 個(gè)過(guò)孔連接至大面積接地銅皮,結(jié)到環(huán)境熱阻 RθJA=20.1℃/W,確保滿負(fù)荷時(shí)結(jié)溫 < 105℃;

- 射頻防護(hù) :模擬輸入引腳附近預(yù)留 50Ω/100Ω 匹配電阻位置,INx2 引腳未使用時(shí)需接地,避免噪聲耦合。

(3)校準(zhǔn)與同步配置

- 上電校準(zhǔn) :上電后需執(zhí)行 Foreground 校準(zhǔn)(SPI 寫(xiě)入 0x20 頁(yè) 0x45 寄存器),校準(zhǔn)前確保 SYSREF 信號(hào)穩(wěn)定,校準(zhǔn)后 INL 改善至 ±2 LSB;

- SYSREF 配置 :通過(guò) 0x02 頁(yè) 0x236 寄存器啟用 SYSREF 計(jì)數(shù),AC 耦合時(shí)需配置 0xB4 寄存器啟用內(nèi)部偏置,確保同步窗口內(nèi)無(wú)信號(hào)跳變;

- JESD 調(diào)試 :初期可啟用 Ramp 測(cè)試模式(0x04 頁(yè) 0x2E 寄存器),驗(yàn)證 lane 對(duì)齊與數(shù)據(jù)傳輸,無(wú)誤后切換至正常采樣模式。

-

adc

+關(guān)注

關(guān)注

100文章

7932瀏覽量

556755 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

4096瀏覽量

130229 -

串行數(shù)據(jù)

+關(guān)注

關(guān)注

0文章

69瀏覽量

16987 -

噪聲頻譜

+關(guān)注

關(guān)注

0文章

28瀏覽量

2260

發(fā)布評(píng)論請(qǐng)先 登錄

ADC32RF5x雙通道14位2.6至3GSPS射頻采樣數(shù)據(jù)轉(zhuǎn)換器數(shù)據(jù)表

高性能射頻采樣ADC:ADC32RF5x系列技術(shù)解析

ADC34RF55 技術(shù)文檔總結(jié)

ADC32RF54雙通道 14 位高速 RF 采樣 ADC 技術(shù)總結(jié)

ADC32RF42 技術(shù)文檔核心總結(jié)

ADC32RF44 技術(shù)文檔核心總結(jié)

ADC32RF8x 技術(shù)文檔核心總結(jié)

ADC32RF8x 系列產(chǎn)品核心信息總結(jié)

ADC12D1000RF 12 位高采樣率 RF 采樣 ADC 技術(shù)文檔總結(jié)

ADC12D500RF 12 位中高速 RF 采樣 ADC 技術(shù)文檔總結(jié)

ADC32RF5x 系列技術(shù)文檔總結(jié)

ADC32RF5x 系列技術(shù)文檔總結(jié)

評(píng)論