ADC32RF5x 是一款單核 14 位、2.6 GSPS 至 3 GSPS、雙通道模數轉換器 (ADC),支持輸入頻率高達 3 GHz 的射頻采樣。該設計最大限度地提高了信噪比 (SNR),并提供 -155 dBFS/Hz 的噪聲頻譜密度。使用額外的內部 ADC 和片上信號平均,噪聲密度提高到 -161 dBFS/Hz。

每個ADC通道都可以使用支持相位相干跳頻的48位NCO連接到四頻數字下變頻器(DDC)。使用GPIO引腳進行NCO頻率控制,可以在不到1 μs的時間內實現跳頻。

*附件:adc32rf54.pdf

該ADC32RF54和ADC32RF55支持具有子類 1 確定性延遲的 JESD204B 串行數據接口,數據速率高達 13 Gbps。

高能效ADC架構在3 Gsps時功耗為2.1 W/ch,并以較低的采樣率提供功率擴展。

特性

- 14位、雙通道2.6至3GSPS ADC

- 噪聲頻譜密度:

- NSD = -155.6 dBFS/Hz(無平均值)

- NSD = -158.1 dBFS/Hz(2x 平均)

- NSD = -160.4 dBFS/Hz(4 個平均值)

- 單核(非交錯)ADC架構

- 孔徑抖動:50 fs

- 低近距離殘余相位噪聲:

- 10 kHz 偏移時為 -127 dBc/Hz

- 頻譜性能(f IN = 1 GHz,-4 dBFS):

- 2 倍內部平均

- 信噪比:62.3 dBFS

- SFDR HD2,3:63 dBc

- SFDR 最差雜散:85 dBFS

- 頻譜性能(f IN = 1.8 GHz,-4 dBFS):

- 2 倍內部平均

- 信噪比:63 dBFS

- SFDR HD2,3:68 dBc

- SFDR 最差雜散:86 dBFS

- 輸入滿量程:1.1 至 1.35 Vpp(2 至 3.5 dBm)

- 代碼錯誤率 (CER):10 -15

- 全功率輸入帶寬 (-3 dB):2.75 GHz

- JESD204B串行數據接口

- 最大通道速率:13 Gbps

- 支持子類 1 確定性延遲

- 數字下變頻器

- 每個ADC通道最多4個DDC

- 復輸出:4 倍至 128 倍抽取

- 48 位 NCO 相位相干跳頻

- 快速跳頻:< 1 us

- 功耗:2.6 W/通道(2x AVG)

- 電源:1.8 V、1.2 V

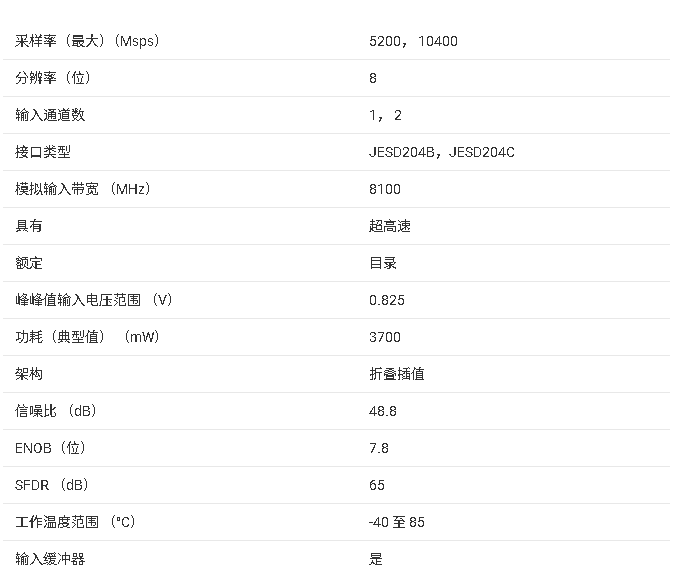

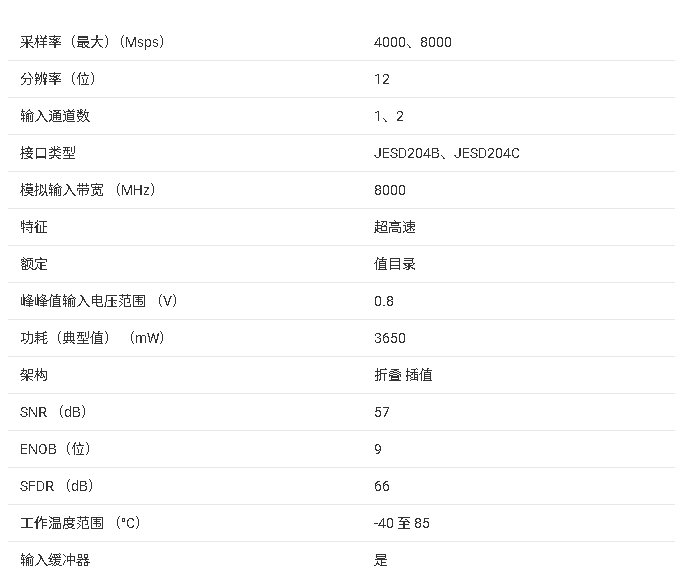

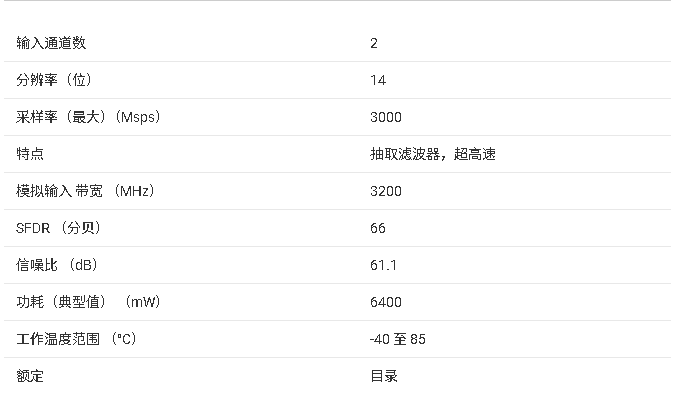

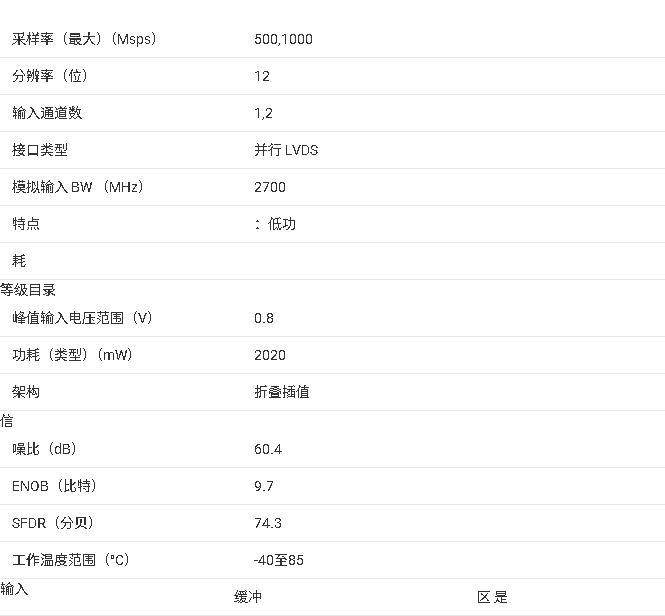

參數

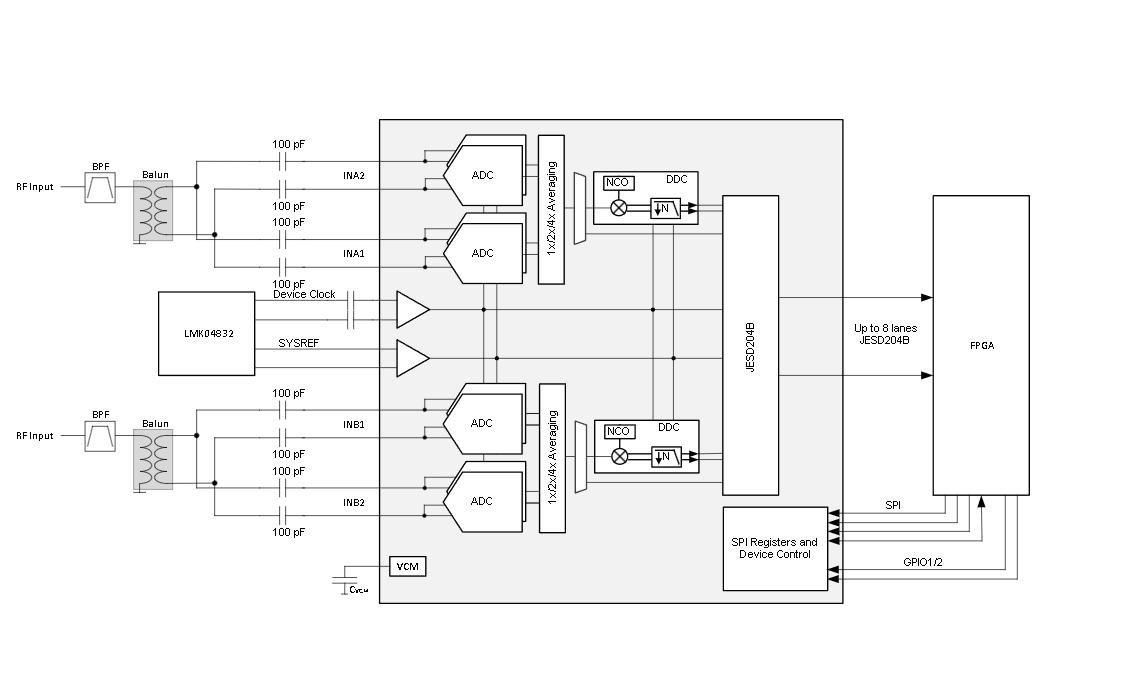

方框圖

ADC32RF54/ADC32RF55 是德州儀器(Texas Instruments)推出的 雙通道 14 位高速 RF 采樣 ADC ,采用單核非交錯架構,采樣速率分別達 2.6 GSPS(ADC32RF54)與 3.0 GSPS(ADC32RF55),專為雷達、頻譜分析儀、軟件定義無線電(SDR)、電子戰及高速數字化儀等高頻高精度場景設計。其核心優勢在于低噪聲譜密度、靈活的數字下變頻器(DDC)配置及高帶寬輸入,可直接對 RF 信號采樣,簡化系統前端設計。以下從核心特性、性能參數、功能模塊、應用設計及訂購信息等方面展開總結。

一、核心特性與產品定位

1. 基礎參數與架構

- ADC 核心配置 :雙通道同步采樣,14 位分辨率,單核非交錯架構(避免交錯失真);每通道支持 1×/2×/4× 內部數字平均,通過多 ADC 核心并行采樣提升噪聲性能,噪聲譜密度(NSD)最低可達 - 160.4 dBFS/Hz(4× 平均)。

- RF 采樣能力 :全功率輸入帶寬(-3 dB)達 2.75 GHz(1×/2× 平均)、2.1 GHz(4× 平均),支持直接對 L 波段及以下 RF 信號采樣;輸入差分阻抗可配置為 50 Ω/100 Ω,適配常見 RF 前端電路。

- 低抖動與相位噪聲 :孔徑抖動僅 50 fs,近載頻殘余相位噪聲低至 - 127 dBc/Hz(10 kHz 偏移),保障高頻信號采樣精度;采樣時鐘路徑獨立供電(CLKVDD),降低電源噪聲對相位的影響。

- 數字信號處理 :每通道集成 4 個數字下變頻器(DDC),支持 4×-128× 復數抽取,48 位數控振蕩器(NCO)實現相位相干跳頻(跳頻時間 < 1 μs);支持實抽取與復抽取模式,適配不同帶寬信號處理需求。

- 接口與兼容性 :JESD204B 串行接口(子類 1 確定性延遲),最高 lane 速率 13 Gbps,支持 8 路 SerDes 輸出;兼容 SPI 配置與 GPIO 快速控制,支持測試模式與內部采樣緩存,便于系統調試。

- 環境適應性 :工作溫度范圍 - 40°C 至 85°C,結溫最高 125°C;ESD 防護達人體放電模型(HBM)±1000 V、帶電器件模型(CDM)±500 V;采用 64 引腳 VQFN(RTD 封裝),尺寸 9 mm×9 mm,底部熱焊盤優化散熱。

2. 型號差異

| 型號 | 采樣速率 | 關鍵性能差異(典型值,f_IN=900 MHz,-4 dBFS) |

|---|---|---|

| ADC32RF54 | 2.6 GSPS | 1× 平均時 SNR=62.7 dBFS,SFDR(非諧波)=89 dBFS |

| ADC32RF55 | 3.0 GSPS | 1× 平均時 SNR=60.9 dBFS,SFDR(非諧波)=85 dBFS |

二、關鍵性能指標

1. 核心電氣性能(典型值,TA=25°C,DVDD=1.2 V,AVDD18=1.8 V)

| 性能參數 | 測試條件(ADC32RF55,3.0 GSPS) | 最小值 | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|---|

| 噪聲譜密度(NSD) | 無平均,f_IN=-20 dBFS | - | -155.6 | - | dBFS/Hz |

| 2× 平均,f_IN=-20 dBFS | - | -158.1 | - | dBFS/Hz | |

| 4× 平均,f_IN=-20 dBFS | - | -160.4 | - | dBFS/Hz | |

| 信噪比(SNR) | f_IN=1 GHz,1× 平均,-4 dBFS | - | 62.3 | - | dBFS |

| f_IN=1.8 GHz,2× 平均,-4 dBFS | - | 63.0 | - | dBFS | |

| 無雜散動態范圍(SFDR) | f_IN=1 GHz,1× 平均,-4 dBFS(非諧波) | - | 85 | - | dBFS |

| f_IN=1.8 GHz,2× 平均,-4 dBFS(諧波 2/3) | - | 68 | - | dBc | |

| 總諧波失真(THD) | f_IN=1 GHz,1× 平均,-4 dBFS | - | -102 | -94 | dBc |

| 孔徑抖動 | 采樣時鐘幅度 1 Vpp | - | 50 | - | fs |

| 輸入滿量程(FS) | 差分輸入,1×/2× 平均 | 1.1 | 1.2 | 1.35 | Vpp |

| 差分輸入,4× 平均 | 1.1 | 1.35 | - | Vpp | |

| 通道隔離度 | 相鄰通道間,f_IN=1 GHz | - | -120 | - | dBc |

2. 電源與熱性能

| 性能參數 | 測試條件(ADC32RF55,3.0 GSPS) | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|

| 功耗(PDIS) | 1× 平均,DDC 旁路模式 | 4.2 | - | W |

| 2× 平均,DDC 使能(抽取 4×) | 5.25 | - | W | |

| 4× 平均,DDC 使能(抽取 16×) | 7.1 | - | W | |

| 電源電流 | AVDD18(1.8 V 模擬供電),4× 平均 | 560 | 620 | mA |

| DVDD(1.2 V 數字供電),4× 平均 | 3020 | 4200 | mA | |

| 結溫(TJ) | 正常工作模式 | - | 105 | °C |

| 結到環境熱阻(RθJA) | 64 引腳 VQFN 封裝,自然散熱 | - | 20.1 | °C/W |

三、核心功能模塊

1. 模擬前端與采樣機制

(1)輸入電路與平均模式

- 輸入架構 :每通道支持 2 路外部輸入(INx1P/M、INx2P/M),1× 平均僅用 INx1,2× 平均復用 INx1(內部 2 個 ADC 核心),4× 平均同時用 INx1 與 INx2(各 2 個 ADC 核心);輸入內置 100 Ω/50 Ω 差分端接,可通過 SPI 配置(寄存器 0x7B/8B)。

- 數字平均 :通過多 ADC 核心采樣結果平均,降低非相關噪聲(如熱噪聲),理想情況下每 2× 平均噪聲改善 3 dB;平均模式下輸出分辨率自動擴展至 16 位,避免量化噪聲惡化,4× 平均時有效位數(ENOB)可達 10.0 Bits(f_IN=100 MHz)。

(2)采樣時鐘與同步

- 時鐘輸入 :差分時鐘輸入(CLKP/M),支持 500 MHz-3.0 GHz 頻率范圍,推薦時鐘幅度 1-2.4 Vpp;獨立 CLKVDD 供電,需外接低噪聲 LDO(如 TPS7A8400),降低電源噪聲對時鐘相位的影響。

- SYSREF 同步 :支持外部 SYSREF 信號同步(AC/DC 耦合可選),用于多器件同步采樣與 NCO 相位校準;SYSREF 捕獲窗口監測功能(±50 ps),避免時鐘與 SYSREF 錯位導致的同步誤差。

2. 數字下變頻器(DDC)與 NCO

(1)DDC 配置

- 抽取與濾波 :每通道 4 個 DDC,支持 4×-128× 復數抽取(復抽取)或 4×-128× 實抽取(實抽取);復抽取模式下采用 80% 通帶帶寬濾波器,實抽取模式下采用 40% 通帶帶寬濾波器,阻帶抑制≥85 dB。

- 多頻段支持 :支持單頻段(1 個 DDC)、雙頻段(2 個 DDC)、四頻段(4 個 DDC)模式,四頻段時每頻段最高抽取 128×,適配多信號并行處理場景(如多目標雷達)。

(2)NCO 功能

- 相位相干跳頻 :48 位 NCO 支持頻率范圍 ±FS/2,頻率分辨率 FS/2??,跳頻時間 < 1 μs(通過 GPIO 控制);支持相位連續與相位相干模式,相位相干模式下多頻率跳變無相位突變,適配雷達波束成形等場景。

- 頻率配置 :每 DDC 可預存 4 個頻率,通過 SPI 或 GPIO 快速切換;NCO 頻率計算公式為,例如 FS=3 GSPS 時,920 MHz 對應 NCO 寄存器值為 0x4E81B4E81B4E。

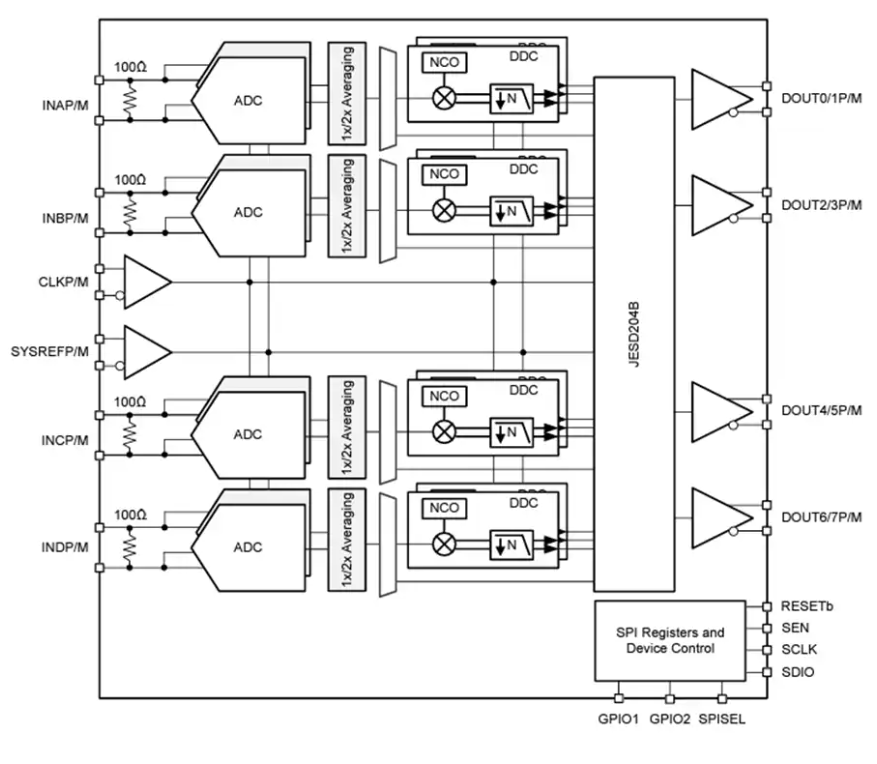

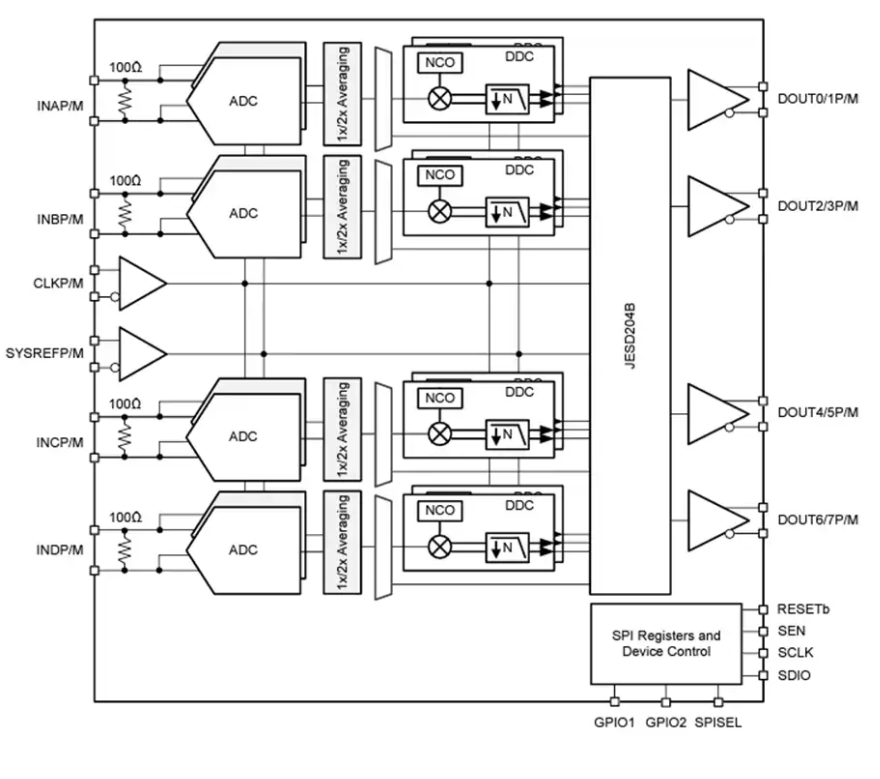

3. JESD204B 接口與數據傳輸

(1)接口配置

- 基本參數 :支持 8 路 SerDes 輸出,每 lane 最高速率 13 Gbps;支持 LMFS(L-M-F-S)配置,例如 LMFS=8-2-8-20(8 lane,2 轉換器,8 字節 / 幀,20 幀 / 多幀),適配不同數據率與分辨率需求。

- 確定性延遲 :子類 1 模式下延遲可配置,例如抽取 4× 時延遲約 44 個采樣時鐘周期,保障多器件同步數據傳輸。

(2)數據幀結構

- 旁路模式 :14 位數據直接輸出,2.6-3.0 GSPS 時采用 12 位輸出(截斷 2 個 LSB),LMFS=8-2-8-20;2.6 GSPS 以下支持 14/16 位輸出,LMFS=8-2-2-4。

- 抽取模式 :輸出 16 位數據(平均模式)或 20 位數據(高抽取模式,避免量化噪聲),20 位模式下數據擴展為 32 位(補 12 個 0),通過 2 個連續 16 位幀傳輸。

4. 校準與故障監測

(1)Foreground 校準

- 校準機制 :內置額外 ADC 核心用于校準,支持單次校準、連續校準與 GPIO 觸發校準;校準覆蓋偏移、增益與非線性誤差,校準時間約 23 ms×3 GSPS/FS(每 ADC 對),校準后 INL≤±3.5 LSB,DNL≤±0.85 LSB。

- 溫度補償 :校準結果隨溫度動態調整,保障 - 40°C 至 85°C 范圍內性能穩定,增益漂移≤25 ppm/°C。

(2)過 range 與故障檢測

- 過 range 指示 :支持 GPIO 輸出(6 個時鐘周期延遲)或 JESD 數據嵌入(替換 LSB),過 range 標志可配置為粘性(需 SPI 清除)或非粘性(自動清除)。

- 內部監測 :集成 64 點采樣緩存,可捕獲 ADC 原始數據(無平均 / 抽取),用于前端模擬電路調試;支持 PRBS、斜坡等測試模式,驗證 JESD 鏈路完整性。

四、應用設計要點

1. 電源與布局設計

- 供電配置 :

- 模擬供電:AVDD18(1.8 V)、AVDD12(1.2 V),需外接 1 μF+0.1 μF 去耦電容(靠近引腳,X7R 材質);CLKVDD(1.2 V)需獨立低噪聲 LDO 供電,避免與數字電源耦合。

- 數字供電:DVDD(1.2 V),外接 1 μF+0.1 μF 去耦電容,與模擬電源單點接地,避免數字噪聲串擾。

- 布局原則 :

- 模擬信號:輸入(INx1P/M、INx2P/M)與時鐘(CLKP/M)采用差分布線,長度匹配(誤差 < 0.5 mm),遠離數字跡線;輸入路徑串聯 RC 抗混疊濾波器(推薦 50 Ω+4.7 nF,截止頻率 < FS/2)。

- 接地與隔離:模擬地(AGND)與數字地(DGND)單點連接,熱焊盤(Thermal Pad)連接 AGND;高壓 RF 電路與低壓數字電路間距≥8 mm,滿足爬電距離要求。

- JESD 鏈路:SerDes 輸出(DOUT0P/M-DOUT7P/M)采用差分布線,阻抗控制 50 Ω,長度匹配(誤差 < 1 mm),避免過孔與直角走線。

2. 模擬輸入設計

- RF 前端匹配 :

- 單端轉差分:采用 1:2 balun(如 Marki BAL-0009SMG)將單端 RF 信號轉為差分,balun 需滿足幅度不平衡 < 0.5 dB、相位不平衡 < 2°,輸出端 AC 耦合 100 pF 電容。

- 阻抗匹配:輸入差分阻抗配置為 50 Ω 或 100 Ω,通過 SPI 寫入寄存器 0x7B/8B(0x00=100 Ω,0x01=50 Ω),確保 RF 信號無反射。

- 噪聲抑制 :

3. 初始化與校準流程

- 上電序列 :

- 先加 DVDD(1.2 V),再加 AVDD12、CLKVDD(1.2 V),最后加 AVDD18(1.8 V)。

- 拉低 RESET 引腳(≥2048 個 CLK 周期),復位寄存器至默認值。

- 通過 SPI 配置平均模式、輸入端接、DDC 抽取比、JESD 參數(如 LMFS)。

- 校準啟動 :

- 配置校準模式(單次 / 連續),寄存器 0x46=0x03(連續校準)。

- 觸發校準:SPI 寫入 0x45=0x8A→0x0A(單次校準),或拉低 GPIO1(GPIO 觸發)。

- 校準完成:讀取寄存器 0x298,4 位 LSB=0x0E 表示校準成功。

-

變頻器

+關注

關注

256文章

7425瀏覽量

155846 -

adc

+關注

關注

100文章

7934瀏覽量

556760 -

模數轉換器

+關注

關注

26文章

4096瀏覽量

130230 -

噪聲頻譜

+關注

關注

0文章

28瀏覽量

2260

發布評論請先 登錄

ADC32RF52雙通道14位1.5GSPS射頻采樣數據轉換器數據表

ADC32RF44雙通道14位2.6GSPS模數轉換器數據表

ADC32RF42雙通道14位1.5GSPS模數轉換器數據表

ADC32RF45 14位3.0GSPS雙通道模數轉換器(ADC)數據表

ADC12DJ5200RF 具有雙通道 5.2 GSPS 或單通道 10.4 GSPS 的射頻采樣 12 位 ADC技術手冊

ADC32RF54雙通道 14 位高速 RF 采樣 ADC 技術總結

ADC32RF54雙通道 14 位高速 RF 采樣 ADC 技術總結

評論