來(lái)源:由半導(dǎo)體行業(yè)觀察編譯自semiengineering

研究人員專注于限制數(shù)據(jù)移動(dòng)以減少邊緣設(shè)備的功耗和延遲。在大眾媒體中,“人工智能”通常意味著在昂貴且耗電的數(shù)據(jù)中心運(yùn)行的大型語(yǔ)言模型。然而,對(duì)于許多應(yīng)用程序來(lái)說(shuō),在本地硬件上運(yùn)行的小型模型更為合適。自動(dòng)駕駛汽車需要實(shí)時(shí)響應(yīng),避免數(shù)據(jù)傳輸延遲。醫(yī)療和工業(yè)應(yīng)用通常依賴于無(wú)法與第三方共享的敏感數(shù)據(jù)。盡管邊緣人工智能應(yīng)用速度更快、更安全,但它們的計(jì)算資源卻非常有限。它們無(wú)法擁有 TB 級(jí)的內(nèi)存空間或幾乎無(wú)限的計(jì)算能力。對(duì)于數(shù)據(jù)中心來(lái)說(shuō),這些限制可能有些抽象,但卻對(duì)邊緣人工智能施加了嚴(yán)格的限制。在2025年IEEE國(guó)際內(nèi)存研討會(huì)的一篇受邀論文及其后續(xù)預(yù)印本中,蘇黎世聯(lián)邦理工學(xué)院計(jì)算機(jī)科學(xué)教授Onur Mutlu及其同事指出,在典型的移動(dòng)工作負(fù)載中,數(shù)據(jù)在內(nèi)存中的移動(dòng)占總能耗的62%,這一比例令人震驚。內(nèi)存是硬件資源的最大消耗者,而且遙遙領(lǐng)先,但內(nèi)存延遲往往是執(zhí)行時(shí)間的最大貢獻(xiàn)者。多年來(lái),器件規(guī)模的擴(kuò)大一直是降低功耗的關(guān)鍵,但現(xiàn)在卻使問(wèn)題更加嚴(yán)重。Mutlu 表示,規(guī)模龐大的 DRAM 穩(wěn)定性較差,需要更頻繁的刷新周期。大型內(nèi)存陣列的訪問(wèn)難度也更大,因?yàn)閹挼脑鲩L(zhǎng)速度不如內(nèi)存條本身的增長(zhǎng)速度快。內(nèi)存和近內(nèi)存計(jì)算提供了可能的解決方案。即使是商用的現(xiàn)成 DRAM,只要軟件基礎(chǔ)設(shè)施支持,也可以執(zhí)行原始的數(shù)據(jù)復(fù)制、初始化和按位邏輯運(yùn)算。

混合解決方案結(jié)合了RRAM和鐵電體

然而,DRAM刷新功率的問(wèn)題仍然存在。在神經(jīng)網(wǎng)絡(luò)模型中,訓(xùn)練和推理任務(wù)都會(huì)重復(fù)使用存儲(chǔ)的權(quán)重矩陣。然而,兩者的要求卻截然不同。正如 CEA-Leti 的 Michele Martemucci 及其同事所解釋的那樣,訓(xùn)練任務(wù)涉及對(duì)權(quán)重矩陣進(jìn)行多次小幅更新,使其逐漸收斂到穩(wěn)定值。這些任務(wù)需要具有高寫入耐久性和存儲(chǔ)精確值能力的內(nèi)存。相比之下,推理任務(wù)使用穩(wěn)定不變的權(quán)重矩陣,但可能會(huì)將其多次應(yīng)用于輸入數(shù)據(jù)。推理任務(wù)受益于具有高讀取耐久性的非易失性存儲(chǔ)器。在這兩種情況下,近內(nèi)存計(jì)算都需要與標(biāo)準(zhǔn) CMOS 邏輯工藝兼容的設(shè)備。RRAM 是一種簡(jiǎn)單的器件,依靠氧化層中形成的導(dǎo)電細(xì)絲來(lái)實(shí)現(xiàn)極高的讀取耐久性。通過(guò)精心設(shè)計(jì)的編程方案,它們可以存儲(chǔ)模擬值,從而減小存儲(chǔ)器陣列的大小。Martemucci 表示,RRAM 技術(shù)已經(jīng)足夠成熟,可以在邊緣推理場(chǎng)景中進(jìn)行商業(yè)部署。遺憾的是,RRAM 的寫入耐久性相對(duì)較低。隨著時(shí)間的推移,編程脈沖會(huì)模糊存儲(chǔ)值之間的電阻差異。設(shè)計(jì)人員通常使用傳統(tǒng)硬件訓(xùn)練模型,然后將預(yù)先計(jì)算的權(quán)重加載到 RRAM 陣列中。然而,在許多應(yīng)用中,邊緣設(shè)備需要具備“學(xué)習(xí)”能力。它要么需要根據(jù)用戶的特定需求進(jìn)行訓(xùn)練,要么需要修改模型以反映實(shí)際流程的變化。與此同時(shí),鐵電電容器支持非常快速的開(kāi)關(guān)和極高的寫入耐久性。它們可以輕松承受訓(xùn)練任務(wù)中遇到的頻繁寫入操作。然而,雖然存儲(chǔ)的值是非易失性的,但讀取操作卻具有破壞性。Martemucci 表示,這些設(shè)備不適合長(zhǎng)期存儲(chǔ)權(quán)重矩陣,也不適合需要頻繁讀取操作的推理任務(wù)。將鐵電晶體管集成到CMOS工藝中非常復(fù)雜,需要高溫工藝和額外的掩模層。鐵電電容器和隧道結(jié)則簡(jiǎn)單得多,這使得多個(gè)研究小組能夠?qū)RAM和鐵電結(jié)構(gòu)結(jié)合起來(lái)。例如,在今年的VLSI技術(shù)研討會(huì)上,SK海力士的研究人員展示了一種兼具電阻和鐵電開(kāi)關(guān)功能的混合鐵電隧道結(jié)(FTJ)。在傳統(tǒng)的FTJ中,頂部和底部電極之間的隧道勢(shì)壘取決于鐵電極性。SK海力士的器件將鐵電鉿鋯氧化物(HZO)層夾在兩個(gè)電極之間,鉭層用作氧空位儲(chǔ)存器。鉭層附近的導(dǎo)電細(xì)絲在器件頂部提供歐姆導(dǎo)電,從而降低了鐵電隧道勢(shì)壘的有效厚度。這些器件實(shí)現(xiàn)了精確的模擬乘法累加運(yùn)算,效率高達(dá)每瓦224.4萬(wàn)億次運(yùn)算(TOPS/W)。在另一種混合方法中,Martemucci 團(tuán)隊(duì)將摻雜硅的 HfO2電容器與鈦氧清除層結(jié)合到標(biāo)準(zhǔn) CMOS BEOL 工藝中。這些器件最初表現(xiàn)為鐵電電容器,其中一些器件接收一次性“喚醒”脈沖以穩(wěn)定鐵電響應(yīng)。同時(shí),電容器陣列的另一部分經(jīng)過(guò)一次性“成型”工藝,形成由氧空位構(gòu)成的導(dǎo)電細(xì)絲。鈦層充當(dāng)氧空位儲(chǔ)存器,防止細(xì)絲溶解。由此產(chǎn)生的憶阻器器件可以在高阻和低阻狀態(tài)之間切換。圖 1:金屬-鐵電-金屬疊層既可以用作 FeCAP,也可以用作憶阻器鐵電電容器充當(dāng)二進(jìn)制元件,存儲(chǔ)用于訓(xùn)練計(jì)算的高精度權(quán)重。憶阻器存儲(chǔ)的模擬權(quán)重精度足以應(yīng)對(duì)推理任務(wù)。在訓(xùn)練過(guò)程中,憶阻器陣列每完成100個(gè)輸入步驟后更新一次,而鐵電陣列則持續(xù)更新。訓(xùn)練此結(jié)構(gòu)進(jìn)行標(biāo)準(zhǔn)數(shù)字識(shí)別任務(wù)所需的寫入操作總數(shù)比憶阻器耐久性小17倍,比鐵電電容器耐久性小75倍,而能耗比持續(xù)更新憶阻器陣列所需能耗低38倍。

人工智能不僅僅是神經(jīng)網(wǎng)絡(luò)內(nèi)存計(jì)算不僅可以提高傳統(tǒng)神經(jīng)網(wǎng)絡(luò)計(jì)算的能效,還能促進(jìn)其他建模方法的發(fā)展。例如,許多計(jì)算難度高的問(wèn)題可以建模為伊辛玻璃,即一組連接的節(jié)點(diǎn)共同演化到最低能量狀態(tài)。[ ? 4] 現(xiàn)實(shí)世界中,這類問(wèn)題可能涉及數(shù)千甚至數(shù)百萬(wàn)個(gè)連接。解決伊辛玻璃問(wèn)題是量子計(jì)算最引人入勝的潛在應(yīng)用之一。更傳統(tǒng)的方法是,在去年的IEEE電子設(shè)備會(huì)議上,德克薩斯大學(xué)研究員Tanvir Haider Pantha和他的同事們提出構(gòu)建一個(gè)三維結(jié)構(gòu),將FeFET融入CMOS邏輯工藝的BEOL(后道工藝)。每個(gè)節(jié)點(diǎn)由四個(gè)交叉耦合的FeFET組成,可以存儲(chǔ)一個(gè)有符號(hào)的模擬值,該值映射到待解決問(wèn)題的伊辛耦合矩陣。每個(gè)節(jié)點(diǎn)的輸出是其相鄰節(jié)點(diǎn)的輸入,從而在整個(gè)網(wǎng)絡(luò)中建立振蕩,最終達(dá)到穩(wěn)定的最小能量配置。圖 2:四個(gè)交叉耦合雙柵 FeFET 構(gòu)成相變納米振蕩器。提出的伊辛玻璃模型每個(gè)節(jié)點(diǎn)使用其中一種結(jié)構(gòu)

內(nèi)存計(jì)算需要新框架傳統(tǒng)的 CPU 和 GPU 是通用設(shè)備。只需更改軟件即可應(yīng)用于許多不同的問(wèn)題。近內(nèi)存和內(nèi)存加速器目前與其預(yù)期任務(wù)密不可分。伊辛玻璃求解器、點(diǎn)云網(wǎng)絡(luò)和圖像識(shí)別網(wǎng)絡(luò)將以不同的方式處理數(shù)據(jù),需要不同的硬件設(shè)計(jì)。據(jù) Mutlu 稱,內(nèi)存計(jì)算的下一步將需要能夠重新映射內(nèi)存訪問(wèn)以滿足特定問(wèn)題要求的軟件框架。反過(guò)來(lái),這些框架將需要能夠獨(dú)立于外部?jī)?nèi)存控制器進(jìn)行自我管理的內(nèi)存硬件。

原文鏈接https://semiengineering.com/why-in-memory-computation-is-so-important-for-edge-ai/

-

芯片

+關(guān)注

關(guān)注

463文章

54009瀏覽量

465957 -

人工智能

+關(guān)注

關(guān)注

1817文章

50094瀏覽量

265302

發(fā)布評(píng)論請(qǐng)先 登錄

ISSCC 2026重磅:清華+華為+字節(jié)聯(lián)合發(fā)布存內(nèi)計(jì)算芯片,重塑推薦系統(tǒng)能效邊界

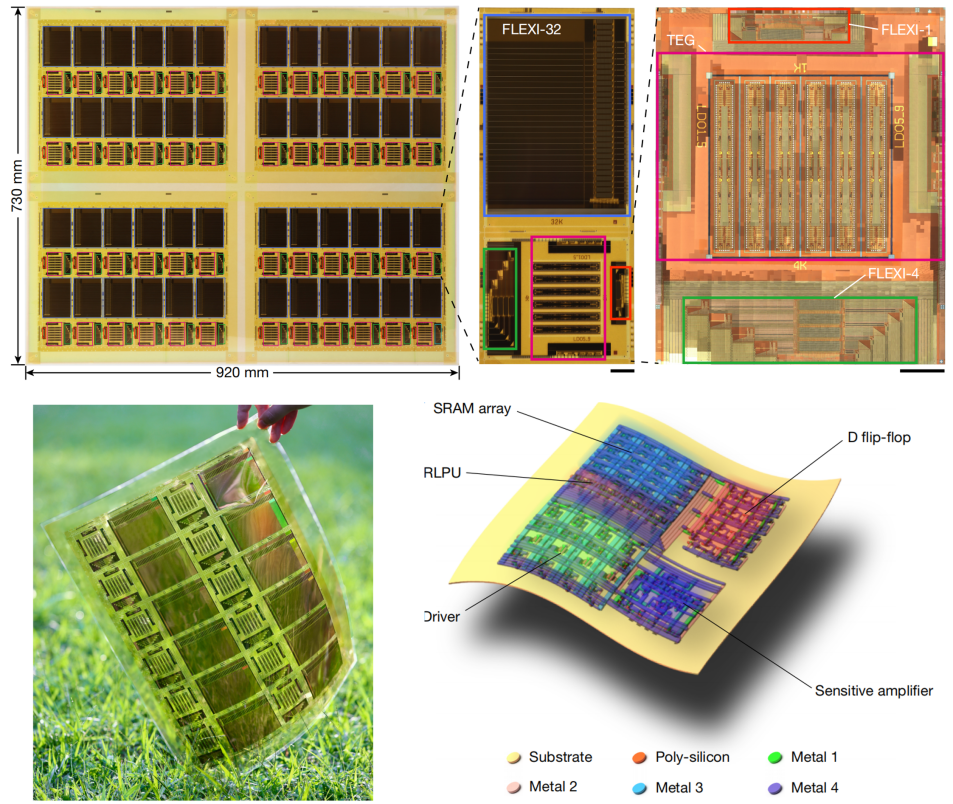

每片低至0.016美元!清華FLEXI芯片柔性+存內(nèi)計(jì)算雙突破

超低功耗智能語(yǔ)音芯片-AT690系列芯片

知存科技王紹迪:AI可穿戴需求爆發(fā),存算一體成主流AI芯片架構(gòu)

針對(duì)CW32芯片內(nèi)部flash能存用戶數(shù)據(jù)嗎?

知存科技榮獲2025半導(dǎo)體市場(chǎng)創(chuàng)新表現(xiàn)獎(jiǎng)

一文看懂“存算一體”

知存科技邀您相約第二十一屆全國(guó)容錯(cuò)計(jì)算學(xué)術(shù)會(huì)議

緩解高性能存算一體芯片IR-drop問(wèn)題的軟硬件協(xié)同設(shè)計(jì)

“算存平衡”有多重要?

得一微定義“AI存力芯片”,讓每比特?cái)?shù)據(jù)創(chuàng)造更多智能

第二屆知存科技杯華東高校存內(nèi)計(jì)算創(chuàng)新應(yīng)用大賽正式啟動(dòng)

知存科技創(chuàng)始人向北大、清華、協(xié)和醫(yī)學(xué)院捐贈(zèng)880萬(wàn)激勵(lì)創(chuàng)新

知存科技入選杭州AI“18羅漢”企業(yè)

得一微:AI存力芯片,重構(gòu)計(jì)算范式

存內(nèi)計(jì)算芯片,熱度大增

存內(nèi)計(jì)算芯片,熱度大增

評(píng)論