ADC3910Dx 和 ADC3910Sx 是系列超低功耗 10 位 125MSPS 高速單通道和雙通道模數(shù)轉(zhuǎn)換器。高速控制環(huán)路受益于僅 1 個(gè)時(shí)鐘周期的短延遲。ADC在125Msps時(shí)僅消耗92mW,功耗隨較低采樣率而變化。

該器件采用DDR、HDDR、SDR或串行CMOS接口輸出+1.8V至+3.3V的數(shù)據(jù),以滿足各種接收器要求。該器件使用具有可編程高閾值和低閾值、遲滯和事件計(jì)數(shù)器的數(shù)字比較器,通過(guò)每個(gè)通道的事件觸發(fā)中斷來(lái)實(shí)現(xiàn)模擬監(jiān)控功能。該器件是引腳兼容的ADC系列,具有8位和10位分辨率以及不同的速度等級(jí)。該器件采用 32 引腳 VQFN 封裝,支持 -40 至 +105°C 的工業(yè)溫度范圍。

*附件:adc3910d065.pdf

特性

- 采樣率高達(dá) 125MSPS

- 延遲:1 個(gè)時(shí)鐘周期

- 低功耗(2 通道):

- 125MSPS 時(shí)為 92mW

- 25MSPS 時(shí)為 59mW

- PD 模式下為 4mW

- 小尺寸:32-VQFN (4mm x 4mm)

- 單通道或雙通道ADC

- 雙數(shù)字比較器

- 參考:內(nèi)部或外部

- 無(wú)遺漏代碼,±1 LSB INL

- 緩沖、差分或單端輸入

- 輸入帶寬:150MHz (3dB)

- 1.8V單電源

- 可選的 3.3VIO 功能

- 工業(yè)溫度范圍:-40 至 105°C

- 片上數(shù)字濾波器(可選)

- 抽取 2、4、8、16

- 并行(SDR、DDR)和串行CMOS接口

- 頻譜性能 (fIN = 5MHz):

- 信噪比:61dBFS

- SFDR:65dBc

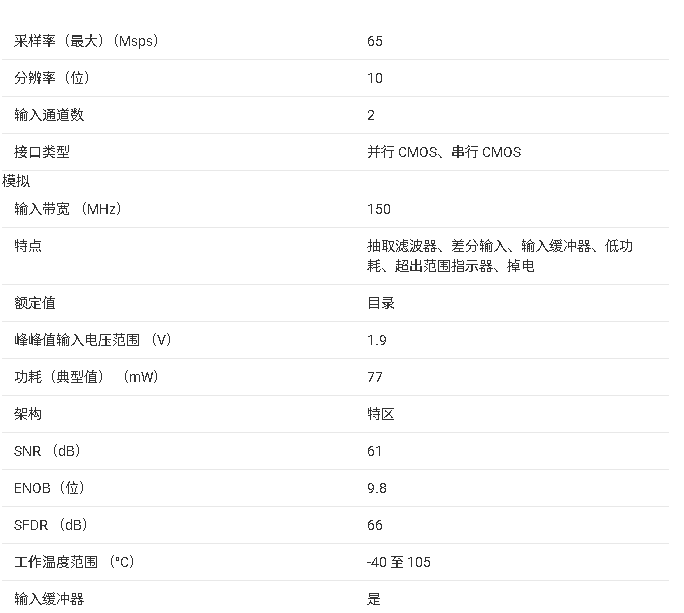

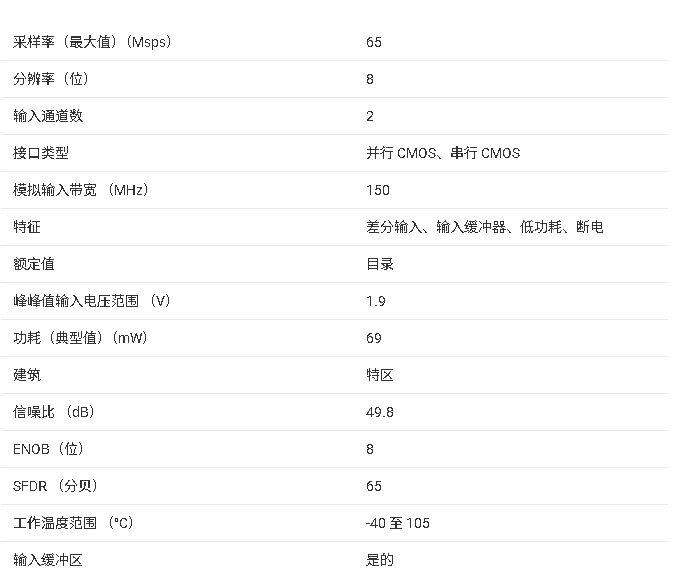

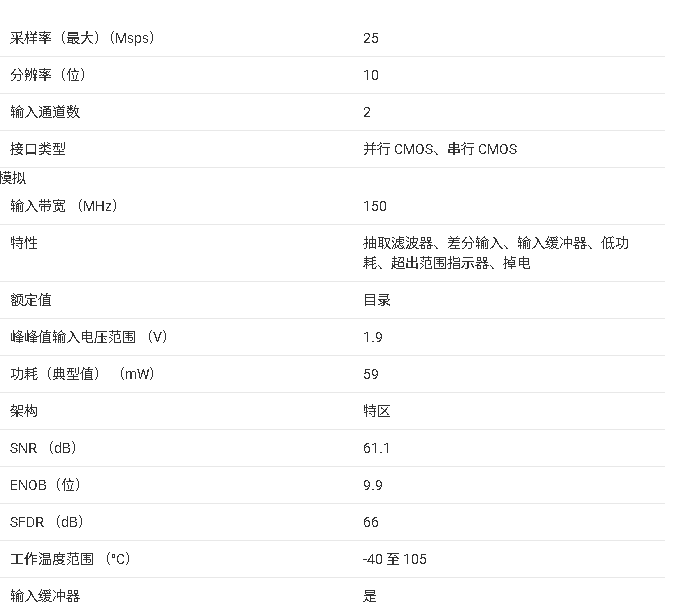

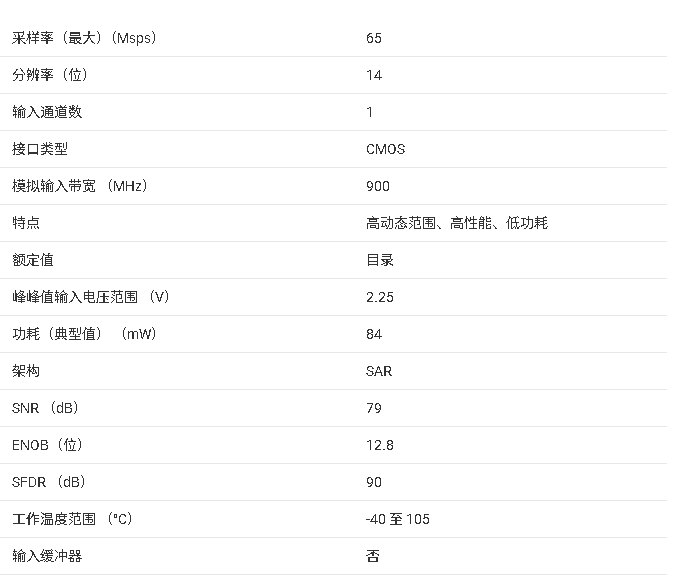

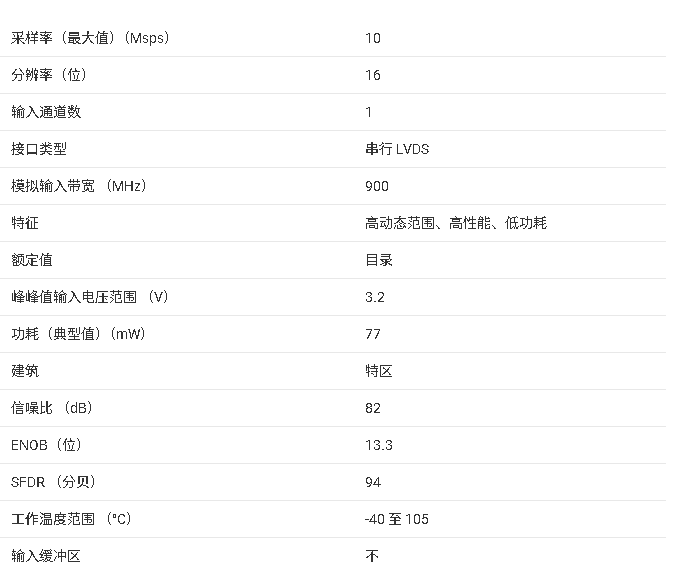

參數(shù)

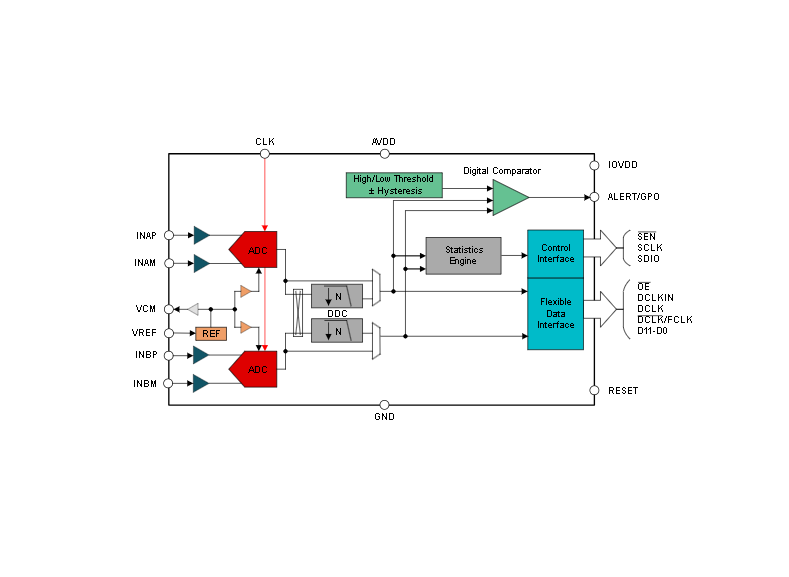

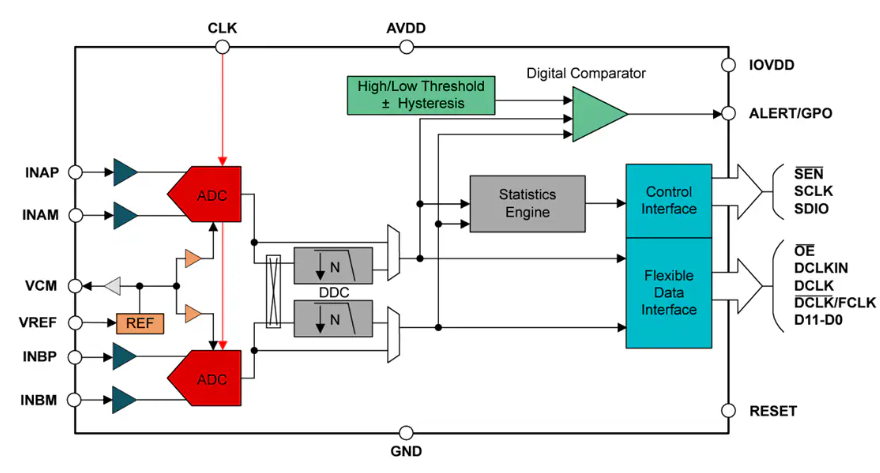

方框圖

ADC3910 系列是德州儀器(TI)推出的 10 位高速模數(shù)轉(zhuǎn)換器(ADC)家族,包含雙路(ADC3910Dx)與單路(ADC3910Sx)型號(hào),采樣率覆蓋 25MSPS 125MSPS,以低延遲(1 時(shí)鐘周期)、低功耗(雙路 125MSPS 時(shí) 97mW)、小尺寸(4mm×4mm 32 引腳 VQFN) 為核心優(yōu)勢(shì),集成輸入緩沖、數(shù)字下變頻器(DDC)、數(shù)字比較器、統(tǒng)計(jì)引擎等功能,適配無(wú)線電接收機(jī)、激光雷達(dá)(LiDAR)、低延遲控制環(huán)路、全球定位系統(tǒng)(GPS)及檢測(cè)設(shè)備等場(chǎng)景,工作溫度覆蓋 - 40°C +105°C 工業(yè)級(jí)范圍,兼具性能與靈活性。

一、核心特性與器件分類

1. 共性核心特性

- 高速低延遲采樣 :

- 采樣率覆蓋 25MSPS(D025/S025)、65MSPS(D065/S065)、125MSPS(D125/S125), 低延遲模式下數(shù)據(jù)輸出僅需 1 個(gè)時(shí)鐘周期 ,數(shù)字功能開(kāi)啟時(shí)延遲增至 5 個(gè)時(shí)鐘周期,適配實(shí)時(shí)控制場(chǎng)景;

- 輸入帶寬(-3dB)達(dá) 150MHz,支持差分 / 單端輸入,差分輸入滿量程(FSR)1.9Vpp,單端輸入 0.95Vpp,輸入共模電壓需匹配 VCM 引腳 1.25V 輸出(±50mV)。

- 高集成數(shù)字功能 :

- 數(shù)字下變頻器(DDC) :支持 2/4/8/16 倍實(shí)抽取,輸出數(shù)據(jù)率隨抽取比降低(如 125MSPS 抽取 16 倍后輸出 7.8125MSPS),阻帶抑制≥70dB,可放松外部抗混疊濾波器要求;

- 雙數(shù)字比較器 :每通道獨(dú)立可編程高 / 低閾值與滯回(0~4095LSB),支持電平比較(超閾值觸發(fā))與斜率比較(相鄰采樣差值觸發(fā)),通過(guò) ALERT 引腳輸出中斷,適配信號(hào)超限監(jiān)測(cè);

- 統(tǒng)計(jì)引擎 :實(shí)時(shí)統(tǒng)計(jì)指定窗口內(nèi)采樣數(shù)據(jù)(超閾值樣本計(jì)數(shù)、最小 / 最大值、求和、平方和),窗口大小可配置(256~256×21?樣本),支持存儲(chǔ)當(dāng)前及前 3 個(gè)窗口數(shù)據(jù),適配信號(hào)特征分析;

- 靈活數(shù)字接口 :支持并行(DDR/HDDR/SDR)與串行 CMOS 輸出,數(shù)據(jù)格式可選二進(jìn)制補(bǔ)碼(默認(rèn))或偏移二進(jìn)制,輸出 lanes 可配置(2/4/8 lane),IOVDD 支持 1.8V~3.3V 邏輯電平,適配不同 FPGA/MCU 接口需求。

- 低功耗與電源管理 :

- 分級(jí)功耗控制:雙路 125MSPS 時(shí)總功耗 97mW,25MSPS 時(shí) 59mW;單路 125MSPS 時(shí) 80mW,25MSPS 時(shí) 41mW;全局掉電模式功耗僅 4mW,支持模塊級(jí)掉電(如單獨(dú)關(guān)閉通道 A/B、參考源),平衡功耗與喚醒速度;

- 電源配置:AVDD(模擬 1.8V)與 IOVDD(數(shù)字 1.8V~3.3V)獨(dú)立供電,電源電流隨采樣率降低而減小(雙路 25MSPS 時(shí) AVDD 電流 29mA,125MSPS 時(shí) 39mA),電源抑制比(PSRR)在 1MHz 時(shí)達(dá) 40dB,抗電源噪聲能力強(qiáng)。

- 可靠性能指標(biāo) :

- DC 精度:10 位無(wú)失碼,微分非線性(DNL)典型 ±0.4LSB(最大 2.1LSB),積分非線性(INL)典型 ±0.5LSB(最大 2.1LSB),增益誤差(外部參考)±0.2% FSR,偏移誤差典型 ±1LSB,溫度漂移(偏移)僅 0.001LSB/°C;

- AC 性能:5MHz 輸入時(shí),信噪比(SNR)典型 60.6dBFS、無(wú)雜散動(dòng)態(tài)范圍(SFDR)典型 64dBc、總諧波失真(THD)典型 - 63dBc,通道隔離串?dāng)_典型 90dBc,滿足中高頻信號(hào)采樣需求;

- ESD 防護(hù):全引腳人體放電模型(HBM)±1000V、帶電器件模型(CDM)±500V,符合 JEDEC JESD22 標(biāo)準(zhǔn),工業(yè)環(huán)境可靠性高。

2. 器件分類(雙路 Dx vs 單路 Sx)

ADC3910 系列按通道數(shù)分為雙路(Dx)與單路(Sx),核心差異如下表:

| 參數(shù) | 雙路 ADC3910Dx(D025/D065/D125) | 單路 ADC3910Sx(S025/S065/S125) |

|---|---|---|

| 通道數(shù) | 2 路同步采樣 | 1 路采樣(通道 B 引腳懸空) |

| 模擬電源電流(AVDD) | 25MSPS 時(shí) 29mA,125MSPS 時(shí) 39mA | 25MSPS 時(shí) 19mA,125MSPS 時(shí) 25mA |

| 數(shù)字電源電流(IOVDD) | 25MSPS 時(shí) 9mA,125MSPS 時(shí) 18.5mA | 25MSPS 時(shí) 8mA,125MSPS 時(shí) 32mA |

| 功耗(典型值) | 125MSPS 時(shí) 97mW,25MSPS 時(shí) 59mW | 125MSPS 時(shí) 80mW,25MSPS 時(shí) 41mW |

| 特殊模式 | 支持交織模式(2 路交織采樣,采樣率翻倍至 2×CLK) | 不支持交織模式 |

| 引腳功能 | INBP/INBM 為通道 B 輸入 | INBP/INBM 為無(wú)連接(NC) |

二、封裝與引腳功能

1. 封裝規(guī)格

全系采用 4mm×4mm 32 引腳 VQFN(RSM 封裝) ,底部裸露熱焊盤(需與 PCB 接地焊盤連接以優(yōu)化散熱),熱阻參數(shù)如下,確保高功率下的散熱可靠性:

| 熱阻參數(shù) | 數(shù)值(°C/W) | 說(shuō)明 |

|---|---|---|

| 結(jié)到環(huán)境(RθJA) | 38.1 | 芯片結(jié)溫到環(huán)境溫度熱阻 |

| 結(jié)到板(RθJB) | 17.9 | 芯片結(jié)溫到 PCB 板熱阻 |

| 結(jié)到殼底(RθJC (bot)) | 7.8 | 芯片結(jié)溫到封裝底部熱阻 |

2. 關(guān)鍵引腳分類與功能

ADC3910 引腳按功能可分為模擬輸入、電源與地、時(shí)鐘、配置控制、數(shù)字接口五大類,核心引腳功能如下表:

| 引腳類別 | 關(guān)鍵引腳示例 | 類型 | 核心功能 |

|---|---|---|---|

| 模擬輸入 | AINAP/AINAM(通道 A)、INBP/INBM(通道 B) | 模擬輸入 | 差分 / 單端模擬輸入,差分模式下 AINAP/AINBM 為同相端,AINAM/INBM 為反相端;單端模式需將負(fù)端接 VCM |

| 電源與地 | AVDD(12/13 腳)、IOVDD(27 腳)、GND(熱焊盤)、DGND(28 腳) | 電源輸入 | AVDD(1.8V 模擬電源,供電 ADC 核心與輸入緩沖)、IOVDD(1.8V~3.3V 數(shù)字電源,供電接口與數(shù)字功能);GND 與 DGND 需單點(diǎn)連接,避免噪聲耦合 |

| 參考與共模 | VREF(17 腳)、VCM(7 腳) | 模擬 I/O | VREF:內(nèi)置 1.2V 參考(溫度漂移 102ppm/°C),外部參考時(shí)需并聯(lián) 10μF+0.1μF 去耦電容;VCM:輸出 1.25V 共模電壓,為模擬輸入提供 DC 偏置 |

| 時(shí)鐘與同步 | CLK(8 腳)、RESET(9 腳) | 數(shù)字輸入 | CLK:采樣時(shí)鐘(5MHz~125MHz,占空比 45%~55%),需低抖動(dòng)(典型 500fs RMS);RESET:硬件復(fù)位(高有效,內(nèi)置 60kΩ 下拉) |

| 配置控制 | SEN(16 腳)、SCLK(18 腳)、SDIO(19 腳) | 數(shù)字 I/O | SPI 配置接口:SEN 低有效(內(nèi)置 40kΩ 下拉),SCLK 時(shí)鐘(最高 20MHz),SDIO 雙向數(shù)據(jù),用于配置寄存器與讀取狀態(tài) |

| 數(shù)字接口 | D0~D11(數(shù)據(jù)輸出)、DCLK(30 腳)、DCLK/FCLK(29 腳) | 數(shù)字輸出 | D0~D11:并行數(shù)據(jù)輸出(10 位有效,高位對(duì)齊);DCLK:數(shù)據(jù)時(shí)鐘(DDR 模式下 125MSPS 時(shí) 250MHz);DCLK/FCLK:默認(rèn)反相 DCLK,可配置為幀時(shí)鐘 |

| 中斷與狀態(tài) | ALERT(20 腳) | 數(shù)字輸出 | 比較器 / 統(tǒng)計(jì)引擎中斷輸出,可配置為推挽 / 開(kāi)漏模式,默認(rèn)監(jiān)測(cè) ADC 過(guò)范圍(OVR)事件 |

三、電氣規(guī)格與性能指標(biāo)

1. 電源與功耗(典型值,TA=25°C,AVDD=IOVDD=1.8V)

| 型號(hào) | 采樣率 | 通道數(shù) | AVDD 電流 | IOVDD 電流 | 總功耗 |

|---|---|---|---|---|---|

| ADC3910D025 | 25MSPS | 2 | 29mA | 9mA | 59mW |

| ADC3910S025 | 25MSPS | 1 | 19mA | 8mA | 41mW |

| ADC3910D065 | 65MSPS | 2 | 33mA | 18mA | 76mW |

| ADC3910S065 | 65MSPS | 1 | 22mA | 19mA | 58mW |

| ADC3910D125 | 125MSPS | 2 | 39mA | 18.5mA | 97mW |

| ADC3910S125 | 125MSPS | 1 | 25mA | 32mA | 80mW |

| 全局掉電模式 | - | - | - | - | 4mW |

2. DC 精度指標(biāo)(TA=25°C,差分輸入,內(nèi)部參考)

| 參數(shù) | 25MSPS 典型值 | 65MSPS 典型值 | 125MSPS 典型值 | 單位 |

|---|---|---|---|---|

| 微分非線性(DNL) | ±0.4 | ±0.4 | ±0.4 | LSB |

| 積分非線性(INL) | ±0.5 | ±0.5 | ±0.5 | LSB |

| 偏移誤差(VOS_ERR) | ±1 | ±1 | ±1 | LSB |

| 增益誤差(外部參考) | ±0.2 | ±0.2 | ±0.3 | %FSR |

| 增益誤差(內(nèi)部參考) | ±0.8 | ±0.8 | ±0.8 | %FSR |

| 偏移漂移(VOS_DRIFT) | 0.001 | 0.001 | 0.001 | LSB/°C |

3. AC 性能指標(biāo)(TA=25°C,fIN=5MHz,AIN=-1dBFS,差分輸入)

| 參數(shù) | 25MSPS 典型值 | 65MSPS 典型值 | 125MSPS 典型值 | 單位 |

|---|---|---|---|---|

| 信噪比(SNR) | 60.7 | 61.1 | 60.6 | dBFS |

| 無(wú)雜散動(dòng)態(tài)范圍(SFDR) | 66 | 65 | 64 | dBFS |

| 總諧波失真(THD) | -65 | -64 | -63 | dBc |

| 噪聲譜密度(NSD) | -132 | -135.9 | -138.8 | dBFS/Hz |

| 有效位數(shù)(ENOB) | 9.9 | 9.9 | 9.8 | Bit |

| 通道串?dāng)_(XTALK) | 97 | 102 | 90 | dBFS |

| 三階互調(diào)失真(IMD3) | -98 | -94 | -84 | dBc |

四、核心功能與工作模式

1. 模擬前端與采樣配置

- 輸入模式 :

- 差分模式:默認(rèn)配置,輸入信號(hào)共模電壓需匹配 VCM(1.25V),AC 耦合時(shí)需通過(guò) 1kΩ 電阻網(wǎng)絡(luò)拉至 VCM;

- 單端模式:通過(guò)寄存器(0x30B,SE_EN=1)啟用,負(fù)端接 VCM,此時(shí) SNR 降低 3dB,輸入滿量程 0.95Vpp。

- 交織模式(僅雙路 Dx) :

- 兩通道 180° 相位交織采樣,采樣率翻倍(如 CLK=62.5MHz 時(shí)輸出 125MSPS),需通過(guò)寄存器(0x84)配置增益 / 偏移校準(zhǔn),抵消通道失配;

- 啟用后禁用 DDC、統(tǒng)計(jì)引擎與比較器,僅支持并行輸出接口。

- 參考源配置 :

- 內(nèi)部參考:默認(rèn)模式,VREF 引腳接 GND,增益漂移 102ppm/°C;

- 外部參考:寄存器(0x30B,EXT_REF=1)啟用,VREF 引腳接 1.2V 參考(如 TI REF7040),需并聯(lián) 10μF+0.1μF 去耦電容,增益漂移降至 - 35ppm/°C。

2. 數(shù)字功能詳解

(1)數(shù)字下變頻器(DDC)

- 抽取配置 :通過(guò)寄存器(0x200)選擇抽取比(2/4/8/16),抽取后輸出帶寬 = 0.8× 采樣率 /(2× 抽取比),如 125MSPS 抽取 16 倍后帶寬 3.125MHz;

- 數(shù)據(jù)選擇 :支持選擇通道 A/B 原始數(shù)據(jù)或校正后數(shù)據(jù)輸入 DDC,通過(guò)寄存器(0x200/0x203)配置;

- 過(guò)范圍監(jiān)測(cè) :DDC 過(guò)范圍事件可觸發(fā) ALERT,通過(guò)寄存器(0x205/0x206)啟用,過(guò)范圍信號(hào)持續(xù) 1 個(gè)輸出時(shí)鐘周期。

(2)數(shù)字比較器

- 比較模式 :

- 電平比較:當(dāng)前采樣值>高閾值 - 滯回 或 <低閾值 + 滯回時(shí)觸發(fā);

- 斜率比較:當(dāng)前采樣值 - 前一采樣值>高閾值 或 <低閾值時(shí)觸發(fā),需將滯回置 0;

- 閾值配置 :高閾值(COMP_THRESHOLD_HI,0xC8

0xCB)、低閾值(COMP_THRESHOLD_LO,0xCC0xCF)、滯回(COMP_HYSTERESIS,0xD0~0xD3),均為 12 位寄存器; - 觸發(fā)邏輯 :支持事件觸發(fā)(單次超閾值觸發(fā) ALERT)或窗口觸發(fā)(指定窗口內(nèi)超閾值次數(shù)達(dá)閾值觸發(fā)),窗口大小通過(guò)寄存器(0x1EA)配置。

(3)統(tǒng)計(jì)引擎

- 統(tǒng)計(jì)項(xiàng) :樣本計(jì)數(shù)(超閾值樣本數(shù))、極值(最小 / 最大值)、求和、平方和(用于功率計(jì)算),支持存儲(chǔ)當(dāng)前窗口(N)及前 3 個(gè)窗口(N-1~N-3)數(shù)據(jù);

- 窗口配置 :通過(guò)寄存器(0x1A0

0x1A3)設(shè)置窗口大小(256256×21?樣本),支持連續(xù)采集或單次采集(1SHOT_CHx 寄存器); - 數(shù)據(jù)讀取 :統(tǒng)計(jì)結(jié)果存儲(chǔ)于專用寄存器(0xE4~0x195),如最大 / 最小值、求和、平方和等,可通過(guò) SPI 讀取。

(4)數(shù)字接口模式

- 并行模式 :

- DDR(雙沿采樣):默認(rèn)模式,DCLK 上升沿輸出通道 A 數(shù)據(jù),下降沿輸出通道 B 數(shù)據(jù),125MSPS 時(shí) DCLK=250MHz;

- HDDR(分 lane 輸出):通道 A/B 數(shù)據(jù)分不同 lane 輸出,需配置 HDDR_EN(0x98);

- SDR(單沿采樣):僅上升沿輸出,需雙倍 DCLK 頻率(125MSPS 時(shí) DCLK=500MHz)。

- 串行模式 :

- 支持 2/4/8/16 倍串行化,減少輸出 lane 數(shù)(如 125MSPS 8 倍串行化后用 2 lane 輸出),通過(guò)寄存器(0xA6,SERIALIZATION)配置;

- 幀時(shí)鐘(FCLK):可通過(guò)寄存器(0x88)啟用,用于同步多器件數(shù)據(jù)輸出。

3. 低功耗與復(fù)位模式

- 分級(jí)掉電 :

- 全局掉電:通過(guò) OEN/PD 引腳(高有效)或寄存器(0x97)觸發(fā),掉電后 AVDD 電流典型 2mA,喚醒時(shí)間(內(nèi)部參考)30μs;

- 模塊掉電:可單獨(dú)關(guān)閉通道 A/B(0x8C,CHA_PDN/CHB_PDN)、參考源(MASK_REF)、DLL(MASK_DLL),關(guān)閉單通道可降低 12mA AVDD 電流。

- 復(fù)位機(jī)制 :

- 硬件復(fù)位:RESET 引腳高有效,復(fù)位后寄存器恢復(fù)默認(rèn)值,需等待 200000 個(gè) CLK 周期后配置;

- 軟件復(fù)位:通過(guò)寄存器(0x00,RESET 位)觸發(fā),自清除,無(wú)需外部引腳操作。

五、寄存器配置

1. 核心寄存器功能(部分關(guān)鍵寄存器)

| 地址 | 寄存器名稱 | 核心功能 |

|---|---|---|

| 0x00 | RESET | 軟件復(fù)位,置 1 后自動(dòng)清 0,復(fù)位所有寄存器 |

| 0x84 | INTERLEAVE | 雙路器件交織模式使能(bit2=1),僅 Dx 系列支持 |

| 0x98 | INTERFACE_CFG_1 | 接口模式配置:HDDR 使能(bit5)、SDR 使能(bit4)、ALERT 引腳驅(qū)動(dòng)強(qiáng)度(bit3~0) |

| 0xA6 | INTERFACE_CFG_4 | 串行化因子(bit4~1)、DDR 數(shù)據(jù)輸出順序(bit5)、測(cè)試模式使能(bit0) |

| 0x200 | DDC_CFG_1 | DDC 抽取比(bit2 |

| 0xC8~0xD3 | COMP 系列寄存器 | 比較器高 / 低閾值、滯回、斜率比較使能 |

| 0x1A0~0x1A4 | STATS 系列寄存器 | 統(tǒng)計(jì)窗口大小、統(tǒng)計(jì)引擎使能、單次采集使能 |

| 0x30B | DEV_CFG_4 | 參考源選擇(bit6)、單端輸入使能(bit5)、分辨率配置(bit0=1 為 8 位) |

2. SPI 配置流程

- 寫操作 :

- SEN 拉低,SCLK 上升沿 latch 16 位數(shù)據(jù)(bit15=0 為寫,bit14~0 為地址 + 數(shù)據(jù));

- 每 16 個(gè) SCLK 周期完成 1 個(gè)寄存器寫入,多寄存器寫入可連續(xù)發(fā)送;

- SEN 拉高,完成寫操作。

- 讀操作 :

- SEN 拉低,發(fā)送 16 位讀命令(bit15=1,bit14~0 為寄存器地址);

- 等待 8 個(gè) SCLK 周期,SDIO 輸出寄存器數(shù)據(jù);

- SEN 拉高,完成讀操作。

- 初始化流程 :

- 上電后等待 2ms(內(nèi)部基準(zhǔn)穩(wěn)定);

- 硬件復(fù)位(RESET 引腳高電平≥10ns),釋放后等待 200000 個(gè) CLK 周期;

- 通過(guò) SPI 配置參考源、接口模式、數(shù)字功能(如 DDC、比較器)。

六、應(yīng)用設(shè)計(jì)建議

1. 典型應(yīng)用場(chǎng)景

- 無(wú)線電接收機(jī) :150MHz 帶寬 + 64dBc SFDR,適配中高頻信號(hào)采樣,DDC 功能可將信號(hào)下變頻至基帶,減少 FPGA 算力消耗;

- LiDAR 系統(tǒng) :125MSPS 采樣率 + 低延遲(1 時(shí)鐘周期),快速捕獲激光回波信號(hào),統(tǒng)計(jì)引擎可實(shí)時(shí)分析信號(hào)極值與能量;

- 低延遲控制環(huán)路 :1 時(shí)鐘周期延遲 + 90dBc 串?dāng)_,適配工業(yè)電機(jī)控制、機(jī)器人定位等實(shí)時(shí)反饋場(chǎng)景;

- 源測(cè)量單元(SMU) :低偏移漂移(0.001LSB/°C)+ 高 SNR,支持微弱電流(pA 級(jí))測(cè)量,適配半導(dǎo)體器件測(cè)試。

2. 硬件設(shè)計(jì)建議

(1)電源與去耦

- AVDD 與 IOVDD 獨(dú)立供電,AVDD 推薦用 LDO(如 TPS7A4701)二次穩(wěn)壓,降低開(kāi)關(guān)噪聲;

- 關(guān)鍵電源引腳去耦:AVDD 與 GND 之間并聯(lián) 10μF(X7R,0603)+0.1μF(陶瓷),距離引腳<2mm;VREF 引腳并聯(lián) 10μF+0.1μF 去耦電容;

- 地平面設(shè)計(jì):模擬地(GND)與數(shù)字地(DGND)僅在熱焊盤處單點(diǎn)連接,避免數(shù)字噪聲耦合至模擬區(qū)。

(2)PCB 布局

- 模擬區(qū)(AINx、VREF、VCM)與數(shù)字區(qū)(D0~D11、DCLK)嚴(yán)格分區(qū),模擬信號(hào)線采用差分布線,阻抗控制 50Ω,長(zhǎng)度匹配 ±0.5mm;

- 采樣時(shí)鐘(CLK):短路徑布線,串聯(lián) 50Ω 匹配電阻,差分對(duì)長(zhǎng)度差<1mm,避免時(shí)鐘抖動(dòng)導(dǎo)致 SNR 下降;

- 熱焊盤:裸露熱焊盤需與 PCB 接地銅皮充分焊接,通過(guò) 4 個(gè)過(guò)孔連接至內(nèi)層地,優(yōu)化散熱(RθJC (bot)=7.8°C/W)。

(3)輸入保護(hù)與匹配

- 模擬輸入串聯(lián) 10Ω 限流電阻 + 22pF 濾波電容,防止浪涌電流損壞輸入緩沖;

- 共模匹配:AC 耦合時(shí),通過(guò) 1kΩ 電阻將輸入拉至 VCM(1.25V),避免通道失配;

- 時(shí)鐘輸入:推薦使用差分時(shí)鐘源(如 TI CDCE6214),單端時(shí)鐘需通過(guò)電阻分壓將共模電壓拉至 0.9V(CLK 引腳最佳共模)。

七、訂購(gòu)信息與可靠性

1. 訂購(gòu)型號(hào)參數(shù)(部分關(guān)鍵型號(hào))

| 訂購(gòu)型號(hào) | 通道數(shù) | 采樣率 | 封裝 | 溫度范圍 | RoHS 合規(guī) | 包裝規(guī)格 |

|---|---|---|---|---|---|---|

| ADC3910D065IRSMR | 2 | 65MSPS | 32 引腳 VQFN | -40°C~+105°C | 是 | 3000 顆 / 大卷帶 |

| ADC3910S065IRSMR | 1 | 65MSPS | 32 引腳 VQFN | -40°C~+105°C | 是 | 3000 顆 / 大卷帶 |

| ADC3910D125IRSMR | 2 | 125MSPS | 32 引腳 VQFN | -40°C~+105°C | 是 | 3000 顆 / 大卷帶 |

| ADC3910S125IRSMR | 1 | 125MSPS | 32 引腳 VQFN | -40°C~+105°C | 是 | 3000 顆 / 大卷帶 |

2. 可靠性與防護(hù)

- ESD 防護(hù) :全引腳 HBM±1000V、CDM±500V,符合 JEDEC JESD22 標(biāo)準(zhǔn);

- 質(zhì)量保證 :量產(chǎn)型號(hào)通過(guò)溫度循環(huán)(-40°C~+105°C)、濕度偏壓(85°C/85% RH)、電應(yīng)力測(cè)試,MTBF(平均無(wú)故障時(shí)間)達(dá) 10?小時(shí)以上;

- 焊接要求 :MSL 等級(jí) 1(無(wú)濕度敏感限制),峰值回流溫度 260°C,焊接時(shí)需遵循 ESD 防護(hù)流程。

-

CMOS

+關(guān)注

關(guān)注

58文章

6217瀏覽量

242820 -

接收器

+關(guān)注

關(guān)注

15文章

2644瀏覽量

77119 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

4013瀏覽量

130100 -

ADC

+關(guān)注

關(guān)注

0文章

226瀏覽量

16845

發(fā)布評(píng)論請(qǐng)先 登錄

ADC10D1000/ADC10D1500低功耗ADC數(shù)據(jù)表

ADS52J90 10位、12位、14位多通道低功耗高速ADC數(shù)據(jù)表

ADC10DL065低功耗、單芯片CMOS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADS52J91 10位、12位、14位多通道低功耗高速ADC數(shù)據(jù)表

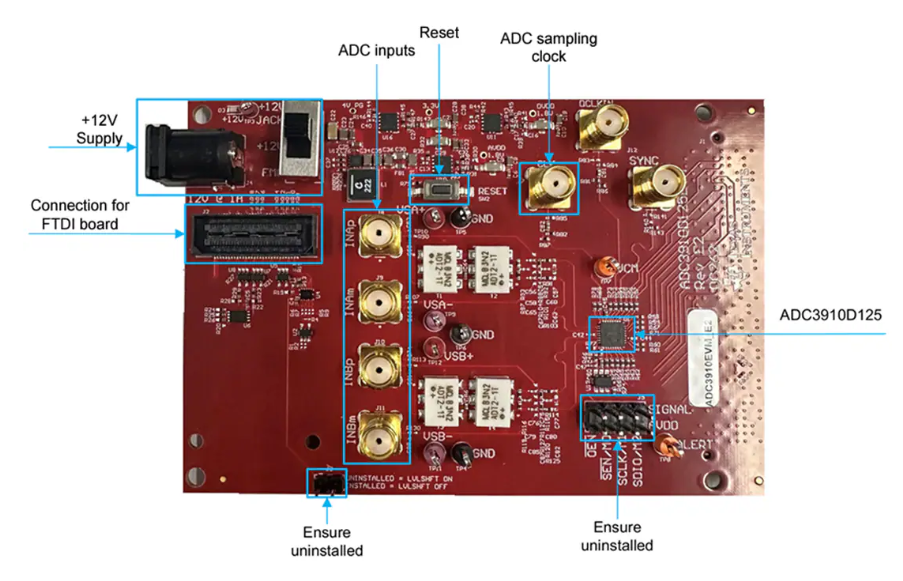

ADC3910D125評(píng)估模塊

德州儀器ADC3910系列:高性能低功耗10位125MSPS ADC技術(shù)解析

Texas Instruments ADC3910D125EVM評(píng)估模塊技術(shù)解析

ADC3908D065數(shù)據(jù)手冊(cè)總結(jié)

ADC3910D065 10 位高速低功耗 ADC 技術(shù)文檔總結(jié)

ADC3910D065 10 位高速低功耗 ADC 技術(shù)文檔總結(jié)

評(píng)論