ADS117L14(四通道)和ADS117L18(八進(jìn)制)是 16 位、三角形 Σ (ΔΣ)、模數(shù)轉(zhuǎn)換器 (ADC)。這些器件提供4個(gè)或8個(gè)通道的同步采樣,數(shù)據(jù)速率高達(dá)512kSPS(寬帶濾波器模式)和1365kSPS(低延遲濾波器模式)。24位ADS127L14(四通道)和ADS127L18(八進(jìn)制)ADC是引腳兼容器件,可提高分辨率。

*附件:ads117l14.pdf

特性

- 同時(shí)測(cè)量四個(gè)或八個(gè)通道

- 寬帶濾波器模式:高達(dá) 512kSPS

- 線性相位響應(yīng)

- ±0.0004dB通帶紋波

- 106dB阻帶衰減

- 低延遲濾波模式:高達(dá) 1365kSPS

- 3.9μs 轉(zhuǎn)換延遲

- 功率可擴(kuò)展速度模式:

- 最大轉(zhuǎn)速:21mW/ch (512kSPS/1365kSPS)

- 高速:16mW/ch (400kSPS/1067kSPS)

- 中速:9mW/ch (200kSPS/533kSPS)

- 低速:3mW/ch (50kSPS/133kSPS)

- 高精度:

- 200kSPS時(shí)的SNR:97.7dB(典型值)

- 總諧波差:–115dB(典型值)

- INL:0.5LSB(典型值)

- 失調(diào)漂移:60nV/°C(典型值)

- 增益漂移:1ppm/°C FSR(典型值)

- 預(yù)充電緩沖信號(hào)輸入

- 雙極或單極電源作

- ±VREF 或 ±2VREF 輸入范圍

- 可通過(guò)引腳設(shè)置或 SPI 進(jìn)行編程

- 用于輸出數(shù)據(jù)的幀同步端口

- 內(nèi)部或外部時(shí)鐘作

- 模擬電源電壓:2.85V 至 5.5V

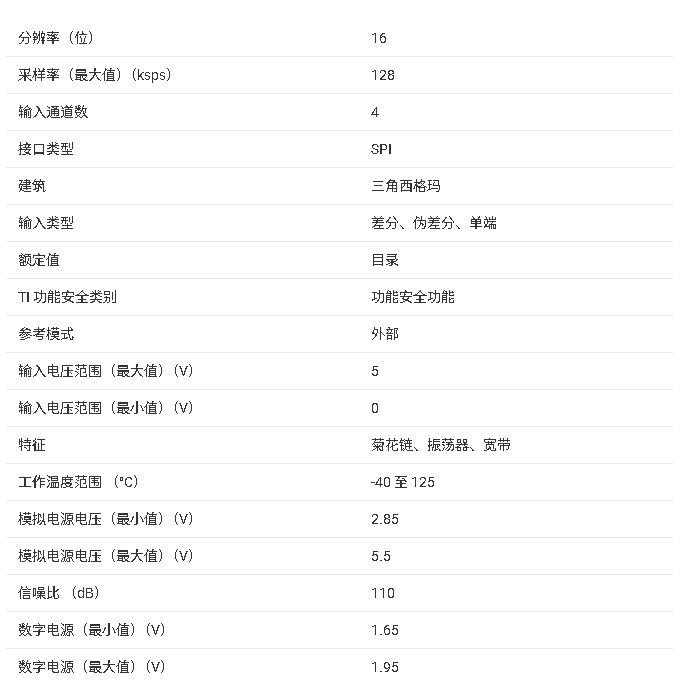

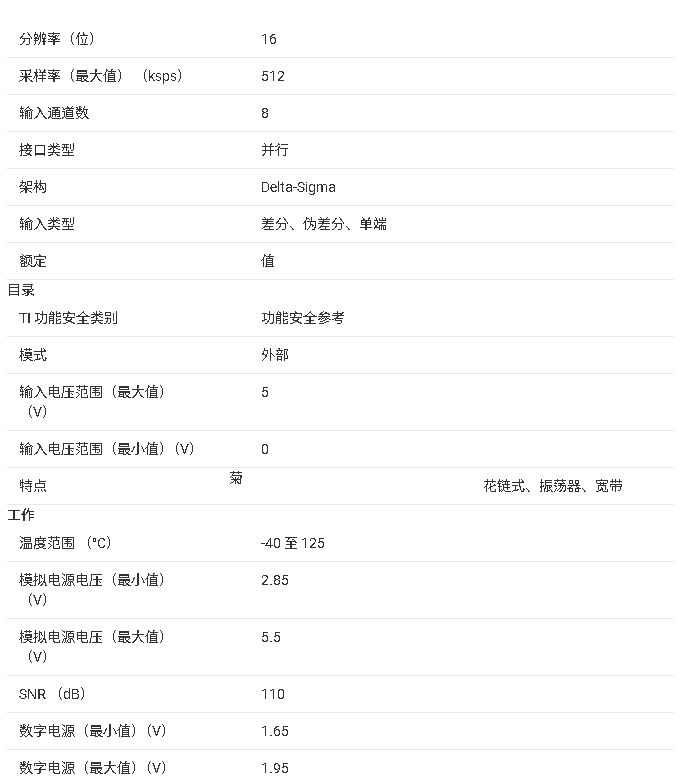

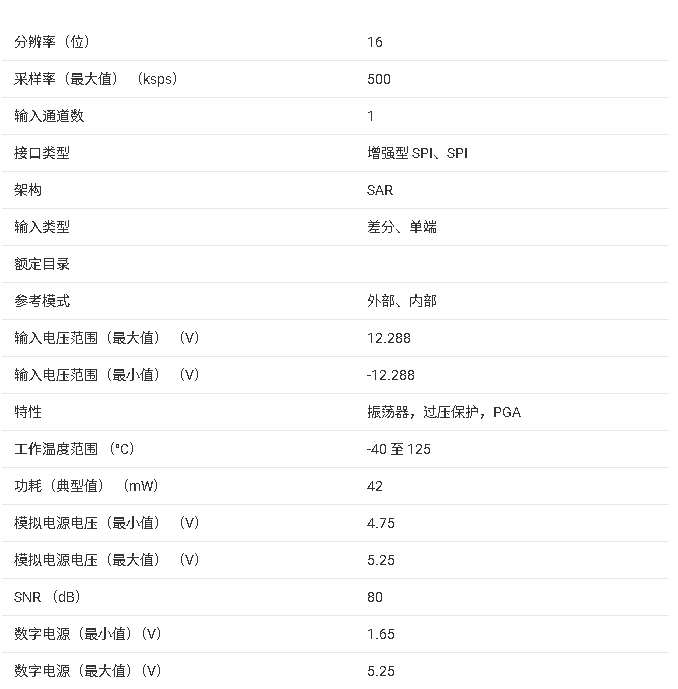

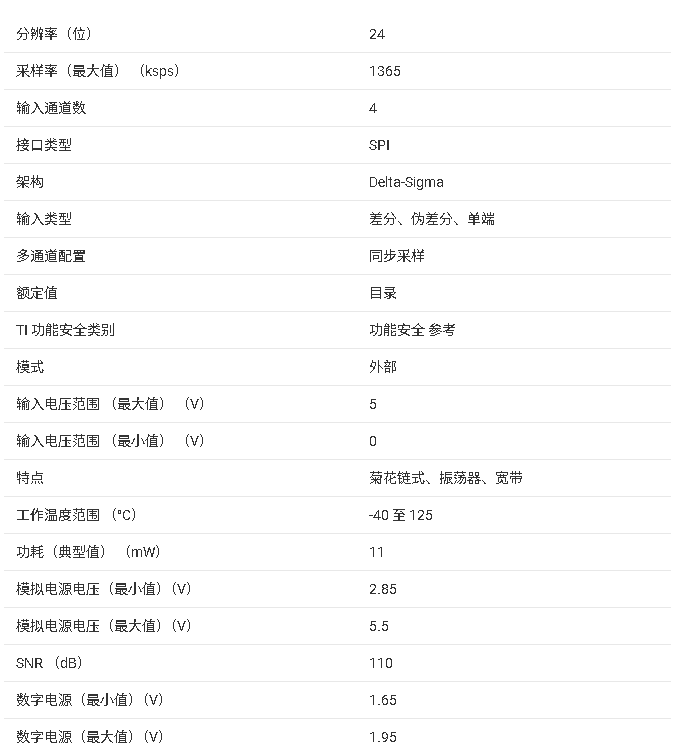

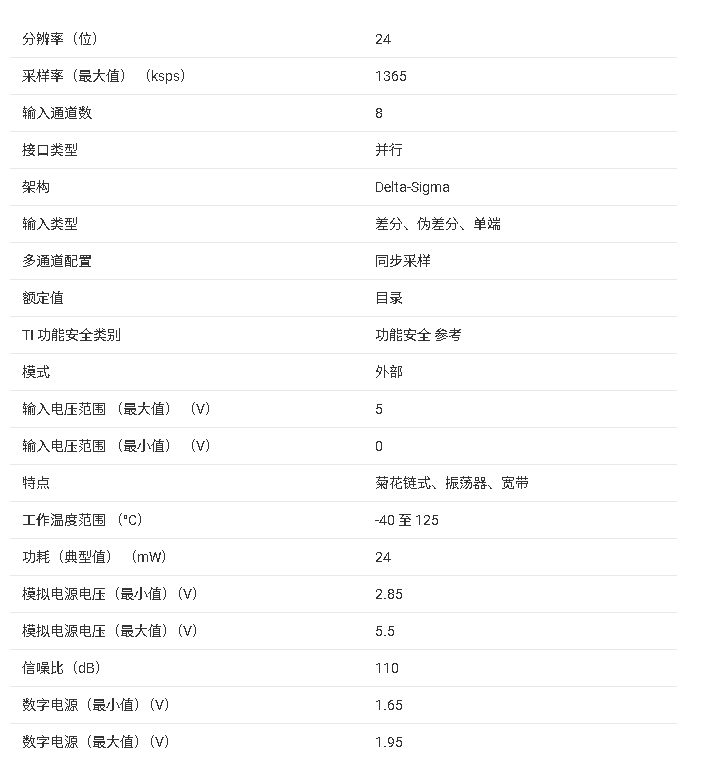

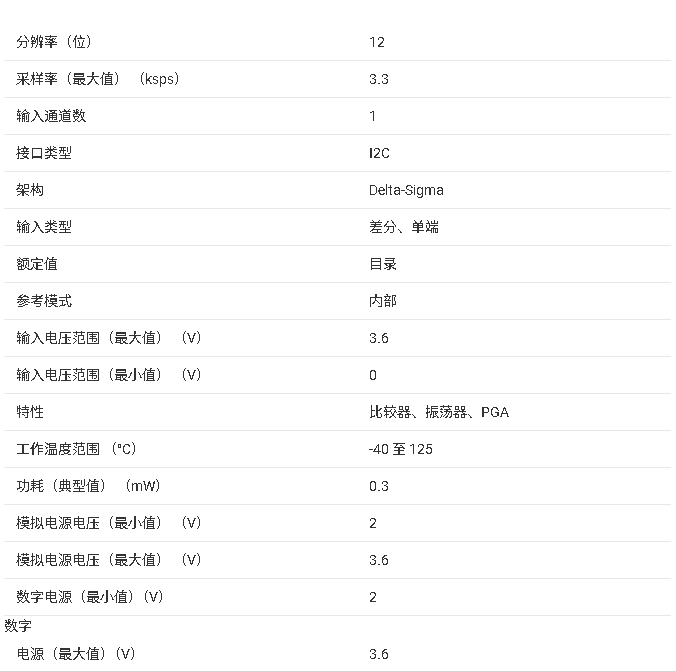

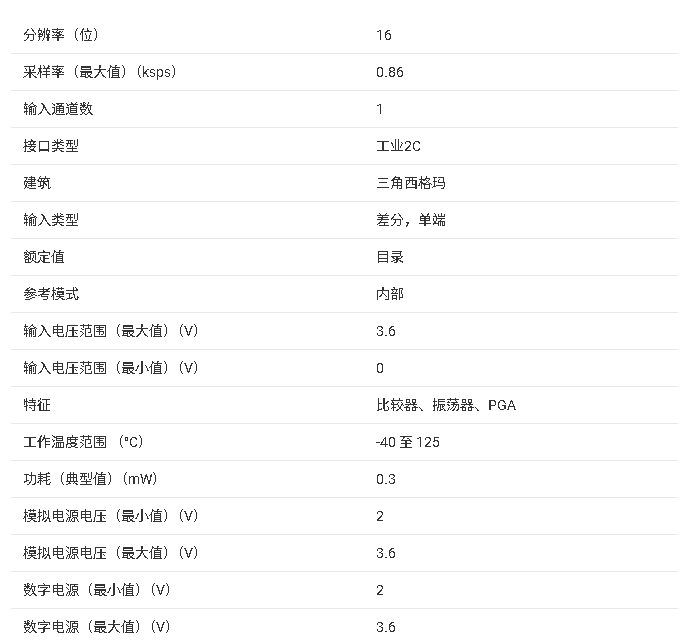

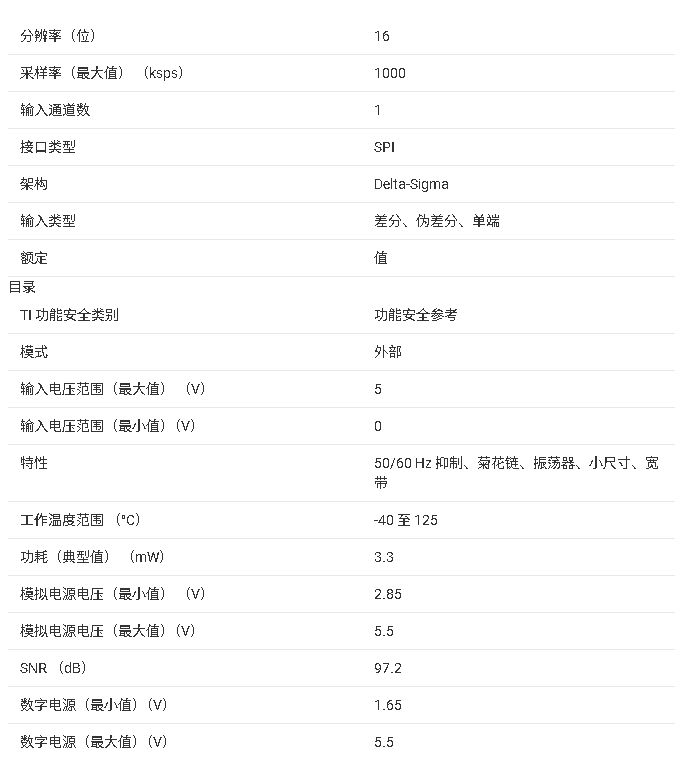

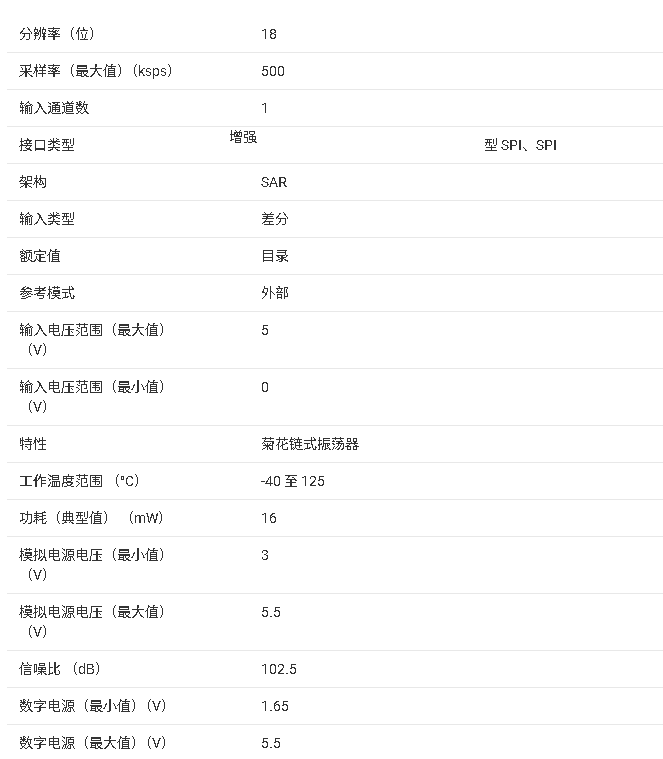

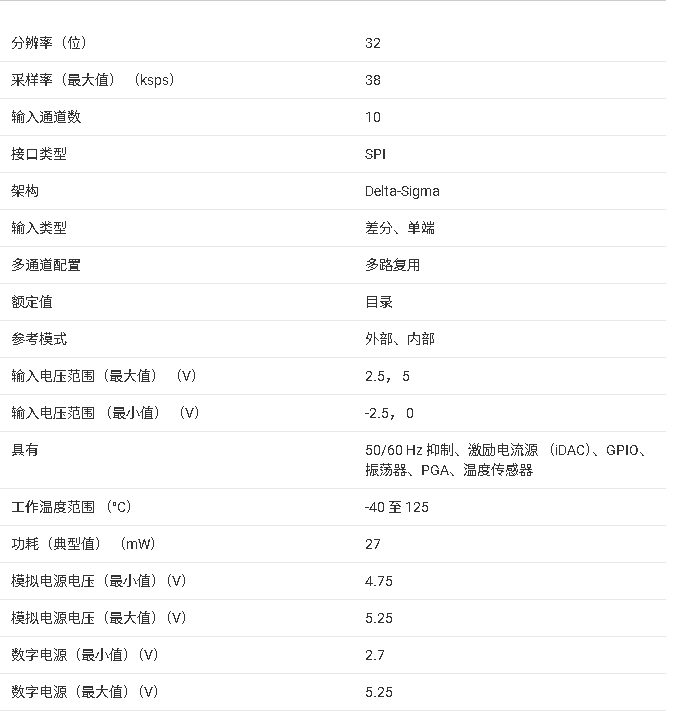

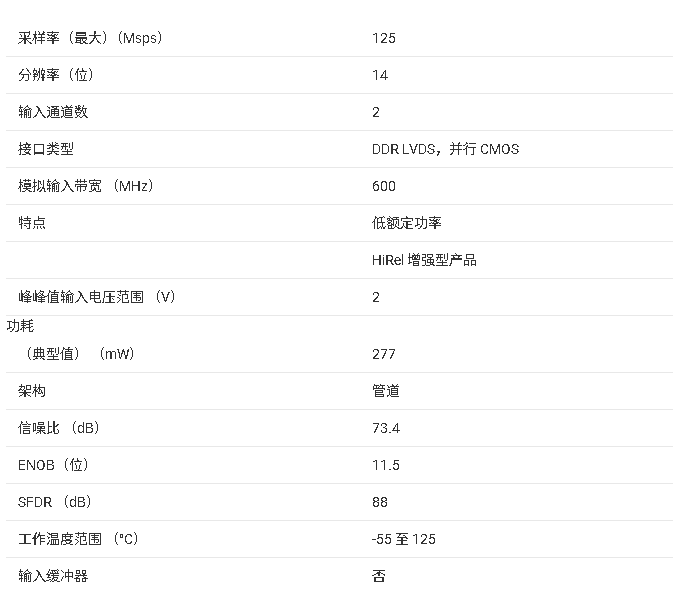

參數(shù)

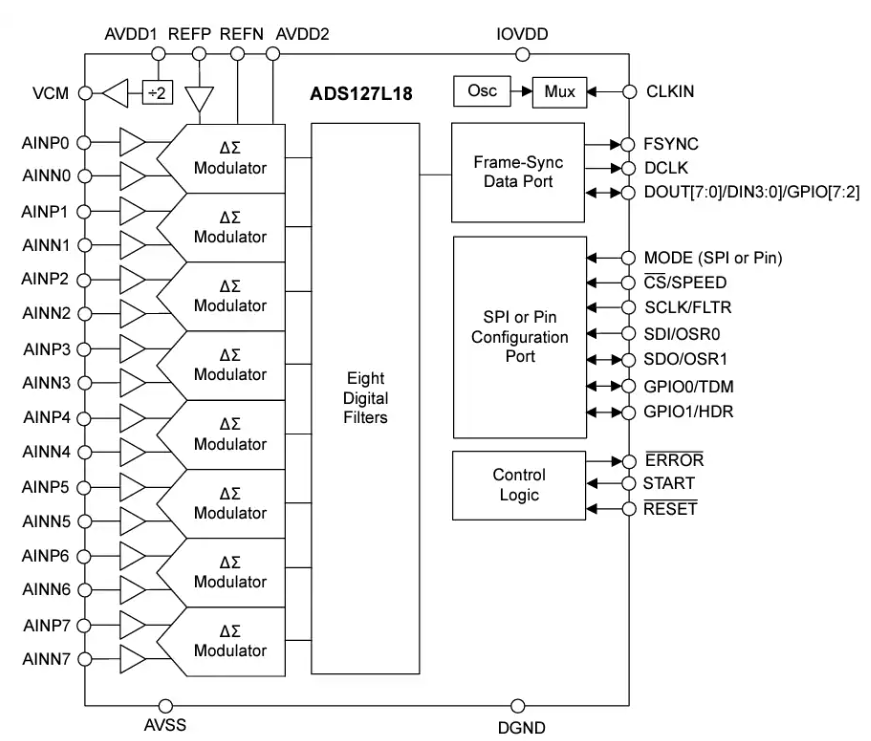

方框圖

ADS117L14(4 通道)與 ADS117L18(8 通道)是 16 位 ΔΣ 架構(gòu)同步采樣模數(shù)轉(zhuǎn)換器(ADC),支持最高 1365.3kSPS 數(shù)據(jù)率與寬頻帶信號(hào)處理,集成可編程濾波器、輸入緩沖及多模式數(shù)據(jù)接口,適用于測(cè)試測(cè)量、工業(yè)自動(dòng)化、航空航天等高精度多通道數(shù)據(jù)采集場(chǎng)景。

一、核心特性

1. 采樣與信號(hào)性能

- 數(shù)據(jù)率與濾波器模式 :提供兩種核心濾波模式,寬帶濾波器(最高 512kSPS,線性相位、106dB 阻帶衰減)適合交流信號(hào),低延遲濾波器(最高 1365.3kSPS,3.9μs 轉(zhuǎn)換延遲)適合直流信號(hào);支持 4 檔功率可縮放速度模式,功耗隨數(shù)據(jù)率降低而減少(如低速模式單通道功耗低至 3mW)。

- 精度指標(biāo) :200kSPS 時(shí)信噪比(SNR)典型值 97.7dB,總諧波失真(THD)低至 - 115dBc,積分非線性(INL)±1LSB,失調(diào)漂移 60nV/℃,增益漂移 1ppm/℃,確保寬溫范圍(-40℃至 125℃)內(nèi)的高精度測(cè)量。

- 輸入范圍與緩沖 :支持 ±VREF 或 ±2VREF 差分輸入范圍,集成輸入預(yù)充電緩沖器,可降低輸入電流(緩沖開(kāi)啟時(shí)典型 ±0.4μA)與采樣噪聲,適配低帶寬信號(hào)驅(qū)動(dòng)場(chǎng)景。

2. 集成功能模塊

- 可編程數(shù)字濾波器 :寬帶濾波器提供 1x-256x 過(guò)采樣比(OSR),阻帶衰減 106dB;低延遲濾波器含 sinc4、sinc4+sinc1 等 4 種拓?fù)洌С?50/60Hz 工頻噪聲抑制(NMRR 達(dá) 100dB)。

- 校準(zhǔn)與診斷 :每通道配備 24 位偏移與增益校準(zhǔn)寄存器,支持硬件 / 軟件復(fù)位;集成 CRC 校驗(yàn)(SPI 接口與寄存器映射)、調(diào)制器飽和檢測(cè)(MOD_FLAG)及電源電壓監(jiān)控(ALV_FLAG),提升系統(tǒng)可靠性。

- 參考電壓管理 :支持 0.5-2.75V(低范圍)或 1V-AVDD1(高范圍)差分參考輸入,可選 REFP 緩沖器降低參考端負(fù)載,VCM 引腳提供(AVDD1+AVSS)/2 的共模電壓輸出,用于外部放大器電平匹配。

3. 接口與同步能力

- 數(shù)據(jù)輸出接口 :幀同步(Frame-Sync)接口支持 1/2/4/8 通道時(shí)分復(fù)用(TDM),可級(jí)聯(lián)多器件( Daisy-Chain)減少數(shù)據(jù) lanes;提供 FSYNC(幀時(shí)鐘)與 DCLK(位時(shí)鐘),數(shù)據(jù)格式支持二進(jìn)制補(bǔ)碼(雙極性)或無(wú)符號(hào)二進(jìn)制(單極性)。

- 配置與控制 :支持硬件引腳配置( MODE 引腳選擇,無(wú)需 SPI)或 SPI 編程(16 位命令幀,可選 CRC 校驗(yàn));START 引腳實(shí)現(xiàn)多通道同步采樣,RESET 引腳支持手動(dòng)復(fù)位,GPIO 引腳可復(fù)用為數(shù)據(jù)接口或控制信號(hào)。

二、適用場(chǎng)景

憑借多通道同步采樣、高信噪比及寬溫特性,兩款芯片主要應(yīng)用于以下領(lǐng)域:

- 測(cè)試測(cè)量 :數(shù)據(jù)采集(DAQ)、振動(dòng)分析儀、聲學(xué)檢測(cè)設(shè)備,利用同步采樣與高 SNR 實(shí)現(xiàn)多通道信號(hào)精準(zhǔn)捕獲。

- 工業(yè)自動(dòng)化 :設(shè)備狀態(tài)監(jiān)控、電機(jī)控制,通過(guò)低延遲濾波與抗干擾能力,實(shí)時(shí)反饋設(shè)備運(yùn)行參數(shù)。

- 航空航天與醫(yī)療 :聲吶系統(tǒng)、腦電圖(EEG),依托寬溫工作范圍(-40℃至 125℃)與低失真特性,適配惡劣環(huán)境與高精度生物信號(hào)采集。

- 電網(wǎng)基礎(chǔ)設(shè)施 :電能質(zhì)量分析儀,支持 50/60Hz 工頻噪聲抑制,準(zhǔn)確測(cè)量電壓、電流諧波與功率參數(shù)。

三、硬件設(shè)計(jì)要點(diǎn)

1. 電源與時(shí)鐘設(shè)計(jì)

- 電源需求 :需多組獨(dú)立電源,模擬電源 AVDD1(2.85-5.5V)、AVDD2(1.74-5.5V),數(shù)字電源 IOVDD(1.65-1.95V),負(fù)電源 AVSS(可接地或負(fù)壓,如 - 2.5V 實(shí)現(xiàn)雙極性輸入);每個(gè)電源引腳需并聯(lián) 2.2μF+0.1μF 低 ESR 電容,CAPA/CAPD 引腳(內(nèi)部穩(wěn)壓器輸出)需 10μF/2.2μF 旁路電容。

- 時(shí)鐘配置 :支持內(nèi)部振蕩器(25.6MHz,僅推薦直流測(cè)量)或外部時(shí)鐘(0.5-33.66MHz),時(shí)鐘分頻器(1/2/3/4/8 倍)可調(diào)整 ADC 核心時(shí)鐘;外部時(shí)鐘需低抖動(dòng)(如 100kHz 信號(hào)允許≤50ps RMS 抖動(dòng)),避免 SNR 性能退化。

2. 布局與布線準(zhǔn)則

- 信號(hào)隔離 :模擬輸入(AINP/AINN)、參考電壓(REFP/REFN)需差分走線(阻抗 100Ω,長(zhǎng)度匹配誤差≤5mil),與數(shù)字信號(hào)(SPI、Frame-Sync)間距≥2mm,避免串?dāng)_。

- 地平面處理 :模擬地(AGND)、數(shù)字地(DGND)單點(diǎn)連接,時(shí)鐘地(VSSCLK)獨(dú)立布局;散熱焊盤(pán)需通過(guò)至少 4 個(gè)過(guò)孔連接至接地平面,PCB 銅皮面積不小于封裝(7mm×7mm VQFN)2 倍,控制結(jié)溫(Tj)≤150℃。

- 抗混疊濾波 :輸入需外接低通濾波器(如 4 階 RC),抑制調(diào)制器采樣頻率(fMOD)附近的帶外信號(hào),避免混疊(如 fMOD=12.8MHz 時(shí),需 90dB 衰減以確保信號(hào)純凈)。

3. 初始化與配置

- 模式選擇 :MODE 引腳接 IOVDD 進(jìn)入 SPI 模式(靈活配置所有參數(shù)),接地 / 懸空進(jìn)入硬件模式(通過(guò)引腳 strap 配置速度、濾波器類型);硬件模式下默認(rèn)外部時(shí)鐘、高參考范圍、VCM 輸出使能。

- 同步與校準(zhǔn) :START 引腳提供多通道同步觸發(fā),需確保觸發(fā)信號(hào)周期為 DACLK 周期整數(shù)倍;校準(zhǔn)流程為:短接輸入測(cè)偏移→施加已知信號(hào)測(cè)增益→寫(xiě)入 24 位校準(zhǔn)寄存器,校準(zhǔn)后誤差可降至 ±0.1% FSR 以內(nèi)。

四、工作模式與性能優(yōu)化

1. 核心工作模式

- 同步控制模式 :START 引腳上升沿觸發(fā)同步采樣,后續(xù)采樣持續(xù)進(jìn)行,支持連續(xù)時(shí)鐘觸發(fā)以維持多通道時(shí)序?qū)R。

- 啟停控制模式 :START 引腳高電平啟動(dòng)采樣,低電平停止(當(dāng)前轉(zhuǎn)換完成后終止),適合單次 / 間歇采樣場(chǎng)景,需注意停止前需提前 24 個(gè) DACLK 周期置位 STOP 信號(hào)。

- 掉電與待機(jī) :支持單通道掉電(CHn_PWDN)或全局待機(jī)模式,掉電通道輸出最后一次采樣值,待機(jī)模式下模擬部分?jǐn)嚯娨越档凸模ù龣C(jī)電流典型 60μA)。

2. 性能優(yōu)化手段

- 噪聲抑制 :開(kāi)啟輸入緩沖器(CHn_BUFP/CHn_BUFN)降低輸入噪聲,選擇合適 OSR(如 OSR=64 時(shí)噪聲典型 7.2μV RMS);模擬電源端并聯(lián) 10nF 高頻電容,抑制開(kāi)關(guān)噪聲。

- 失真控制 :輸入信號(hào)幅度控制在 FSR 的 90% 以內(nèi),避免調(diào)制器飽和(MOD_FLAG 置位);參考電壓端使用低噪聲基準(zhǔn)(如 REF6041),并靠近 ADC 布局以減少布線損耗。

- 接口優(yōu)化 :Frame-Sync 接口采用 TDM 模式減少數(shù)據(jù) lanes(如 8 通道可壓縮至 1 lane),級(jí)聯(lián)時(shí)需確保所有器件時(shí)鐘分頻比為 1,且同步觸發(fā)信號(hào)延遲一致。

五、可靠性與封裝

- ESD 防護(hù) :符合 HBM 2000V、CDM 1000V 標(biāo)準(zhǔn),PCB 布局需預(yù)留 TVS 管空間,避免靜電損傷。

- 封裝與散熱 :均采用 7mm×7mm 56 引腳 VQFN 封裝(RSH),結(jié)到環(huán)境熱阻(RθJA)23.5℃/W,需通過(guò)散熱焊盤(pán)與 PCB 銅皮結(jié)合散熱,確保高負(fù)載下結(jié)溫不超 125℃。

- 訂單信息 :量產(chǎn)型號(hào)為 ADS117L14IRSHR(4 通道)、ADS117L18IRSHR(8 通道),均為 2500 片卷帶包裝,RoHS 合規(guī),引腳鍍層為 NIPDAU,MSL 等級(jí) 2(260℃峰值回流)。

-

濾波器

+關(guān)注

關(guān)注

162文章

8447瀏覽量

186116 -

adc

+關(guān)注

關(guān)注

100文章

7932瀏覽量

556747 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

4096瀏覽量

130228 -

數(shù)據(jù)速率

+關(guān)注

關(guān)注

0文章

60瀏覽量

12310

發(fā)布評(píng)論請(qǐng)先 登錄

ADS117L11 400 kSPS、寬帶寬、16位、Δ-ΣADC數(shù)據(jù)表

Texas Instruments ADS127L18 24 位模數(shù)轉(zhuǎn)換器數(shù)據(jù)手冊(cè)

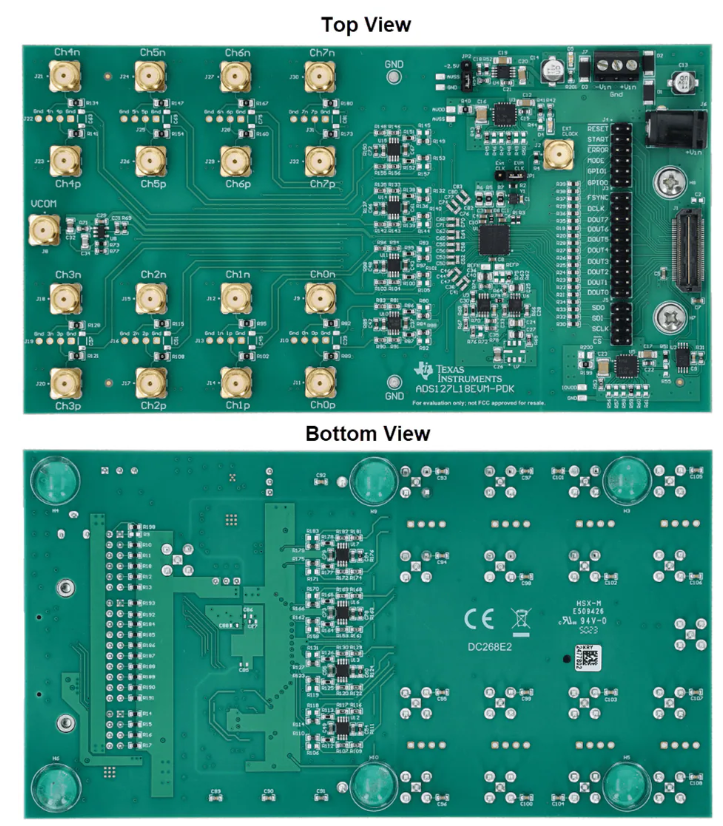

Texas Instruments ADS127L18EVM-PDK 評(píng)估模塊(EVM)數(shù)據(jù)手冊(cè)

ADS117L18 512kSPS、16位、8通道、同步采樣、寬帶寬、Δ-Σ ADC技術(shù)手冊(cè)

ADS8681W/ADS8685W/ADS8689W 核心信息總結(jié)

ADS127L14/ADS127L18 ADC 產(chǎn)品文檔總結(jié)

ADS127L18四通道 / 八通道同步采樣 24 位 ADC 產(chǎn)品文檔總結(jié)

ADS1014L/ADS1015L 系列模數(shù)轉(zhuǎn)換器技術(shù)文檔總結(jié)

ADS1114L/ADS1115L 系列模數(shù)轉(zhuǎn)換器技術(shù)文檔總結(jié)

ADS117L11 技術(shù)文檔總結(jié)

ADS891xB 系列 18 位高精度 SAR ADC 核心信息總結(jié)

ADS127L01 24 位高速寬帶 ADC 核心信息總結(jié)

ADS1262/ADS1263 產(chǎn)品核心信息總結(jié)

ADS4245-EP 核心產(chǎn)品信息總結(jié)

ADS117L14/ADS117L18 核心信息總結(jié)

ADS117L14/ADS117L18 核心信息總結(jié)

評(píng)論