該ADS117L11是一款 16 位 Δσ 模數轉換器 (ADC),使用寬帶濾波器的數據速率高達 400 kSPS,使用低延遲濾波器的數據速率高達 1067 kSPS。該器件將交流性能和直流精度完美結合,功耗低(高速模式下為 18.6 mW)。

該器件集成了輸入和基準緩沖器,以減少信號負載。低漂移調制器可實現出色的直流精度和低帶內噪聲,從而實現出色的交流性能。功率可擴展架構提供兩種速度模式來優化數據速率、分辨率和功耗。

*附件:ads117l11.pdf

數字濾波器可配置為寬帶或低延遲作,優化交流性能或直流信號的數據吞吐量,所有這些都在一個器件中完成。

串行接口具有菊花鏈功能,可減少隔離柵上的SPI I/O。輸入和輸出數據以及寄存器設置通過循環冗余校驗 (CRC) 功能進行驗證,以提高運行可靠性。

小型 3 mm × 3 mm WQFN 封裝專為空間有限的應用而設計。該器件完全符合–40°C至+125°C溫度范圍的額定工作。

特性

- 可編程數據速率:

- 高達 400 kSPS(寬帶濾波器)

- 高達 1.067 MSPS(低延遲濾波器)

- 可選數字濾波器:

- 寬帶或低延遲

- 交流精度與直流精度:

- 動態范圍:97.5 dB (200 kSPS),典型值

- THD:–110 dB,典型值

- INL:0.5 LSB,典型值

- 失調漂移:50 nV/°C,典型值

- 增益漂移:0.6 ppm/°C,典型值

- 電源可擴展架構:

- 高速模式:400 kSPS,18.6 mW

- 低速模式:50 kSPS,3.3 mW

- 輸入和基準預充電緩沖器

- 內部或外部時鐘

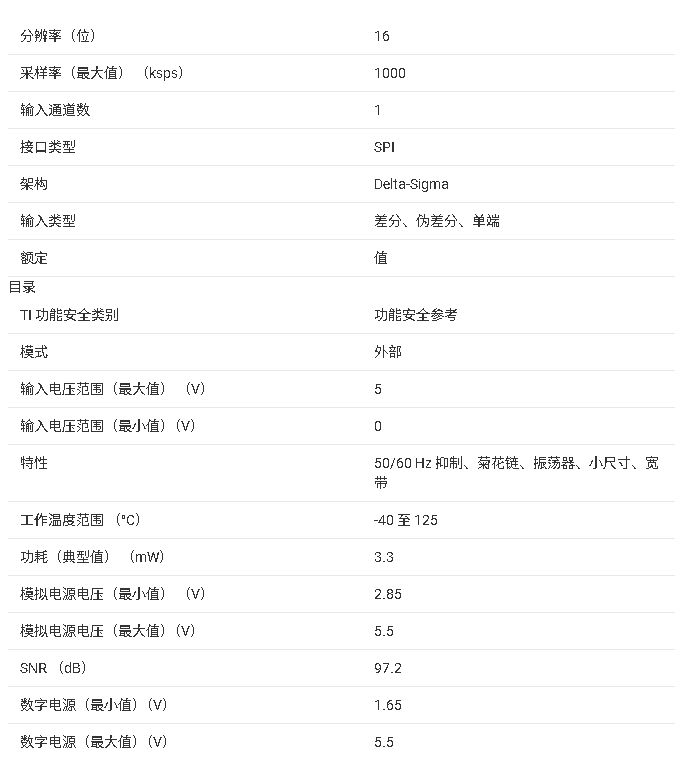

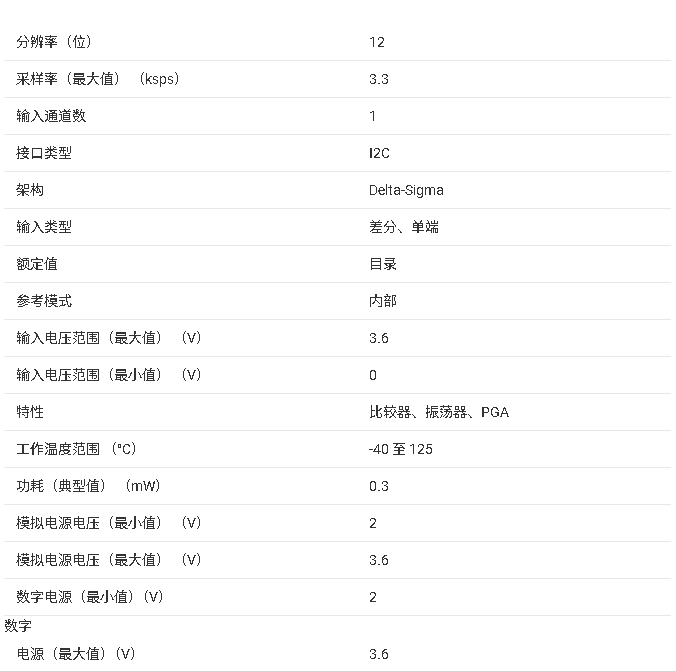

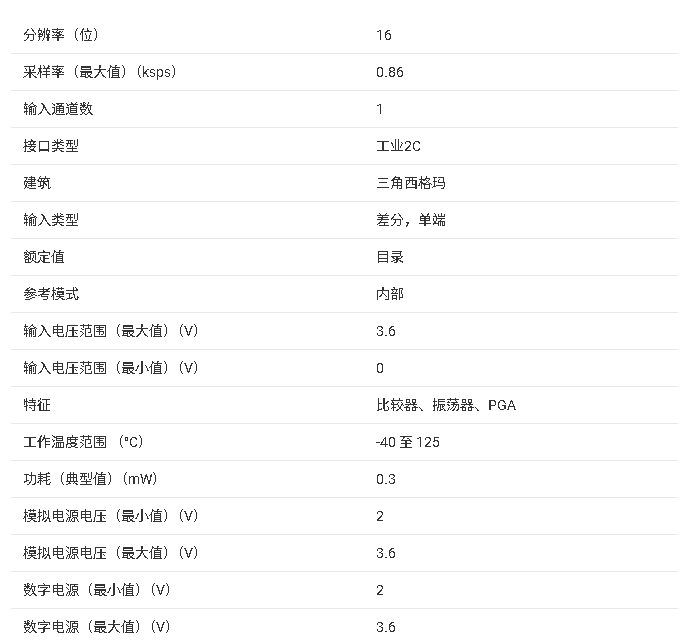

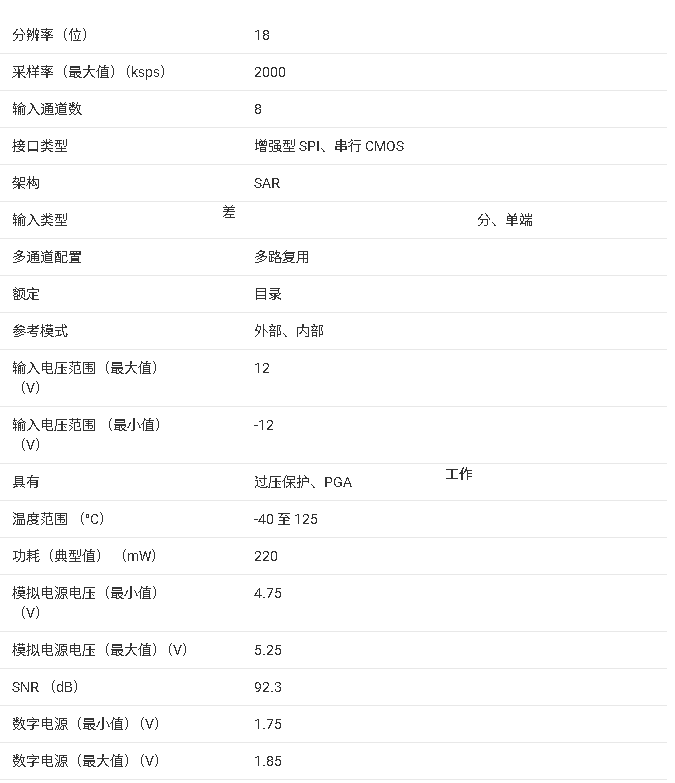

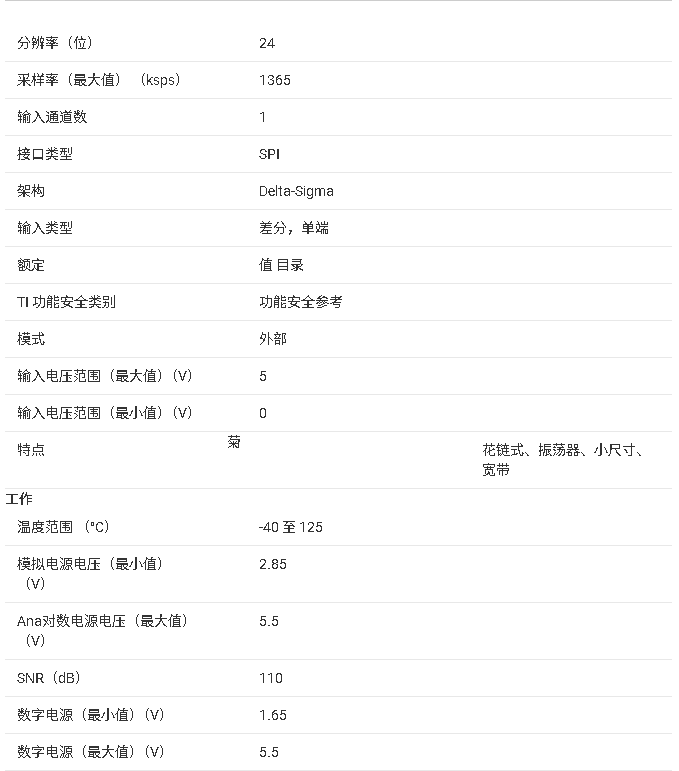

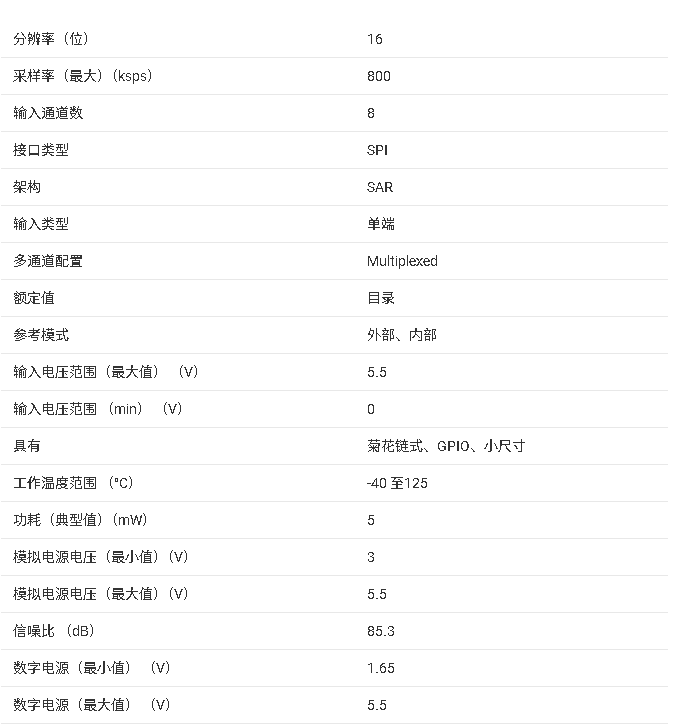

參數

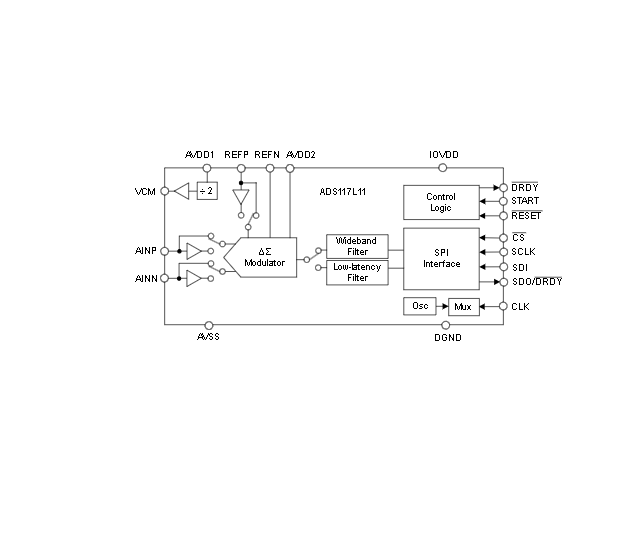

方框圖

一、產品定位與核心屬性

ADS117L11 是德州儀器推出的 16 位高精度 ΔΣ 模數轉換器(ADC) ,采用 3mm×3mm 20 引腳 WQFN 封裝,支持 - 40°C 至 + 125°C 寬溫工作范圍,專為高精度信號采集場景設計,如測試測量(數據采集、振動儀器、聲學設備)、工廠自動化(模擬輸入模塊)、醫療(脈搏血氧儀)及電網基礎設施(電力質量分析儀)。其核心優勢在于 功率可縮放架構 (高速模式 400 kSPS/18.6 mW,低速模式 50 kSPS/3.3 mW)、優異的動態性能(動態范圍 97.5 dB、THD -110 dBc)與直流精度(INL 0.5 LSB、偏移漂移 50 nV/°C),同時集成輸入與基準預充電緩沖器,簡化前端驅動設計,適配多場景高精度信號采集需求。

二、關鍵性能參數

1. 精度與線性度

- 分辨率與完整性 :16 位無缺失碼,支持 1x(±V_REF)/2x(±2V_REF)輸入量程切換,可通過配置實現雙極性(2's 補碼)或單極性(二進制)數據輸出,適配不同信號類型。

- 線性誤差 :積分非線性(INL)典型值 0.5 LSB,微分非線性(DNL)未明確最大值(需結合應用場景評估),確保全量程信號轉換線性度。

- 直流特性 :25°C 時偏移誤差 ±30 μV(最大值 ±250 μV),偏移漂移典型值 50 nV/°C(最大值 200 nV/°C);增益誤差 ±200 ppm FSR(最大值 ±2000 ppm FSR),增益漂移典型值 0.6 ppm/°C(最大值 2 ppm/°C),溫漂特性優異,寬溫環境下精度穩定。

- 抗干擾能力 :直流共模抑制比(CMRR)110-120 dB,10 kHz 時 115 dB;電源抑制比(PSRR)AVDD1/AVDD2/IOVDD 直流均為 95-100 dB,有效抑制共模干擾與電源噪聲。

2. 動態性能(典型值,AVDD1=5V,V_REF=4.096V,1x 量程)

| 參數 | 測試條件 | 典型值 | 單位 |

|---|---|---|---|

| 信噪比(SNR) | 高速模式,寬帶濾波器,f_IN=1kHz,OSR=64 | 97.5 | dBFS |

| 總諧波失真(THD) | 高速模式,f_IN=1kHz,-0.2 dBFS 輸入 | -110 | dBc |

| 無雜散動態范圍(SFDR) | 高速模式,f_IN=1kHz | 110 | dBc |

| 噪聲譜密度(NSD) | 高速模式,寬帶濾波器,OSR=32 | 10.6 | μVrms |

| 正常模式抑制比(NMRR) | f_IN=50/60Hz,對應采樣率 | 100 | dB |

3. 功耗與速率特性

- 功率可縮放 :高速模式(f_CLK=25.6 MHz)功耗 18.6 mW(400 kSPS),低速模式(f_CLK=3.2 MHz)功耗 3.3 mW(50 kSPS),支持空閑、待機、掉電模式,待機功耗 60 μA,掉電功耗 5 μA,適配低功耗場景。

- 采樣速率 :寬帶濾波器最高 400 kSPS(高速模式)/50 kSPS(低速模式);低延遲濾波器(sinc4/sinc3)最高 1.067 MSPS(高速模式)/133 kSPS(低速模式),速率與功耗靈活平衡。

- 輸入特性 :輸入阻抗 8 kΩ(100 kHz),輸入電容 7 pF(100 kHz),支持差分輸入,共模電壓(VCM 引腳)輸出 0.95 V((AVDD1+AVSS)/2),可直接驅動外部全差分放大器。

三、硬件設計關鍵信息

1. 引腳功能與配置

- 模擬輸入 :單通道差分輸入(AINP/AINN),支持 AC/DC 耦合,1x 量程時滿量程輸入 ±V_REF,2x 量程時 ±2V_REF;集成輸入預充電緩沖器(CONFIG1 寄存器控制使能),降低前端驅動帶寬需求。

- 基準電壓 :差分基準輸入(REFP/REFN),支持低基準范圍(0.5-2.75V)與高基準范圍(1V 至 AVDD1-AVSS),集成 REFP 預充電緩沖器(CONFIG1 寄存器控制),減少基準采樣電流(典型值 ±2 μA)。

- 電源引腳 :

- 控制與通信引腳 :

- SPI 接口:CS(引腳 7,片選低有效)、SCLK(引腳 9,時鐘)、SDI(引腳 8,數據輸入)、SDO/DRDY(引腳 10,數據輸出 / 數據就緒),支持 3 線 / 4 線模式、菊花鏈連接,集成 CRC 校驗(SPI 通信與寄存器映射)。

- 同步 / 復位:START(引腳 16,轉換啟動)、RESET(引腳 6,硬件復位低有效,內置 20 kΩ 上拉)、DRDY(引腳 11,數據就緒低有效)。

2. 時鐘與基準設計

- 時鐘選項 :支持內部振蕩器(高速模式 25.6 MHz±0.8%,低速模式 3.2 MHz±0.9%)或外部時鐘(高速模式 0.5-26.2 MHz,低速模式 0.5-3.28 MHz),外部時鐘可通過 CLK_DIV 寄存器分頻(÷8)適配低速模式,時鐘抖動需控制(如 200 kHz 信號需 < 20 ps rms)以避免 SNR 劣化。

- 基準配置 :推薦外接高精度基準(如 REF6041 4.096V),REFP/REFN 引腳需就近放置 1μF+0.1μF 旁路電容;低基準范圍(如 2.5V)適配 2x 量程,高基準范圍(如 4.096V)僅支持 1x 量程,需通過 CONFIG1 寄存器的 REF_RNG 位匹配基準電壓。

3. 數字接口與數據處理

- SPI 通信 :兼容 SPI 模式 1(CPOL=0,CPHA=1),支持全雙工操作,幀長度 16/24/32 位(含 STATUS 頭 / CRC 字節),菊花鏈模式可減少多 ADC 系統的 SPI 引腳占用,最大級聯數量受 SCLK 頻率與數據率限制(如 20 MHz SCLK、100 kSPS 數據率時最多 6 片)。

- 數據格式 :雙極性輸出為 16 位 2's 補碼(范圍 - 8000h 至 7FFFh),單極性為 16 位二進制(范圍 0000h 至 FFFFh),可通過 CONFIG4 寄存器的 BIP_UNI 位切換,數據讀取支持同步 / 啟動 - 停止 / 單觸發三種控制模式。

四、功能模塊與配置

1. 模擬前端優化

- 輸入緩沖器 :AINP/AINN 預充電緩沖器(CONFIG1 寄存器 AINP_BUF/AINN_BUF 位),使能后輸入電流降至 ±0.4 μA(低速模式),減少前端驅動負載,適配高阻抗傳感器(如應變片)直接連接;禁用時輸入電流 95 μA/V(高速模式),需前端驅動具備足夠帶寬。

- 輸入多路選擇(MUX) :支持正常極性、反相極性、偏移測試(輸入短接至共模電壓)、共模測試(輸入短接后接 AINP)四種模式,可通過 MUX 寄存器配置,用于系統校準與性能驗證。

- 擴展量程 :CONFIG2 寄存器 EXT_RNG 位使能后,輸入量程擴展 25%(如 1x 量程變為 ±1.25V_REF),提供信號余量,但 SNR 在輸入超 110% 滿量程時會因調制器飽和劣化。

2. 數字濾波器配置

- 寬帶濾波器 :多抽頭 FIR 結構,支持 OSR 32-4096 可調,-0.1 dB 帶寬 0.4×f_DATA,-3 dB 帶寬 0.437×f_DATA,群延遲 34/f_DATA,適合 AC 信號采集(如振動、聲學),高速模式 OSR=32 時數據率 400 kSPS,噪聲 10.6 μVrms。

- 低延遲濾波器 :含 sinc4、sinc4+sinc1、sinc3、sinc3+sinc1 四種配置, latency 最短 4.38 μs(高速模式 sinc4,OSR=12),適合 DC 信號快速采集(如醫療監護),sinc3 模式支持 50/60 Hz 工頻抑制(NMRR 100 dB)。

- 過采樣與噪聲 :OSR 可調(32-4096),噪聲隨 OSR 增加降低(如高速模式 OSR=4096 時噪聲 0.92 μVrms),量化噪聲與熱噪聲共同決定 SNR,多數速率下量化噪聲占主導(SNR≈98 dB)。

3. 校準與電源管理

- 校準功能 :支持 24 位偏移(OFFSET2/1/0 寄存器)與增益(GAIN2/1/0 寄存器)校準,偏移校準通過減去校準值實現,增益校準通過乘以歸一化系數(GAIN/400000h)實現,需存儲校準系數至外部非易失性存儲器,上電后重新配置。

- 電源模式 :

- 正常模式:全功能工作,高速 / 低速模式可通過 SPEED_MODE 位切換。

- 待機模式:轉換停止時自動進入,功耗降至 60 μA,重啟需額外 24 個時鐘周期。

- 掉電模式:CONFIG2 寄存器 PWDN 位使能,僅保留 SPI 與數字 LDO,功耗 5 μA,喚醒需清除 PWDN 位或復位。

五、應用設計與布局建議

1. 典型應用電路

以高精度數據采集系統為例,前端采用 THS4551 全差分放大器(135 MHz GBW,50 ns settling 時間),搭配 4 階抗混疊濾波器(無源 RC + 有源 MFB 結構),實現 12.8 MHz(高速模式調制器頻率)處 90 dB 衰減;ADC 配置為高速模式、1x 量程、寬帶濾波器(OSR=32),基準采用 REF6041 4.096V(噪聲 10 μVrms),數據通過 SPI 傳輸至 FPGA,時鐘采用低抖動晶振(如 Si5351,抖動 < 100 fs),保障雙通道同步采樣精度。

2. 電源與濾波設計

- 電源架構 :AVDD1 推薦 “開關電源(如 TPS62821)+3Ω 串聯電阻 + 1μF+0.1μF 旁路電容”,AVDD2/IOVDD 直接并聯 1μF+0.1μF 電容,CAPA/CAPD 引腳分別外接 1μF 電容至 AVSS/DGND,減少電源紋波與 LDO 噪聲。

- 抗混疊濾波 :模擬輸入串聯 22Ω 電阻 + 2.2 nF 電容(截止頻率≈3.6 MHz),REFP/REFN 引腳并聯 1μF+0.1μF 電容,抑制高頻噪聲耦合,適配 ΔΣ ADC 的噪聲整形特性。

3. 布局 Guidelines

-

濾波器

+關注

關注

162文章

8411瀏覽量

185686 -

adc

+關注

關注

100文章

7511瀏覽量

555926 -

模數轉換器

+關注

關注

26文章

4013瀏覽量

130100 -

調制器

+關注

關注

3文章

975瀏覽量

48496

發布評論請先 登錄

ADS127L11和ADS127L01相比主要突出的特點有哪些?

理解和運用ADS127L11EVM GUI中的Histogram Analysis

ADS117L11 400 kSPS、寬帶寬、16位、Δ-ΣADC數據表

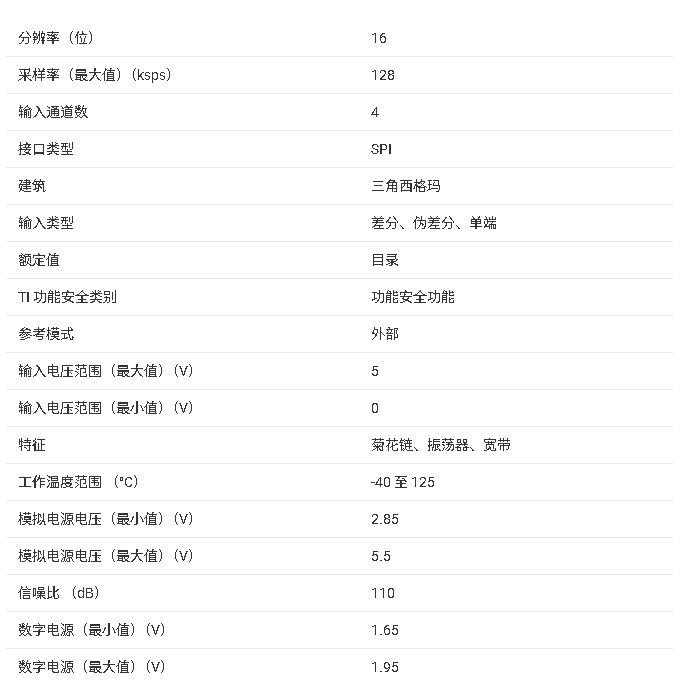

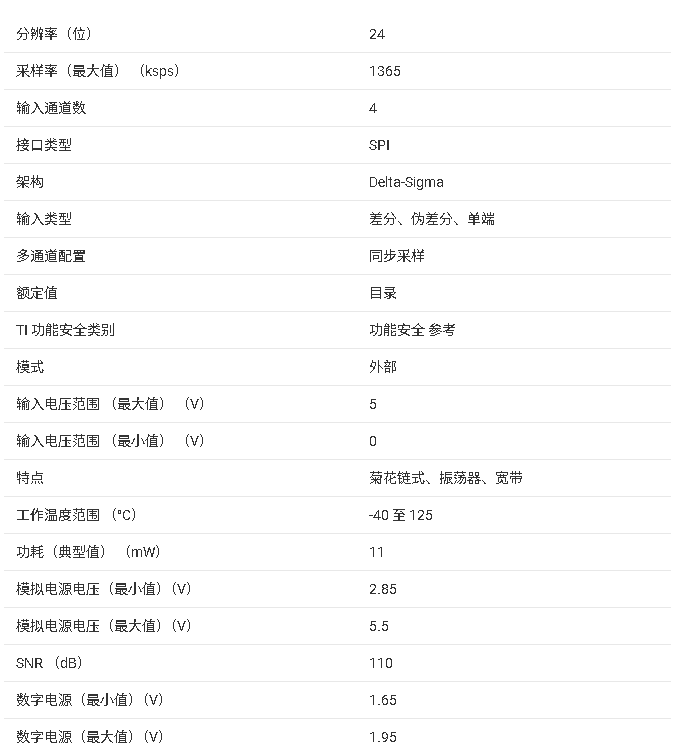

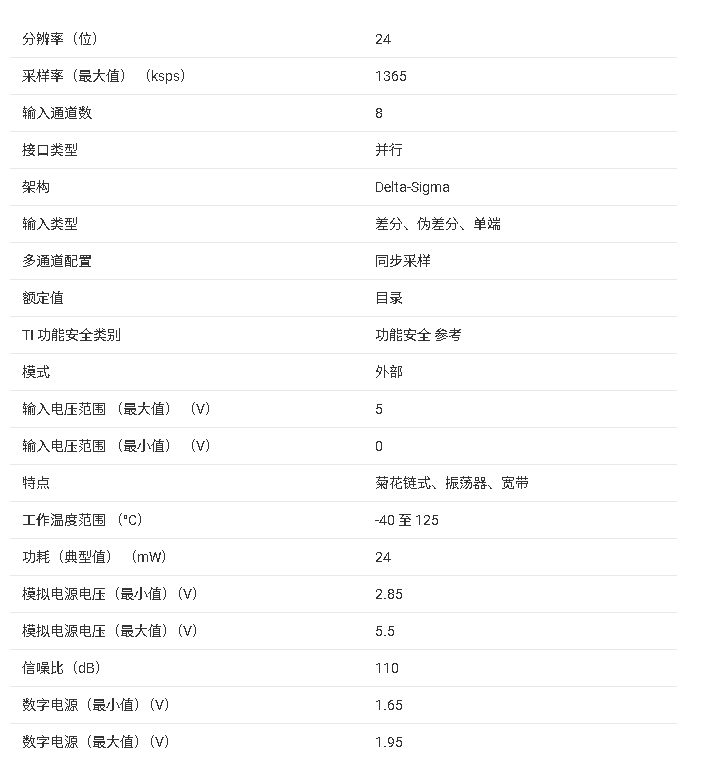

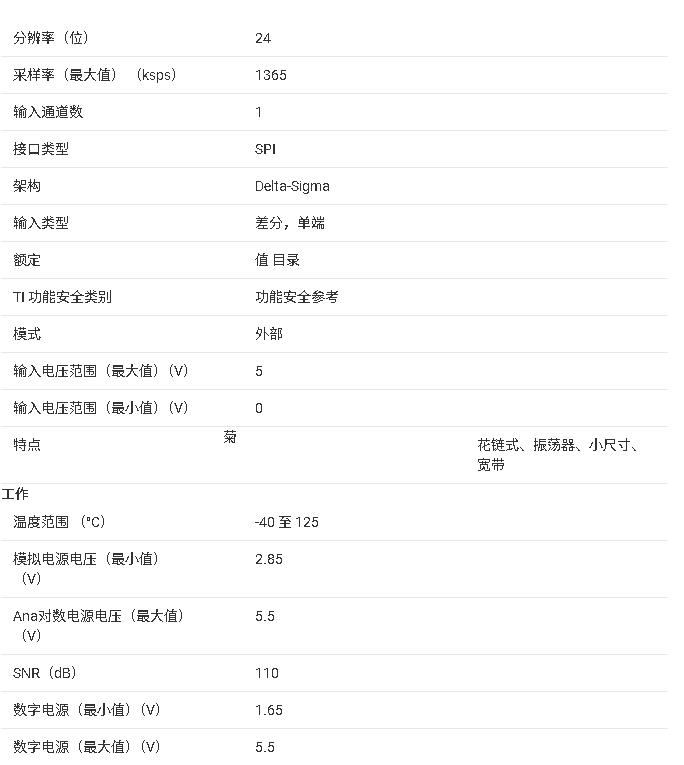

ADS117L14/ADS117L18 核心信息總結

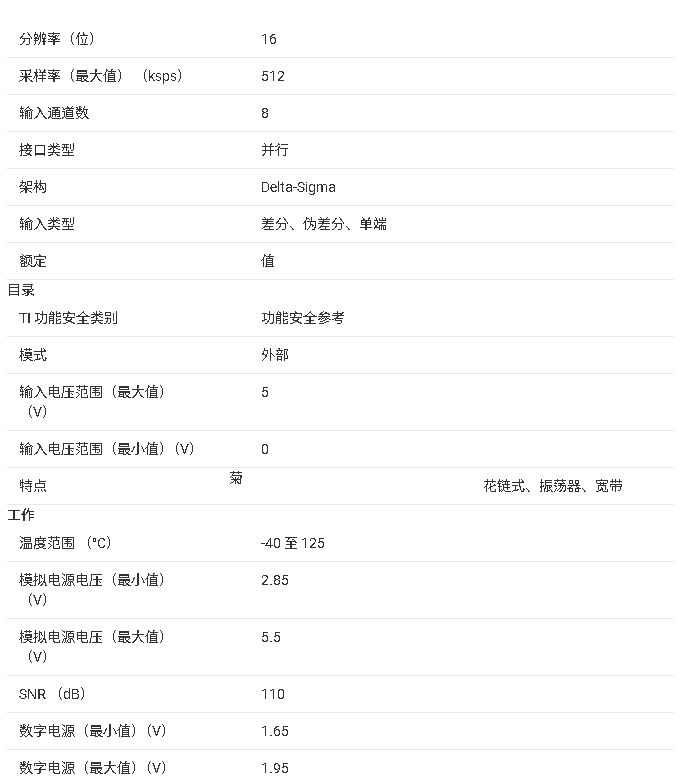

ADS117L18 512kSPS、16位、8通道、同步采樣、寬帶寬、Δ-Σ ADC技術手冊

ADS127L14/ADS127L18 ADC 產品文檔總結

ADS127L18四通道 / 八通道同步采樣 24 位 ADC 產品文檔總結

ADS127L21B 產品技術文檔總結

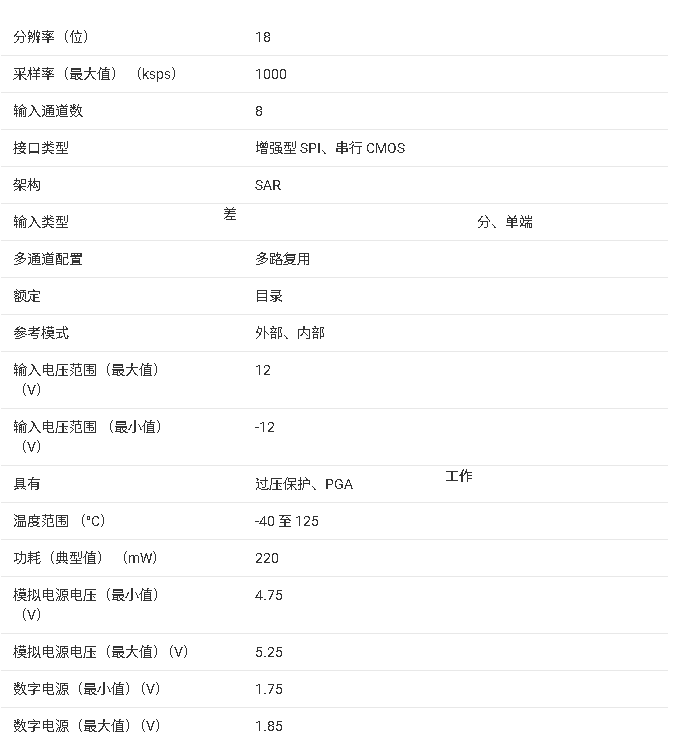

ADS9815/ADS9817 產品技術文檔總結

ADS1014L/ADS1015L 系列模數轉換器技術文檔總結

ADS1114L/ADS1115L 系列模數轉換器技術文檔總結

ADS9817 技術文檔總結

ADS127L21 技術文檔總結

ADS7067 技術文檔總結

ADS117L11 技術文檔總結

ADS117L11 技術文檔總結

評論