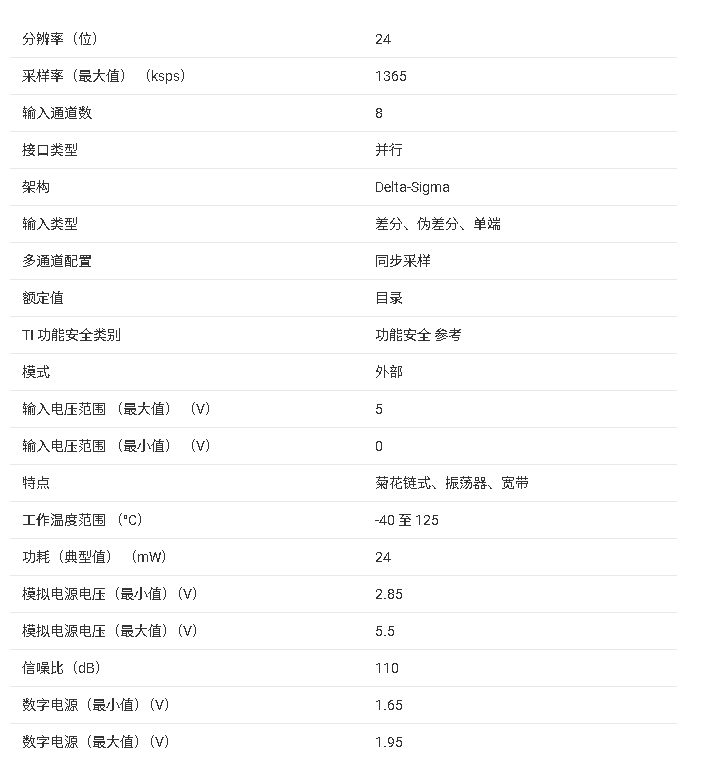

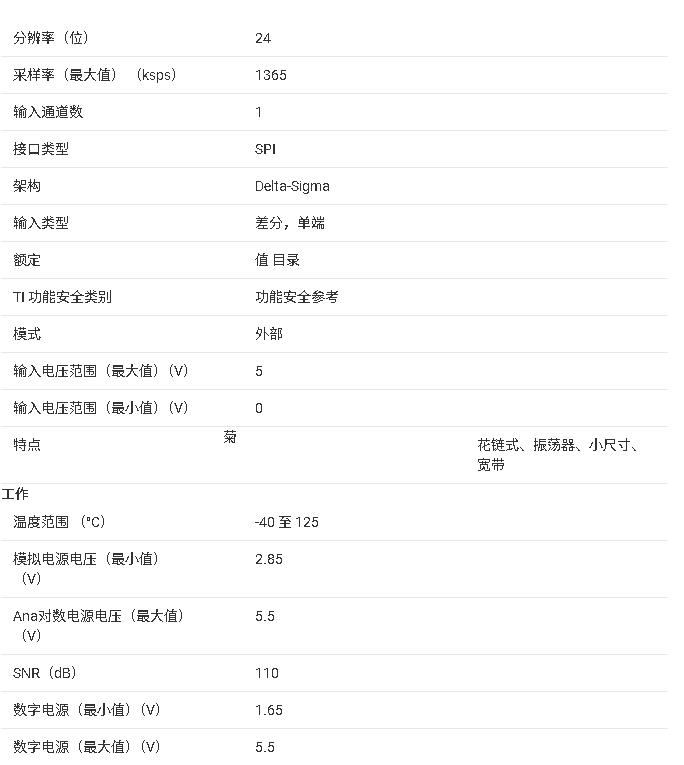

ADS127L14(四通道)和ADS127L18(八進制)是基于單通道ADS127L11的24位、增量Σ(ΔΣ)模數轉換器(ADC)。這些器件提供4個或8個通道的同步采樣,數據速率高達512kSPS(寬帶濾波器模式)和1365kSPS(低延遲濾波器模式)。

*附件:ads127l14.pdf

特性

- 同時測量四個或八個通道

- 寬帶濾波器模式:高達 512kSPS

- 低延遲濾波模式:高達 1365kSPS

- 功率可擴展速度模式:

- 最大速度:512kSPS

- 83mW (ADS127L14)

- 165mW (ADS127L18)

- 高速:400kSPS

- 64mW (ADS127L14)

- 128mW (ADS127L18)

- 中速:200kSPS

- 37mW (ADS127L14)

- 74mW (ADS127L18)

- 低速:50kSPS

- 12mW (ADS127L14)

- 24mW (ADS127L18)

- 最大速度:512kSPS

- 具有直流精度的交流性能:(高速模式)

- 200kSPS時的動態范圍:112dB(典型值)

- 總諧失真:–118dB(典型值)

- INL:1ppm FSR(典型值)

- 失調漂移:10nV/°C(典型值)

- 增益漂移:0.5ppm/°C(典型值)

- 預充電緩沖信號輸入

- 可通過引腳設置或 SPI 進行編程

- 用于輸出數據的幀同步端口

- 內部或外部時鐘作

- 模擬電源電壓:2.85V 至 5.5V

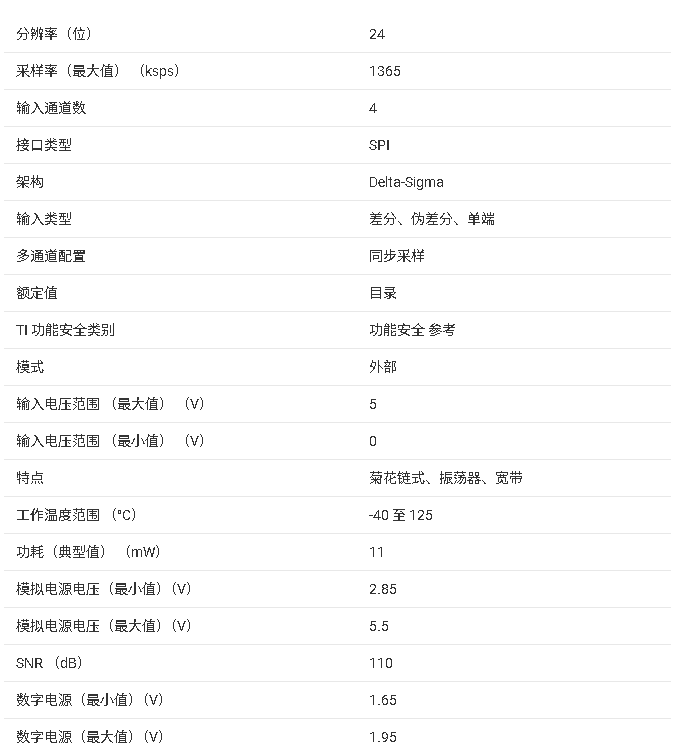

參數

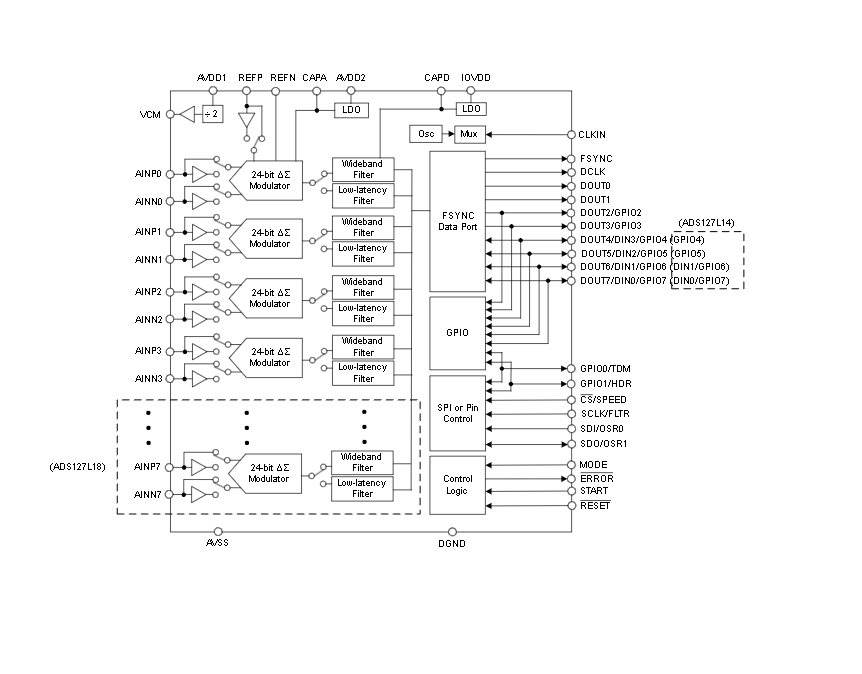

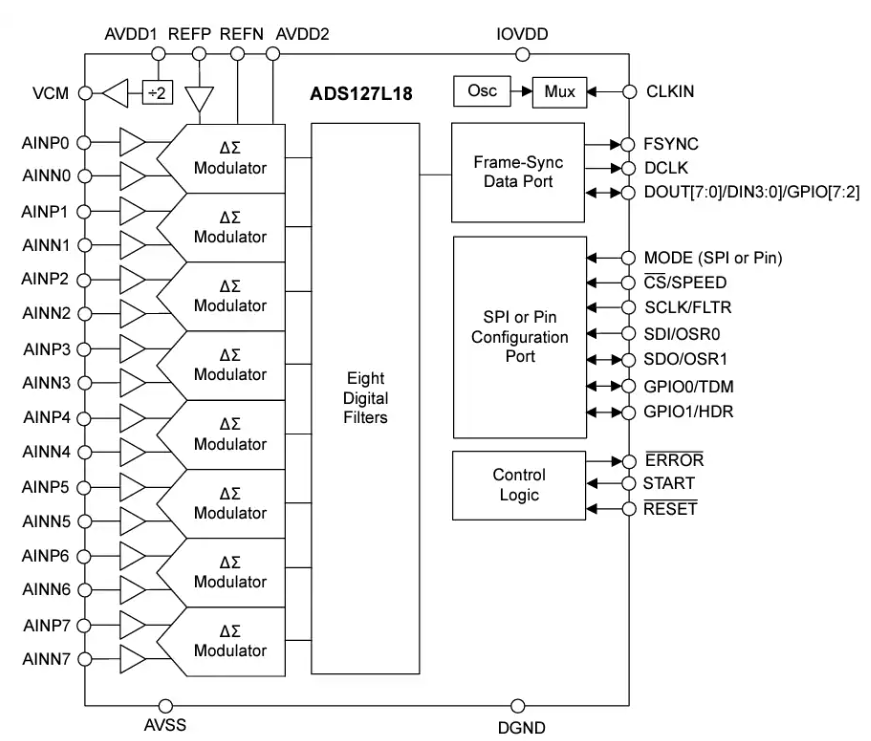

方框圖

一、產品概述

ADS127L14(四通道)與 ADS127L18(八通道)是德州儀器推出的 24 位 delta-sigma(ΔΣ)架構模數轉換器(ADC),核心優勢為 多通道同步采樣 、 高分辨率與寬信號帶寬平衡 、 功率可縮放 ,適用于高精度數據采集場景。兩款產品封裝與核心架構一致,僅通道數量差異,均支持 - 40°C 至 + 125°C 工業級工作溫度,滿足測試測量、工廠自動化、航空航天、醫療等領域需求。

二、核心參數對比

兩款產品核心差異為通道數量,關鍵性能參數一致,具體如下:

| 參數 | ADS127L14(四通道) | ADS127L18(八通道) | 備注 |

|---|---|---|---|

| 分辨率 | 24 位(無失碼) | 24 位(無失碼) | 支持 16 位 / 24 位輸出分辨率切換 |

| 采樣速率 | 寬帶濾波模式:最高 512kSPS;低延遲濾波模式:最高 1365kSPS | 同左 | 采樣速率隨速度模式與過采樣率(OSR)可調 |

| 功耗(典型值) | 最高速模式:83mW;低速模式:12mW | 最高速模式:165mW;低速模式:24mW | 功率隨速度模式線性縮放 |

| 動態范圍(DR) | 高速模式 200kSPS 下:112dB | 同左 | 寬帶濾波模式,OSR=64 |

| 總諧波失真(THD) | 高速模式 1kHz 輸入:-118dB | 同左 | 1x 輸入范圍,V_REF=4.096V |

| 積分非線性(INL) | ±1ppm of FSR | 同左 | 全溫度范圍典型值 |

| 輸入帶寬 | 寬帶濾波模式 - 3dB 帶寬:0.4374×f_DATA | 同左 | f_DATA 為輸出數據率 |

| 電源電壓 | 模擬:2.85V-5.5V(AVDD1);數字:1.8V(IOVDD) | 同左 | 支持單極性(如 5V/0V)或雙極性(如 ±2.5V)供電 |

三、硬件設計關鍵信息

1. 封裝與引腳

- 封裝類型 :均采用 56 引腳 VQFN(RSH 封裝),尺寸 7mm×7mm,暴露熱焊盤需接地以保證散熱(熱阻 RθJA=23.5°C/W)。

- 關鍵引腳功能 :

- 模擬輸入:AINPn/AINNn(n=0-3/7,通道正負端),支持差分輸入,需匹配 VCMOUT 共模電壓(典型為 (AVDD1+AVSS)/2)。

- 電源:AVDD1(模擬主電源)、AVDD2(模擬輔助電源)、IOVDD(數字 I/O 電源)、AVSS(模擬地),需按要求搭配 2.2μF/10μF X7R 陶瓷去耦電容。

- 基準與共模:REFP/REFN(基準電壓正負端,支持 0.5V-5V 差分輸入)、VCM(共模電壓輸出,需接 1μF 去耦電容)。

- 時鐘與數據:CLKIN(外部時鐘輸入)、FSYNC(幀同步信號)、DCLK(數據時鐘)、DOUTx/DINx(差分數據 I/O,支持菊花鏈)。

- 配置引腳:MODE(選擇硬件 / SPI 配置)、SCLK/SDI/SDO(SPI 配置接口)、START/RESET(同步 / 復位控制)。

2. 電源與基準設計

- 電源要求 :

- 單極性供電:AVDD1=5V、AVSS=0V;雙極性供電:AVDD1=2.5V、AVSS=-2.5V,AVDD2 可接 AVDD1 或獨立降壓(1.8V-5V)以降低功耗。

- 去耦電容:AVDD1/AVDD2/IOVDD 需就近接 2.2μF 去耦電容,CAPA(模擬穩壓器輸出)接 10μF 電容,REFP/REFN 接 2.2μF(緩沖開啟)或 10μF(緩沖關閉)電容。

- 基準選擇 :

四、核心功能與配置

1. 采樣與濾波

- 同步采樣 :所有通道嚴格同步采樣,支持多芯片菊花鏈同步(通過 START 引腳或 SPI 命令),同步后濾波需 68 個數據周期穩定(寬帶濾波)。

- 雙濾波模式 :

- 寬帶濾波 :線性相位 FIR 架構,通帶紋波 ±0.0004dB,阻帶衰減 106dB,適合 AC 信號測量,支持 OSR=32-4096,數據率 512kSPS(最高速)-0.39kSPS(低速)。

- 低延遲濾波 :CIC(sinc)架構,支持 sinc4、sinc4+sinc1、sinc3、sinc3+sinc1 四種配置,延遲低至 3.9μs(最高速模式),適合 DC 信號快速采集,數據率最高 1365kSPS。

- 過采樣(OSR) :可編程 OSR=12-4096,OSR 提升可降低噪聲(如 OSR=4096 時動態范圍達 139dB),輸出數據率 = f_MOD/OSR(f_MOD= f_CLK/2)。

2. 數據接口與傳輸

- 幀同步(Frame-Sync)接口 :

- 支持 1/2/4/8 車道(TDM 時分復用),DOUTx 引腳可切換為 GPIO 或菊花鏈 DINx 輸入,數據幀含可選 STATUS 頭字節(通道狀態)與 CRC 字節(錯誤檢測)。

- 數據格式:24 位二進制補碼(默認)或 16 位左對齊,MSB 優先,支持數據重復或菊花鏈級聯(多芯片擴展通道)。

- SPI 配置接口 :

- 支持 SPI 模式 1(CPOL=0, CPHA=1),可通過 SPI 或硬件引腳配置(MODE 引腳選擇),寄存器分全局配置(時鐘、電源)與通道配置(濾波、增益)。

- 錯誤檢測:支持 SPI CRC(8 位)、寄存器映射 CRC(16 位)、時鐘計數錯誤、地址越界檢測,ERROR 引腳(開漏)指示錯誤狀態。

3. 校準與診斷

- 校準功能 :

- 偏移校準:每通道 24 位偏移寄存器(CHn_OFS),支持 ±16LSB 微調,校準值以二進制補碼存儲,在增益校準前生效。

- 增益校準:每通道 24 位增益寄存器(CHn_GAN),默認 400000h(增益 = 1),校準值以無符號二進制存儲,公式:

校準后數據=(原始數據-偏移)×增益/400000h。

- 診斷功能 :

- 溫度監測:無內置溫度傳感器,可通過輸入短接測噪聲漂移間接判斷溫度影響。

- 自測試:輸入多路器支持短路(測偏移 / 噪聲)、全量程(測增益)、共模(測 CMRR)測試模式,通過 CHn_CFG1 寄存器配置。

- 電源監測:ALV_FLAG(模擬欠壓)、POR_FLAG(上電復位)監測電源狀態,ERROR 引腳同步指示。

4. 功率與速度模式

四檔速度模式 :通過 GEN_CFG2 寄存器選擇,速度與功耗線性匹配:

速度模式 f_CLK 最高采樣率(寬帶濾波) 功耗(ADS127L14) 最高速 32.768MHz 512kSPS 83mW 高速 25.6MHz 400kSPS 64mW 中速 12.8MHz 200kSPS 37mW 低速 3.2MHz 50kSPS 12mW 省電模式 :通道可獨立斷電(CHn_CFG2 寄存器),斷電后輸出最后一次有效數據;待機模式(STBY_MODE)停止采樣,功耗降低 50% 以上。

五、應用設計與布局

1. 典型應用

- 信號鏈設計 :輸入需搭配抗混疊濾波器(推薦 THS4551 全差分放大器),四階濾波器可實現 12.8MHz(f_MOD)處 90dB 衰減,避免信號混疊。

- 多通道擴展 :通過菊花鏈級聯(DOUTx 接下一片 DINx),支持最多 32 片級聯,需同步 CLKIN 與 START 信號,DCLK 頻率需滿足

f_DCLK ≥ f_DATA×TDM比×數據包長度。

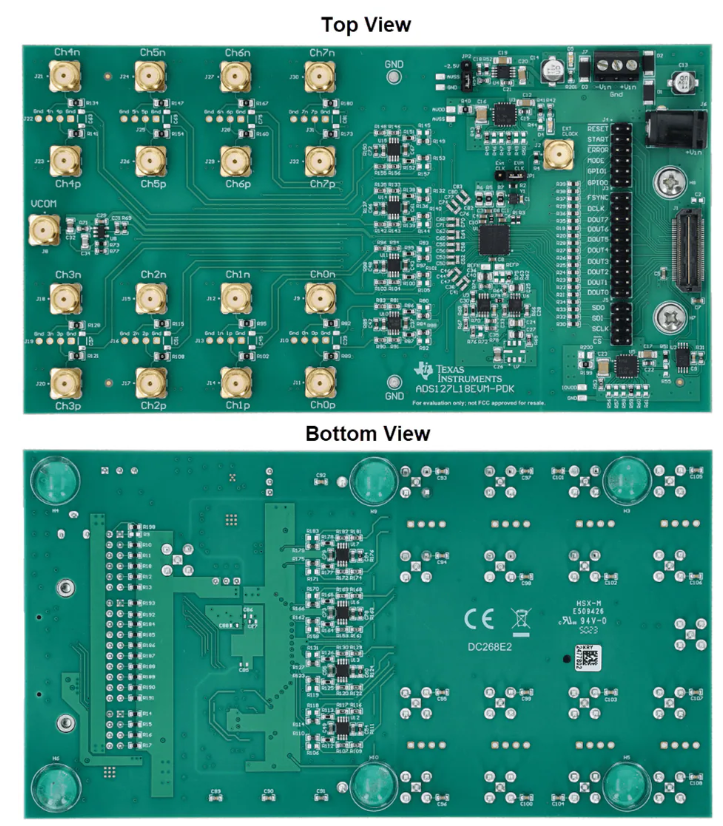

2. PCB 布局準則

- 分層設計 :至少 4 層板,內層為地與電源平面,模擬地(AVSS)與數字地(DGND)單點連接(ADC 處),避免數字噪聲串擾。

- 布線要求 :

- 模擬輸入(AINPn/AINNn)采用等長差分對布線,遠離數字線(如 SCLK、DCLK)。

- 時鐘線(CLKIN)需短且阻抗匹配(串 10Ω 電阻),避免與其他時鐘線平行。

- 電源平面:AVDD1/AVDD2/IOVDD 獨立平面,熱焊盤需大面積接地,降低熱阻。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

濾波器

+關注

關注

162文章

8444瀏覽量

186091 -

adc

+關注

關注

100文章

7932瀏覽量

556712 -

模數轉換器

+關注

關注

26文章

4095瀏覽量

130224 -

熱焊盤

+關注

關注

0文章

6瀏覽量

5766

發布評論請先 登錄

相關推薦

熱點推薦

ADS127L11磁場升高的時候ADC損壞,為什么?

我們用 ADS127L11這個adc芯片連接霍爾磁場傳感器的模擬輸出。以前傳感器和ADC分開有1.5米距離,沒有出現問題。這次設計的時候讓ADC和磁場傳感器靠在一起。但是發現當磁場升

發表于 11-18 07:50

ADS127L11和ADS127L01相比主要突出的特點有哪些?

ADS127L11除了能實現高達1MSPS的速率外還有哪些地方比ADS127L01有更加突出的特點?

或者說從命名上看幾乎一樣,相比ADS127L11是ADS127L01的“plus

發表于 11-25 07:26

ADS127L01采樣數據不準確是哪里的問題?

ADS127L01這是我寫的使用模擬SPI讀取ADS127L01數據的程序,有使用過的大神可以幫忙解答一下嗎?能否提供一下參考程序?

SET_START_ADS127L01; //拉高START

發表于 12-13 07:35

ADS127L11資料介紹

現推出超小型24位寬帶寬模數轉換器(ADC),可比同類ADC在更寬的帶寬內實現業界領先的信號測量精度。ADS127L11為TI精密寬帶寬ADC系列的全新

發表于 11-04 07:18

理解和運用ADS127L11EVM GUI中的Histogram Analysis

理解和運用ADS127L11EVM GUI中的Histogram Analysis

發表于 10-28 11:59

?1次下載

ADS127L11 400kSPS、寬帶寬、24位、Δ-Σ ADC數據表

電子發燒友網站提供《ADS127L11 400kSPS、寬帶寬、24位、Δ-Σ ADC數據表.pdf》資料免費下載

發表于 07-15 10:53

?2次下載

Texas Instruments ADS127L18 24 位模數轉換器數據手冊

Texas Instruments ADS127L18 24位模數轉換器(ADC)是基于單通道 ADS127L11的Δ-Σ 器件。這些器件可對八個通道進行采樣,數據速率高達512kSPS(寬帶濾波器

Texas Instruments ADS127L18EVM-PDK 評估模塊(EVM)數據手冊

(ADC),支持高達512kSPS(寬帶濾波器)的數據速率和高達1.365MSPS(低延遲濾波器)的數據速率。Texas Instruments ADS127L18具有出色的交流和直流性能以及多種

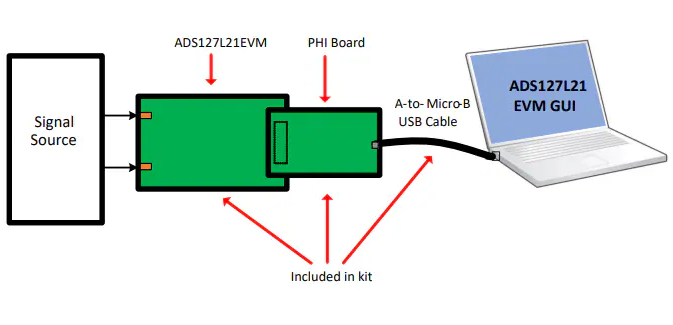

ADS127L21EVM-PDK評估套件技術解析與應用指南

Texas Instruments ADS127L21EVM-PDK評估套件用于評估ADS127L21。ADS127L21是一款24位、高速、定制寬帶寬濾波器Δ-Σ(ΔΣ)模數轉換器 (ADC

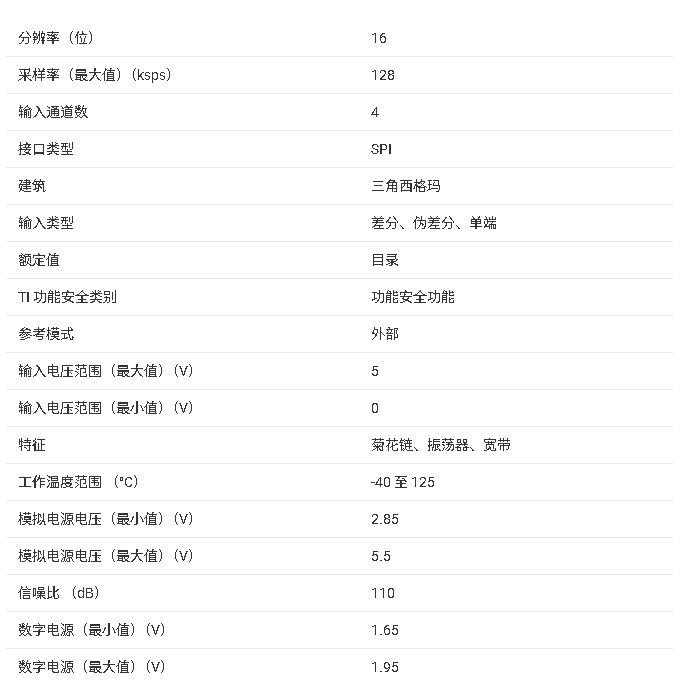

ADS117L14/ADS117L18 核心信息總結

ADS117L14(四通道)和ADS117L18(八進制)是 16 位、三角形 Σ (ΔΣ)、模數轉換器 (ADC)。這些器件提供4個或8個通道的同步采樣,數據速率高達512kSPS(寬帶濾波器模式)和1365kSPS(低延遲濾

ADS127L18四通道 / 八通道同步采樣 24 位 ADC 產品文檔總結

ADS127L14(四通道)和ADS127L18(八進制)是基于單通道[ADS127L11](https://www.ti.com/lit/pdf/SBAS946)的24位、增量Σ(ΔΣ)模數轉換器

ADS127L21B 產品技術文檔總結

該ADS127L21B是一款高精度、24位、Δ-Σ(Δσ)、模數轉換器(ADC),具有可編程數字濾波器。該數字濾波器使用寬帶濾波器的數據速率高達 512kSPS,使用低延遲濾波器的數據速率高達 1365kSPS。該器件提供了交流性能和直流精度的完美組合,功耗低。

ADS127L01 24 位高速寬帶 ADC 核心信息總結

該ADS127L01是一款 24 位、三角積分 (ΔΣ)、帶數據的模數轉換器 (ADC) 速率高達 512 kSPS。該器件提供了出色的直流精度和 出色的交流性能。高階斬波穩定調制器實現了極低的漂移

ADS127L14/ADS127L18 ADC 產品文檔總結

ADS127L14/ADS127L18 ADC 產品文檔總結

評論