TI推出WEBENCH? FPGA Power Architect 電源系統(tǒng)架構(gòu)設(shè)計(jì)工具,它是業(yè)界首款可在幾分鐘內(nèi)仿真及優(yōu)化FPGA電源系統(tǒng)的設(shè)計(jì)工具。WEBENCH FPGA Power Architect 電源系統(tǒng)架構(gòu)設(shè)計(jì)網(wǎng)頁詳列了130多款Altera與 Xilinx 公司最新的FPGA器件的供電要求。包含先進(jìn)FPGA芯片的新一代電源系統(tǒng)的設(shè)計(jì)均較為復(fù)雜,因?yàn)?a target="_blank">工程師往往要加設(shè)多個(gè)能按照不同設(shè)置準(zhǔn)確提供不同驅(qū)動(dòng)電壓的負(fù)載點(diǎn)供電系統(tǒng)。除了必須符合電壓及電流的規(guī)定外,每一負(fù)載點(diǎn)還可能受到其他方面如,紋波、噪聲濾除、同步操作、獨(dú)立供電及啟動(dòng)定義(如軟啟動(dòng))等的特定限制。

-

電源

+關(guān)注

關(guān)注

185文章

18840瀏覽量

263493 -

FPGA

+關(guān)注

關(guān)注

1660文章

22408瀏覽量

636231 -

webench

+關(guān)注

關(guān)注

19文章

70瀏覽量

28646

發(fā)布評(píng)論請(qǐng)先 登錄

電能質(zhì)量在線監(jiān)測裝置的核心芯片架構(gòu)對(duì)裝置性能有哪些影響?

AMD UltraScale架構(gòu):高性能FPGA與SoC的技術(shù)剖析

RUI Builder 圖形化UI設(shè)計(jì)工具

DigiKey 推出業(yè)界首款電源配置工具 使用在線工具一鍵獲取電源解決方案,省時(shí)省力,高效提速設(shè)計(jì)過程

簡單認(rèn)識(shí)eSchema電路設(shè)計(jì)工具

智多晶EDA工具HqFpga軟件的主要重大進(jìn)展

PathFinder在FPGA中的角色與缺陷

FPGA+DSP/ARM架構(gòu)開發(fā)與應(yīng)用

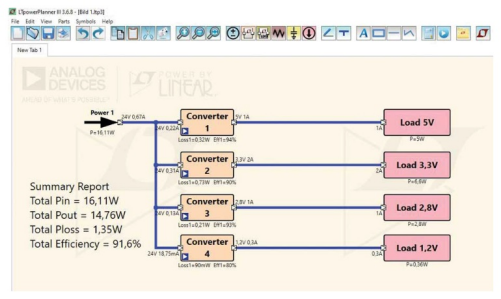

ADI建議電源開發(fā)優(yōu)先考慮電源架構(gòu)的優(yōu)化

智多晶FPGA設(shè)計(jì)工具HqFpga接入DeepSeek大模型

賽盛在線實(shí)操指南講解(五)

安森美WebDesigner+設(shè)計(jì)工具使用心得

使用設(shè)計(jì)工具設(shè)計(jì)的帶通濾波器與Multisim仿真結(jié)果不一致是怎么回事?

設(shè)計(jì)評(píng)審利器——在線評(píng)審工具ReviewHub

WEBENCH FPGA電源架構(gòu)的在線設(shè)計(jì)工具

WEBENCH FPGA電源架構(gòu)的在線設(shè)計(jì)工具

評(píng)論