以下文章來(lái)源于OpenFPGA,作者碎碎思

在 FPGA 的設(shè)計(jì)流程里,有一個(gè)名字幾乎無(wú)人不知:PathFinder。

自 1990 年代末以來(lái),PathFinder 一直是 FPGA 布線(routing)階段的主力算法,為設(shè)計(jì)工具提供“能連通又不重疊”的路徑規(guī)劃方案。

但最近 EPFL + AMD 的團(tuán)隊(duì)在一篇新研究中指出:當(dāng)電路越來(lái)越復(fù)雜、連線越來(lái)越密,「PathFinder 有時(shí)會(huì)失敗」——它的局限性終于被“撕開(kāi)了”。

今天我們就來(lái)聊聊:

PathFinder 為什么關(guān)鍵?

它的經(jīng)典缺點(diǎn)是什么?

在 FPGA 世界里,我們?cè)撊绾慰创蛻?yīng)對(duì)這個(gè)算法的瓶頸?

一、什么是 PathFinder?它為什么重要

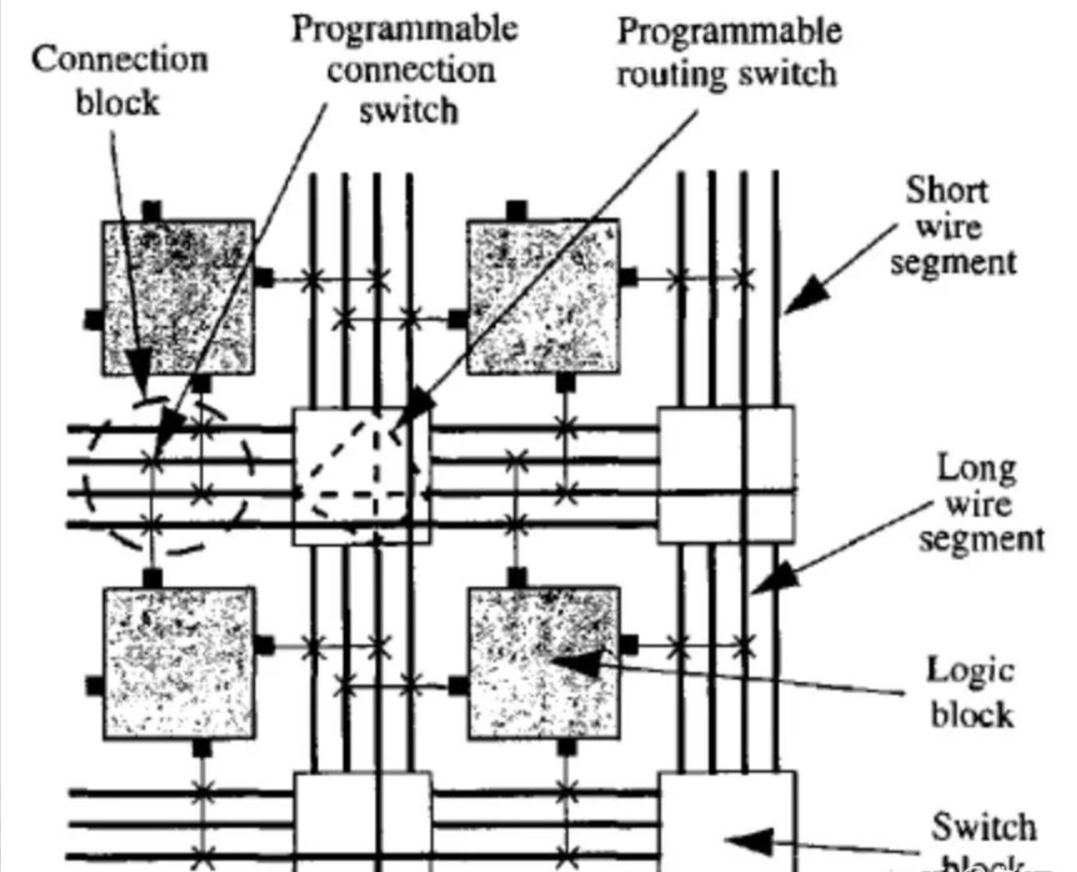

在 FPGA 的后端流程里,布線是最關(guān)鍵的一步:你已經(jīng)確定了模塊擺放(placement),下一步是把各個(gè)信號(hào)連通起來(lái)。這個(gè)過(guò)程中要滿足以下要求:

不重疊(線路不能沖突)

延遲受限(路徑不要過(guò)長(zhǎng))

布線資源有限

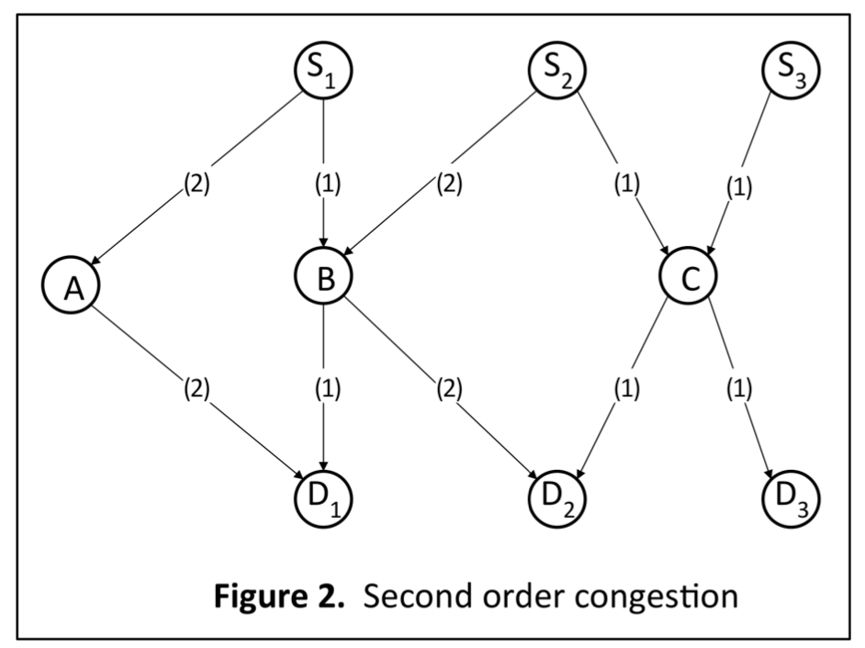

PathFinder 算法正是為了解決這類布線圖形化問(wèn)題的經(jīng)典工具:它會(huì)把信號(hào)當(dāng)做“樹(shù)”(tree)來(lái)連通多個(gè)目標(biāo)點(diǎn)(多點(diǎn)網(wǎng)絡(luò)),在布線資源有限的情況下生成通道。

因?yàn)?FPGA 的互連資源(routing wires、開(kāi)關(guān)節(jié)點(diǎn))是稀缺的,布線越好、沖突越少,設(shè)計(jì)的性能和可路由性就越高。PathFinder 的好壞,直接影響設(shè)計(jì)能不能“布”通、時(shí)序能不能達(dá)標(biāo)。

正因?yàn)樗€(wěn)定、可靠、行之多年,它就成了幾乎所有 FPGA 工具鏈里默認(rèn)的布線模塊。

二、PathFinder 的經(jīng)典缺陷:在大規(guī)模電路里“偶爾翻車”

雖說(shuō) PathFinder 長(zhǎng)期以來(lái)表現(xiàn)“異常穩(wěn)定”,但隨著設(shè)計(jì)變大,它的盲點(diǎn)也慢慢顯現(xiàn)。EPFL / AMD 團(tuán)隊(duì)的研究就揭示了幾個(gè)關(guān)鍵弱點(diǎn):

1. 構(gòu)造出的 routing 樹(shù)往往“比必要的更大”

研究指出,PathFinder 在連接節(jié)點(diǎn)時(shí),有時(shí)會(huì)“過(guò)度擴(kuò)展”樹(shù)枝,使得樹(shù)形結(jié)構(gòu)本可以更簡(jiǎn)潔的情況下被拉得龐大。這樣一來(lái),布線資源被占得更滿,沖突可能性更高。

換句話說(shuō),它有時(shí)不“精打細(xì)算”,而是把可能用得上的路徑都鋪開(kāi)一點(diǎn),以保安全,結(jié)果反而減低整體效率。

2. 分支順序敏感性強(qiáng)

在給信號(hào)添加不同分支(branch)的時(shí)候,PathFinder 的行為很受“添加順序”的影響。不同的順序可能產(chǎn)生完全不同的結(jié)果——有些版本能成功、有些就失敗。團(tuán)隊(duì)發(fā)現(xiàn)在一些“本應(yīng)可布線”的小例子里,PathFinder 表現(xiàn)反常。

也就是說(shuō),在復(fù)雜電路里,“順序”這個(gè)幾乎看不見(jiàn)的決策,可能決定能不能布線成功。

3. 對(duì)極端邊界 /密集連線 /擁塞場(chǎng)景脆弱

在信號(hào)非常密集、資源極度緊張的區(qū)域,PathFinder 有時(shí)被標(biāo)簽為 “unroutable”(無(wú)法路由),即使理論上是有解的設(shè)計(jì)。很多設(shè)計(jì)師遇到這類問(wèn)題時(shí),只能換更大 FPGA、重排模塊、或者放棄部分連接。

這些缺陷在過(guò)去不太被注意,是因?yàn)樵O(shè)計(jì)規(guī)模沒(méi)那么大、資源余量足。但隨著 FPGA 越做越復(fù)雜,可能被壓到極限時(shí),這些弱點(diǎn)就暴露出來(lái)了。

三、面對(duì) PathFinder 的局限,設(shè)計(jì)師怎樣“保命”?

發(fā)現(xiàn)問(wèn)題容易,能改進(jìn)才難。下面是幾個(gè)在實(shí)際工程里常用/建議的對(duì)策:

| 對(duì)策 | 說(shuō)明 |

|---|---|

| 多次嘗試不同參數(shù) / 不同分支順序 | 因?yàn)榉种ы樞蛎舾校o算法多個(gè)“重跑機(jī)會(huì)”,看哪次能成功 |

| 局部手工布線 / 模塊隔離 | 對(duì)于極其擁擠區(qū)域可手工介入,繞開(kāi)算法盲區(qū) |

| 分階段布線 / 分層布線 | 先布通關(guān)鍵 /大信號(hào),再布其他線路,降低沖突可能 |

| 使用替代或增強(qiáng)算法 | 有研究團(tuán)隊(duì)提出改進(jìn)版本,或在 PathFinder 上做 heuristics 增強(qiáng) |

| 優(yōu)化布局(placement) | 布局階段就盡量減少后續(xù)布線難度,為 PathFinder 打基礎(chǔ) |

| 限制設(shè)計(jì)規(guī)模、合理拆分模塊 | 如果設(shè)計(jì)太大,分成多個(gè)子模塊 / 子系統(tǒng)分別布線 |

這些方法各有利弊,有時(shí)得組合使用才穩(wěn)定。

四、小結(jié)

PathFinder 是 FPGA 工具鏈里不可或缺的“布線路徑規(guī)劃器”,但它不是萬(wàn)能的。

在大規(guī)模、資源緊張的設(shè)計(jì)場(chǎng)景中,它的弱點(diǎn)可能導(dǎo)致設(shè)計(jì)“明明可做,卻被標(biāo)簽為不可路由”。

對(duì)普通 FPGA 開(kāi)發(fā)者而言,了解這些局限有助于在設(shè)計(jì)早期就規(guī)避坑、在布線階段提升穩(wěn)定性。

下次當(dāng)工具提示“unroutable”時(shí),別急著換板、別急著重寫(xiě)邏輯,先想想是不是 PathFinder 那棵“樹(shù)”一著不好。

-

FPGA

+關(guān)注

關(guān)注

1662文章

22449瀏覽量

637652 -

amd

+關(guān)注

關(guān)注

25文章

5693瀏覽量

140180 -

算法

+關(guān)注

關(guān)注

23文章

4786瀏覽量

98278 -

布線

+關(guān)注

關(guān)注

9文章

828瀏覽量

86197

原文標(biāo)題:隱形布線之王:深入 PathFinder 在 FPGA 中的角色與缺陷

文章出處:【微信號(hào):FPGA研究院,微信公眾號(hào):FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

如何在FPGA中實(shí)現(xiàn)系統(tǒng)設(shè)計(jì)

FPGA在人工智能中的應(yīng)用有哪些?

轉(zhuǎn):開(kāi)源Pathfinder觸覺(jué)導(dǎo)航-盲人導(dǎo)航器設(shè)計(jì)

請(qǐng)問(wèn)兩臺(tái)藍(lán)牙手機(jī)在匹配過(guò)程中,主從角色的轉(zhuǎn)換過(guò)程是怎樣的?

NI在工業(yè)物聯(lián)網(wǎng)中的角色

DLL在FPGA時(shí)鐘設(shè)計(jì)中的應(yīng)用

基于FPGA玻璃缺陷圖像采集處理系統(tǒng)

DLL在_FPGA時(shí)鐘設(shè)計(jì)中的應(yīng)用

基于FPGA的玻璃缺陷圖像采集預(yù)處理系統(tǒng)設(shè)計(jì)

如何使用FPGA實(shí)現(xiàn)CCD掃描缺陷的檢測(cè)實(shí)時(shí)數(shù)據(jù)處理技術(shù)的論文說(shuō)明

FPGA_ASIC-MAC在FPGA中的高效實(shí)現(xiàn)

Codasip加入Intel Pathfinder for RISC-V設(shè)計(jì)支持計(jì)劃

PathFinder在FPGA中的角色與缺陷

PathFinder在FPGA中的角色與缺陷

評(píng)論