近日,2025年USENIX年度技術會議(ATC'25,The 2025 USENIX Annual Technical Conference)在美國波士頓與OSDI聯合召開。作為計算機系統領域頂級的CCF-A類會議,本屆ATC共收到634篇論文投稿,僅100篇成功入選,中稿率低至15.8%。其中,華為數據中心網絡技術實驗室與中國科學院計算技術研究所合作完成的論文——基于Compute Express Link(CXL)的解耦式機架架構DRack,成功獲收錄。該論文提出在機柜規模內,通過以太網與CXL總線多模式互連構建網卡池-內存池架構DRack,為解決數據中心跨機柜網絡通信帶寬瓶頸提供了創新方案。

研究背景

跨機柜網絡通信帶寬逐漸成為

分布式計算的性能瓶頸

隨著數據密集型應用的廣泛部署,其計算規模已擴展至多主機、多機柜并行,并依托GPU、領域定制加速器等高性能計算單元實現高吞吐處理。這一趨勢對網卡帶寬及網絡帶寬提出更高要求,以滿足機柜間數據同步的時效性需求。

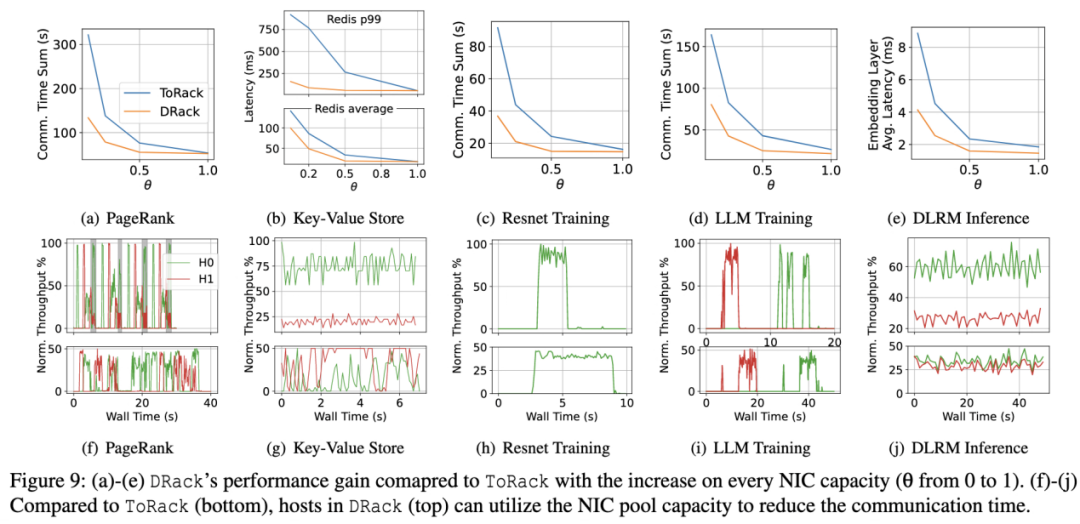

但在傳統柜頂交換機(Top of Rack,ToR)架構中,主機私有網卡與機柜間核心網絡常因資源超額認購(over-subscription),成為跨機柜通信的性能瓶頸。研究通過實證發現:盡管跨機柜通信流量規模大,但單個機柜內主機網卡利用率普遍偏低,核心原因有兩點:一是不同主機計算負載不均衡,數據訪問量差異顯著;二是部分主機僅運行非分布式任務,無數據同步需求。若能實現機柜內閑置網卡資源的動態共享與靈活調度,可有效提升跨機柜通信效率。

研究創新性提出DRack新型機柜架構,通過CXL總線與以太網融合,構建“網卡池-內存池”雙池體系,核心設計包含三點:

網卡解耦與共享池構建:將機柜內所有網卡從主機解耦,形成集中式共享網卡池,可向單個主機提供短時聚合帶寬,大幅提升網卡資源利用率

內存解耦與大帶寬池構建:考慮到主機本地內存及PCIe鏈路帶寬遠低于網卡池總帶寬,單一主機難以充分利用網卡資源,DRack進一步解耦主機內存,構建聚合讀寫帶寬超越網卡池的機柜級內存池,支持網卡池向多內存設備并行讀寫數據。

內存語義直訪優化:允許主機處理器或加速器在計算過程中,通過內存語義直接讀寫內存池數據,無需先經DMA將數據遷移至本地內存,減少數據傳輸環節,提升效率。

選擇CXL互連實現DRack架構,核心在于其兩大特性與設計需求高度契合:一是CXL2.0標準通過CXL交換機支持內存與IO設備池化,CXL3.0進一步實現機柜級內存共享;二是CXL支持CXL.mem協議(內存語義),可滿足主機直訪內存池的需求。

通過上述設計,DRack不僅有效緩解傳統ToR架構的跨機柜通信瓶頸,其更優的通信效率還能為現有任務調度算法(如 Crux@Sigcomm24)提供有力補充。相較于現有方案,DRack采用靜態架構設計,無需應對可重構性與流量預測的復雜性,也無需額外增置硬件;同時可通過向CXL互連架構接入更多內存、網卡設備,實現系統靈活擴展。

實驗效果:多場景性能顯著提升

鑒于目前尚無商業化CXL3.0產品,研究團隊開發了原型驗證系統,用于模擬四機柜DRack架構:每個機柜配備2個定制化 MPSoC FPGA(模擬計算主機,集成四核CPU、雙通道內存、四個光纖端口),CPU通過HP/HPC端口將內存總線信號傳至FPGA側,并實現類CXL協議軟IP;同一機柜的2個FPGA連接服務器雙端口網卡,基于DPDK技術在服務器上仿真網卡池與CXL互連功能。

測試結果顯示,在DNN訓練、圖計算(數據密集型)及鍵值存儲(延遲敏感型)等典型應用場景中,DRack較傳統ToR架構平均降低37.3%的數據同步時間。此外,網卡池帶寬利用率表現優異:單個主機可充分利用帶寬,兩臺主機同時通信時,能根據流量大小動態共享資源,總體帶寬利用率接近1。

技術突破意義

獲國際認可,夯實創新地位

DRack相關技術有望與業界scaleup方案形成深度協同,整體提升高性能計算與分布式系統能力。在面向大規模人工智能計算場景時,該架構能夠顯著增強基于萬卡、千機柜的大語言模型訓練與推理任務的執行效率,降低通信開銷、提升資源利用率。同時,在傳統分布式應用(如圖計算、內存鍵值存儲(如Memcached))等系統中,該技術也可有效優化通訊表現與資源利用率,進一步提升整體系統吞吐與響應性能,為下一代數據中心基礎設施構建提供可擴展、高效率的架構支撐。

此次DRack相關論文獲USENIX ATC收錄,不僅意味著華為與中國科學院計算技術研究所在CXL技術與數據中心機柜架構融合領域的探索,得到國際頂級學術界的高度認可,更標志著華為在數據中心網絡領域的又一重大突破。

-

處理器

+關注

關注

68文章

20250瀏覽量

252206 -

華為

+關注

關注

218文章

36003瀏覽量

262078 -

帶寬

+關注

關注

3文章

1040瀏覽量

43352 -

主機

+關注

關注

0文章

1053瀏覽量

36741

原文標題:榮譽殿堂 | 由華為、中國科學院計算技術研究所聯合開發基于CXL協議的解耦式機架架構DRack論文獲USENIX收錄

文章出處:【微信號:Huawei_Fixed,微信公眾號:華為數據通信】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

合力泰到訪中國科學院福建物質結構研究所調研交流

中國科學院自動化研究所一行蒞臨智行者考察調研

潤和軟件與中國科學院廣州生物醫藥與健康研究院達成戰略合作

中國科學院院士王曦,遞補為中央委員

中國科學院自動化研究所攜手中科曙光打造高性能工具鏈解決方案

奇異摩爾出席第三屆芯粒開發者大會AI芯片與系統分論壇

中國科學院沈陽自動化研究所:研究基于石墨烯/PDMS封裝的醫用膠帶柔性傳感器,用于水下機器人運動檢測

奇異摩爾邀您相約第三屆芯粒開發者大會AI芯片與系統論壇

恭賀 | 晟鵬創始人成會明院士當選歐洲科學院院士!

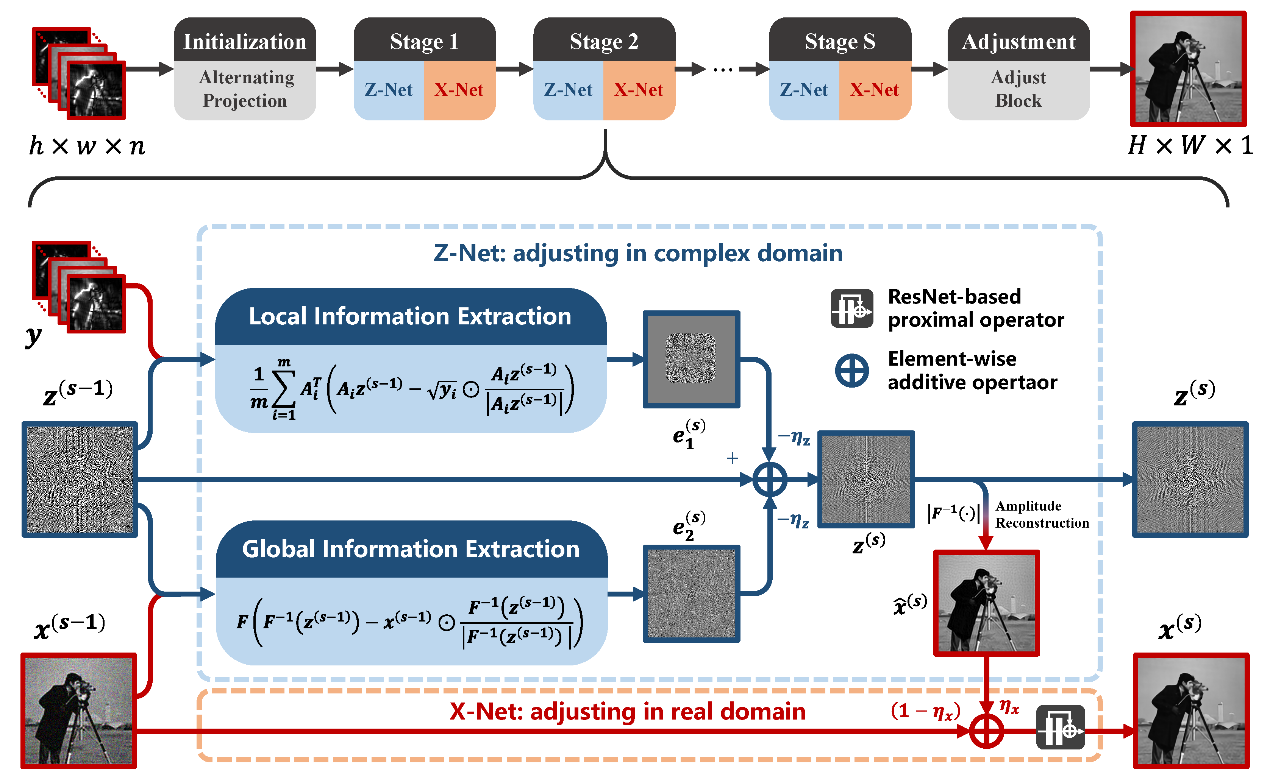

中國科學院西安光機所在計算成像可解釋性深度學習重建方法取得進展

中國科學院上海微系統所開發出高性能10mm大口徑壓電 MEMS 快反鏡

國民技術與中國科學院深圳先進技術研究院達成戰略合作

如何堅持做難而正確的芯片研發?

華為、中國科學院計算技術研究所聯合開發論文獲USENIX收錄

華為、中國科學院計算技術研究所聯合開發論文獲USENIX收錄

評論