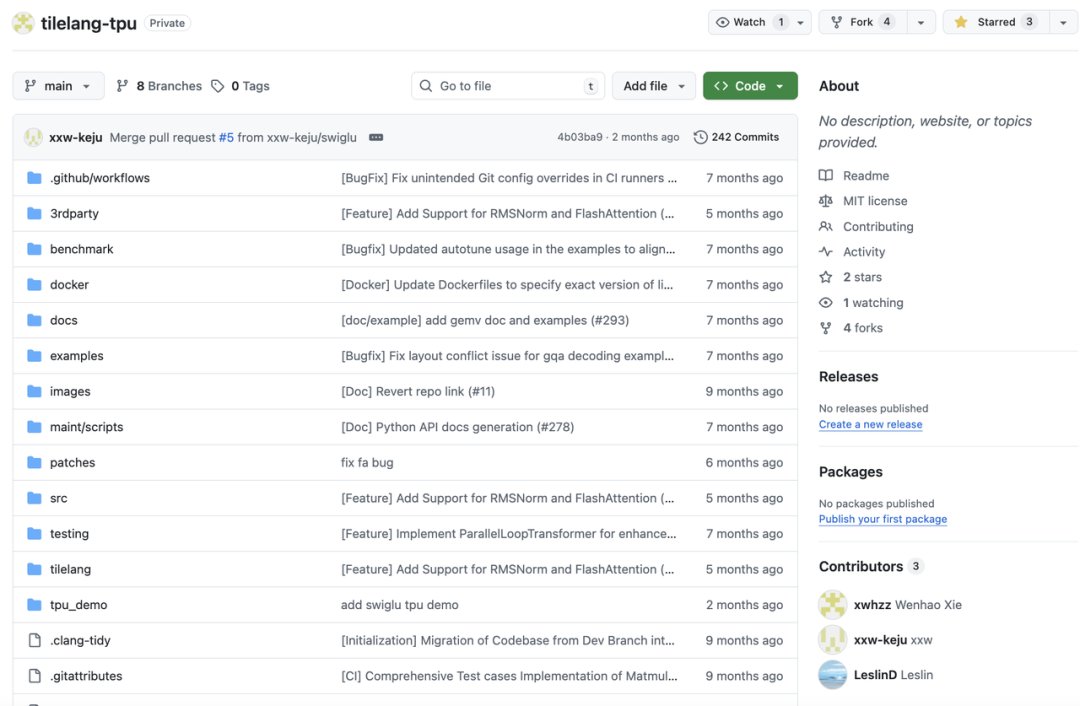

近日,DeepSeek V3.2-Exp 上線,官宣支持國產AI算子編程語言TileLang 并發布了針對 V3.2 的算子示例,這意味著支持“同一語義、跨多后端”的TileLang得到了權威認可,基于算能TPU的TileLang-TPU項目也于近日完成工程驗證。

TileLang 發布之初,算能聯合北京大學、復旦大學、山東大學等高校的科研團隊,共同開展TileLang接入算能TPU的工作,目前已在BM1684X 、SC11等智算平臺上完成了主流大模型算子的工程驗證。

算能SC11 FP300單卡集成256GB LPDDR5X高帶寬內存,內置原生FP8算力單元,板載高達1.1TB/s的內存帶寬,配合PCIe Gen5主機接口及256GB/s的卡間高速互聯,有效應對大模型參數存儲與計算需求,DeepSeek V3滿血版在4卡SC11上吞吐超過600tokens/s。

Tile Language (TileLang) 是一種簡潔的領域專用語言,也是一款開源的 AI 算子編程語言,TileLang 對接算能TPU擴展的工作由北大碩士生解文浩、博士生任天行作為主要負責人牽頭開發,山大、復旦的研發團隊也參與了算子開發、大模型接入TPU的工作,一并表示感謝。

全棧貫通|從可行性到工程閉環

TileLang能夠將高級別的數據流描述,自動轉換并優化為高效的底層代碼(如CUDA或TPU kernel)。通過獨特的Tile級抽象和自動調度能力,開發者可以用更簡潔的代碼表達復雜計算,快速為自己的算法開發一個接近峰值性能的算子,顯著提升算子開發效率。

TileLang-TPU適配路徑以“少驚擾、強約束”為原則:前端僅描述 tile 級計算邏輯與數據流,不引入設備細節;中間以穩定的 Tile-IR 承接形狀推斷、布局決定與算子融合;后端生成面向算能 TPU 的 device 側 C 代碼與指令序列,并與 PPL 的內核注冊、調度與運行時貫通。

該路徑已在典型大模型算子上跑通,涵蓋常見的 GEMM、歸一化與位置相關變換等,完成從算子表達、代碼生成、到 hostdevice 數據搬運和執行的全鏈路打通。由此,TileLang 的一次建模、多后端復用能力在國產 TPU 場景獲得驗證,為后續開源與規模化交付奠定了基礎。

極致簡潔|三步實現 TPU后端支持

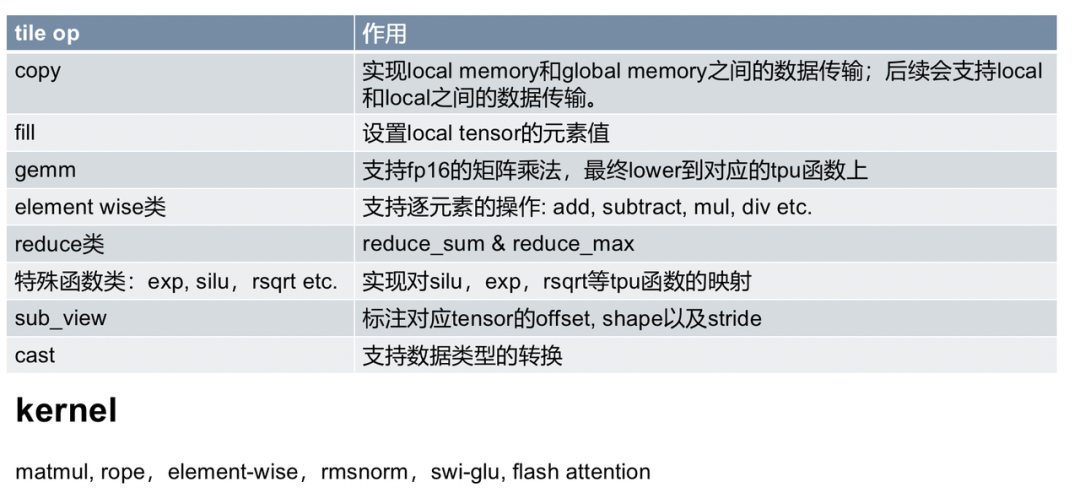

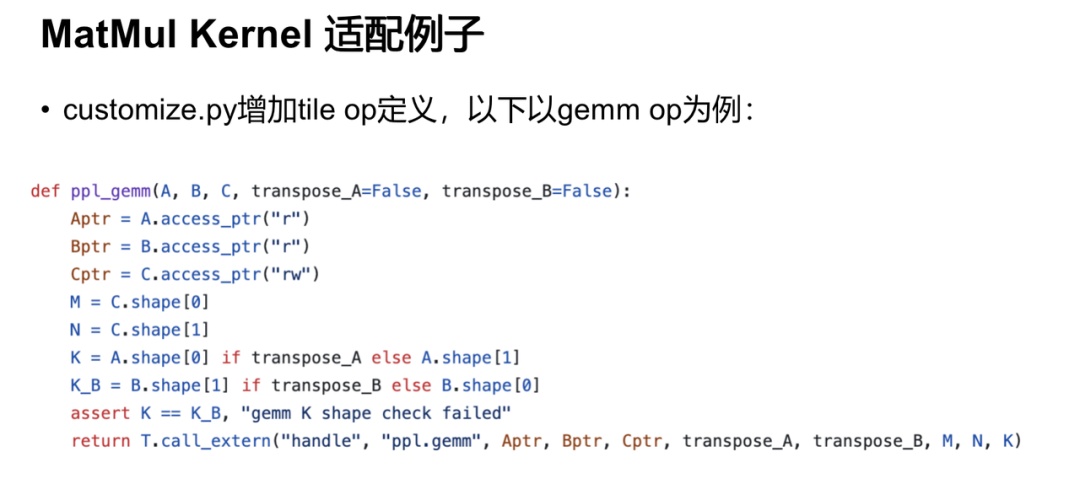

TileLang-TPU的核心工作聚焦三點:前端原語擴展。于 TileLang/language/customize.py 增補自定義 tile op 接口,使 GEMM、RMSNorm、RoPE、SwiGLU 等算子可以以更貼近數學定義的方式表達,并在 Tile-IR 層明確迭代空間、數據復用與流水線切分,減少手寫索引與 bank 沖突的偶然性。

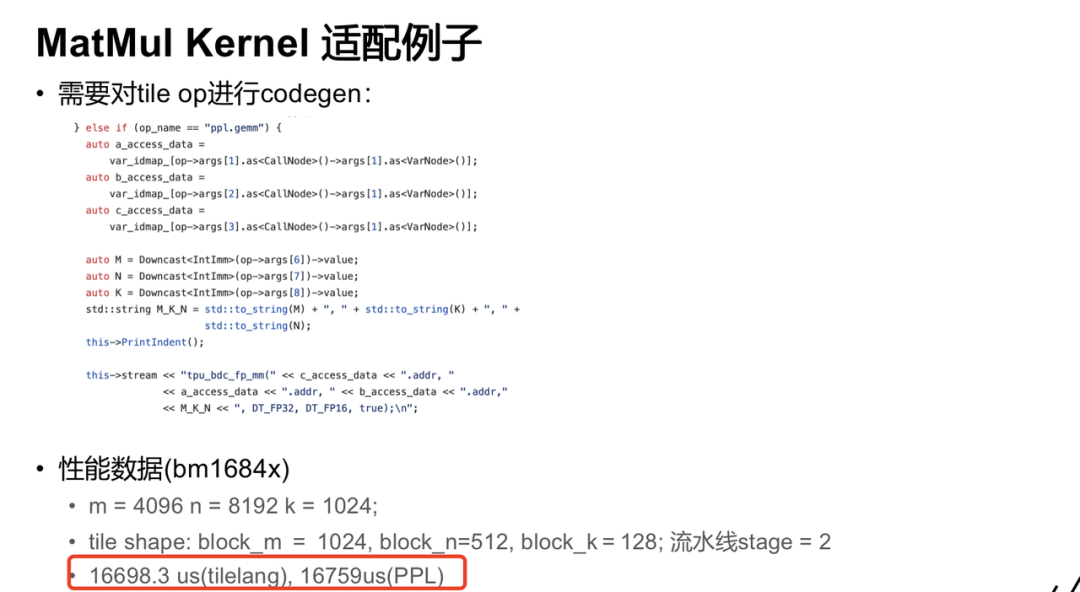

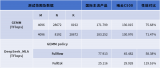

代碼生成映射。于 src/target/codegen_ppl.cc 完成原語到算能 TPU 專用執行單元的映射,將GEMM 一類算子對齊到 BDC 的矩陣乘路徑(如 tpu_bdc_fp_mm.v 等),同時根據設備層級內存模型生成指令序列與局部緩存策略,確保計算與搬運(GDMA)管線化協同。以matmul在BM1684x上的計算為例,使用TileLang撰寫的算子跟PPL手寫算子性能持平,代碼更加簡潔。

運行棧整合。生成的 device 側 C 代碼與元信息并入 PPL 體系,完成 kernel 注冊、調度入口與形參綁定,保證 host 側裝載、形狀檢查、dtype/stride 處理與 device 側執行一致;必要時補充 tiling 規則與長短軸對齊策略,以兼顧大shape與批處理場景。當前已實現TileLang 前端 → PPL/TPU 設備端 C → PPL 運行期可執行的完整鏈路,關鍵算子具備可對齊的性能基線與可定位的優化,便于后續按模型族進行系統化補全與壓測。

持續開源 | 一次改寫多處復用

TileLang開源的價值不止于“又多了一個后端”,更在于“少了成倍的重復移植”。在國產芯片生態日益多樣化的現實下,統一的 tile 級前端抽象能把算子資產沉淀在可組合、可驗證的語義層;遷移到新后端時,僅需圍繞 CodeGen 與 runtime 這條窄口補齊映射與 ABI,可繼承既有的表達、調度與測試體系。

這種“前端統一、后端定制”的方式,有機會在工程維度緩解國產芯片的碎片化,讓差異化架構以最小成本共享同一套高質量算子實現與基準。后續開發團隊將優先確保DeepSeek等主流模型鏈路的端到端可用,再面向長尾算子逐步補全,并在流水線深度、訪存回填、緩存復用等細節上持續優化最佳實踐。

TileLang-TPU 正在做開源前的代碼清理與文檔化的工作,它的意義并不在于“多了一個后端”,而在于“少了很多重復”,當同一套算子前端可以映射到更多芯片時,碎片化就不再是阻力,而會成為競爭力,讓不同架構以各自所長服務更大的模型與更廣的場景,而不是把資源消耗在移植與改寫上。

再次感謝來自北大、復旦、山大等高校的研發團隊在TileLang-TPU上所做的前瞻性工作,后續的開源倉庫將附帶清晰的示例與文檔,支持以標準化方式擴展原語、以嚴謹的工程標準實現“一次改寫、多平臺復用”的目標。TileLang-TPU的成功驗證,將進一步加深算能與高校、開源社區的合作深度,為完善國產芯片軟件棧打造一個經典范式。

-

AI

+關注

關注

91文章

40578瀏覽量

302178 -

TPU

+關注

關注

0文章

171瀏覽量

21693 -

DeepSeek

+關注

關注

2文章

837瀏覽量

3352

發布評論請先 登錄

DeepSeek V3.1發布!擁抱國產算力芯片

沐曦股份GPU產品正式接入華佗開源生態

國產算力生態擁抱開源AI智能體:光合組織全國OpenClaw體驗“龍蝦局”正式啟動

摩爾線程正式開源TileLang-MUSA項目

北大團隊最新研究:AI芯片算力提升數倍,能效提升超90倍

中北大學以開源技術鋪就人才與產業共贏之路

東北大學開源鴻蒙技術俱樂部正式揭牌成立

復旦大學探索開源人才發展新模式

沐曦曦云C系列產品已支持TileLang

邊緣計算AI硬件如何接入DeepSeek嗎?需要具備哪些條件?

【「DeepSeek 核心技術揭秘」閱讀體驗】--全書概覽

【「DeepSeek 核心技術揭秘」閱讀體驗】書籍介紹+第一章讀后心得

TPU編程競賽系列|2025中國國際大學生創新大賽產業命題賽道,算能11項命題入選!

擁抱DeepSeek開源生態| 算能TPU接入TileLang,集結北大復旦山大頂尖團隊!

擁抱DeepSeek開源生態| 算能TPU接入TileLang,集結北大復旦山大頂尖團隊!

評論