CDC5801A器件提供從單端參考時鐘 (REFCLK) 到差分輸出對 (CLKOUT/CLKOUTB) 的時鐘乘法和分頻。乘法和分頻端子 (MULT/DIV0:1) 提供倍頻比和分頻比選擇,生成 12.5 MHz 至 500 MHz 的 CLKOUT/CLOUTKB 頻率,時鐘輸入基準 (REFCLK) 范圍為 19 MHz 至 125 MHz。

實施的相位對齊器通過將需要對齊的時鐘饋送到 DLYCTRL 和 LEADLAG 端子,提供了在 CLKOUT/CLKOUTB 和 REFCLK 或系統中的任何其他 CLK 之間進行相位對齊(零延遲)的可能性。

*附件:cdc5801a.pdf

相位對準器還允許用戶以 2.6 mUI(單位間隔)的步長延遲或推進 CLKOUT/CLKOUTB。對于DLYCTRL端子上的每個上升沿,只要LEADLAG端子上存在低電平,輸出時鐘就會延遲2.6 mUI步長。同樣,對于DLYCTRL端子上的每個上升沿,只要LEADLAG端子上存在高電平,輸出時鐘就會提前2.6 mUI步長。該CDC5801A具有故障安全上電初始化狀態機,支持在所有上電條件下正常運行。由于REFCLK和CLKOUT/CLKOUTB之間的相位在上電后是隨機的,因此應用可以在上電時實現自校準例程,以產生特定的相位起始位置,然后再使用DLYCTRL端子上的時鐘對固定延遲進行編程。

根據模式端子 (P0:2) 的選擇,該器件充當旁路相位對準器的乘法器(4、6 或 8),或作為具有可編程延遲和相位對準器功能的乘法器或分頻器。通過選擇端子 (P0:2),用戶還可以繞過相位對準器和 PLL(測試模式),直接在 CLKOUT/CLKOUTB 端子上輸出 REFCLK。通過 P0:2 端子,輸出可以處于高阻抗狀態。該器件具有另一個獨特的功能,即能夠通過改變 V 上的電壓來在 REFCLK 端子上的寬電壓帶下工作DDREF 終端。

該CDC5801A具有故障安全上電初始化狀態機,支持在所有上電條件下正常運行。

CDC5801A器件的特點是在 –40°C 至 85°C 的自由空氣溫度下運行。

特性

- 低抖動時鐘乘法器乘以 x4、x6、x8。輸入頻率范圍(19 MHz 至 125 MHz)。支持150 MHz至500 MHz的輸出頻率

- 故障安全上電初始化

- 低抖動時鐘分頻器 /2、/3、/4。輸入頻率范圍(50 MHz 至 125 MHz)。支持12.5 MHz至62.5 MHz的輸出頻率范圍

- 2.6 mUI 可編程雙向延遲步長

- 500 MHz時典型8 ps相位抖動(12 kHz至20 MHz)

- 500 MHz時典型值為2.1 ps RMS周期抖動(整個頻段)

- 一個單端輸入和一個差分輸出對

- 輸出可驅動LVPECL、LVDS和LVTTL

- 三種電源工作模式,可最大限度地降低功耗

- 低功耗(500 MHz 時典型值為 200 mW)

- 采用收縮小外形封裝 (DBQ) 封裝

- PLL 無需外部元件

- 擴頻時鐘跟蹤能力可降低 EMI

- 應用:視頻圖形、游戲產品、數據通信、電信

- 接受 REFCLK 端子的 LVCMOS、LVTTL 輸入

- 通過對適當的 V 進行編程,在 REFCLK 端子上接受其他單端信號電平

DDREF電壓電平(例如,HSTL 1.5,如果VDD參考 = 1.6 V) - 支持 -40°C 至 85°C 的工業溫度范圍

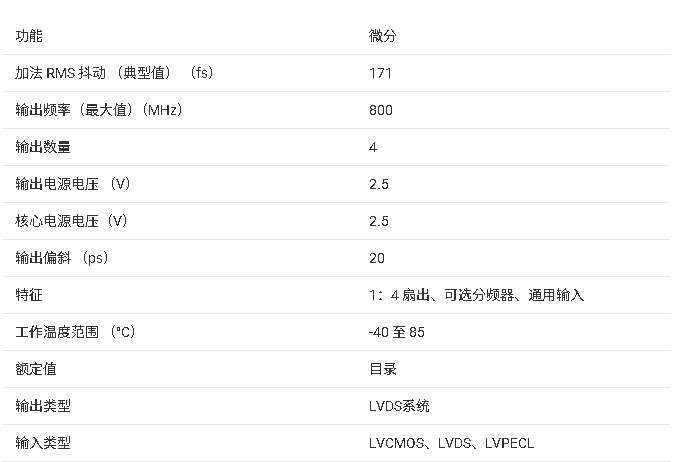

參數

?1. 產品概述?

CDC5801A是德州儀器(TI)推出的高性能時鐘管理芯片,具備以下核心功能:

- ?時鐘倍頻?:支持×4、×6、×8倍頻,輸入頻率19 MHz至125 MHz,輸出頻率150 MHz至500 MHz。

- ?時鐘分頻?:支持÷2、÷3、÷4分頻,輸入頻率50 MHz至125 MHz,輸出頻率12.5 MHz至62.5 MHz。

- ?可編程延遲與相位對齊?:提供2.6 mUI步長的雙向延遲調節,典型相位抖動低至8 ps(12 kHz–20 MHz頻段)。

?2. 關鍵特性?

- ?低功耗設計?:典型功耗200 mW(500 MHz時),支持三種省電模式。

- ?接口兼容性?:支持LVCMOS、LVTTL、LVPECL、LVDS等多種電平標準。

- ?工業級溫度范圍?:-40°C至85°C,適用于嚴苛環境。

- ?封裝形式?:24引腳SSOP(DBQ)封裝,無需外部元件。

?3. 功能模式?

通過控制引腳(P0-P2)可配置以下工作模式:

- ?倍頻/分頻模式?:帶相位對齊和可編程延遲(P0:2=000或001)。

- ?純倍頻模式?:繞過相位對齊器以降低抖動(P0:2=100)。

- ?測試模式?:直接輸出參考時鐘(P0:2=110)。

- ?高阻模式?:關閉輸出(P0:2=01X)。

?4. 電氣特性?

- ?抖動性能?:

- 倍頻模式(500 MHz):典型RMS周期抖動2.1 ps。

- 分頻模式(62.5 MHz):典型RMS周期抖動6.5 ps。

- ?時序參數?:

- 啟動時間(PWRDNB↑至穩定輸出):典型100 μs。

- 時鐘禁用響應時間(STOPB↓):≤5 ns。

?5. 應用場景?

?6. 設計支持?

- 提供功能框圖、時序圖及典型應用電路(如多時鐘相位對齊方案)。

- 詳細引腳定義與真值表(如DLYCTRL/LEADLAG控制延遲方向)。

?7. 生產與可靠性?

- 符合TI標準質保條款,生產數據截至文檔發布日有效。

- 絕對最大額定值:供電電壓-0.5V至4V,工作溫度-40°C至85°C。

-

分頻器

+關注

關注

43文章

536瀏覽量

53352 -

編程

+關注

關注

90文章

3716瀏覽量

97182 -

高電平

+關注

關注

6文章

225瀏覽量

22819 -

時鐘輸入

+關注

關注

0文章

7瀏覽量

2104

發布評論請先 登錄

低抖動高精度時鐘發生器MAX3625B相關資料分享

將系統的時鐘分頻器系數以及PLL的倍頻系數配置好

應用于倍頻電路的預置可逆分頻器設計

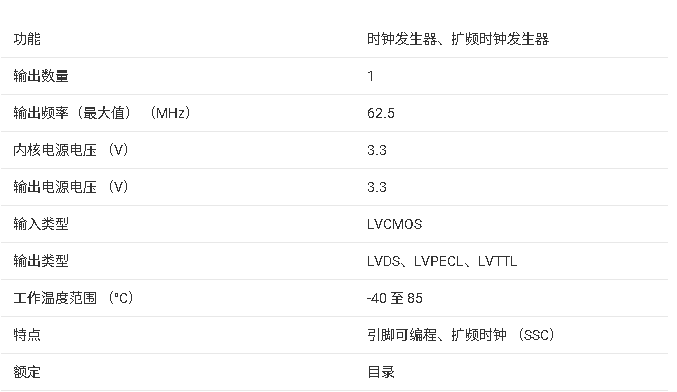

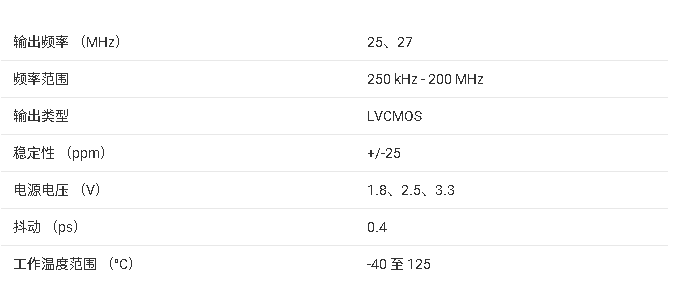

?CDC6C-Q1低功耗LVCMOS輸出BAW振蕩器技術文檔總結

CDC6C 低功耗、低抖動、體聲波 (BAW)、固定頻率 LVCMOS 振蕩器技術文檔總結

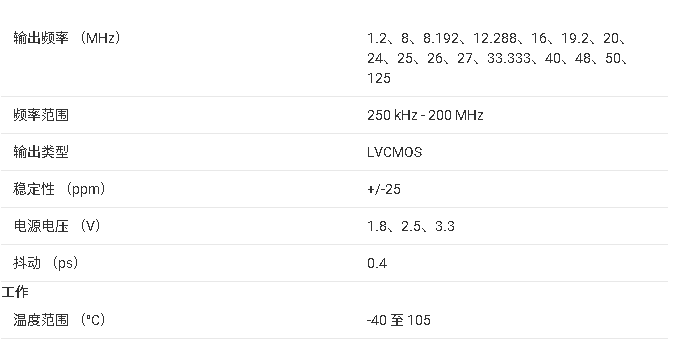

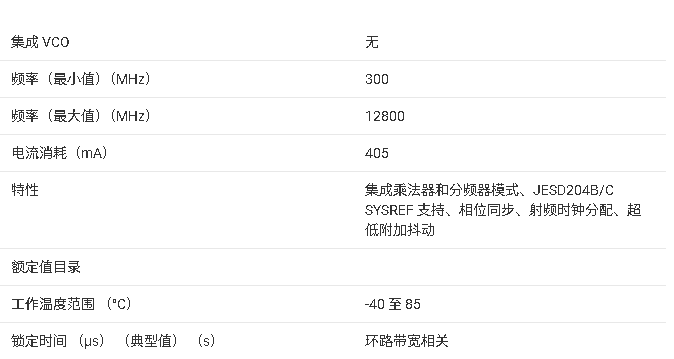

?LMX1204 低噪聲高頻 JESD 緩沖器/乘法器/分頻器技術文檔總結

?CDC5801A低抖動時鐘倍頻/分頻器技術文檔總結

?CDC5801A低抖動時鐘倍頻/分頻器技術文檔總結

評論