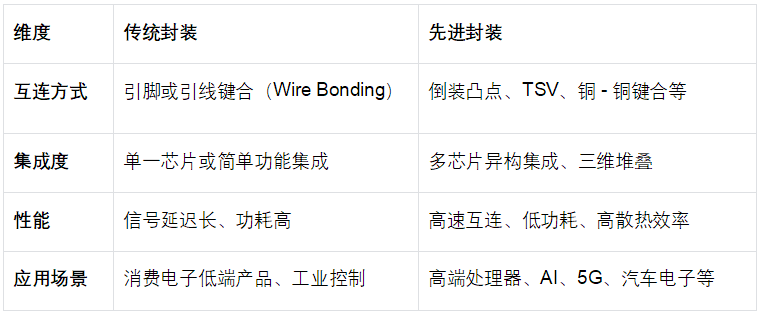

先進封裝通過縮短(I/O)間距與互聯長度,大幅提升 I/O 密度,成為驅動芯片性能突破的關鍵路徑。相較于傳統封裝,其核心優勢集中體現在多維度性能升級與結構創新上:不僅能實現更高的內存帶寬、更優的能耗比與性能表現,還可將芯片厚度做得更薄,同時支持多芯片集成、異質集成及芯片間高速互聯,完美適配當下半導體器件對高密度、高速度、低功耗的需求。在先進封裝的技術體系中,凸塊(Bump)、重布線層(RDL)、硅通孔(TSV)、混合鍵合(Hybrid Bonding)等技術共同構成了實現其性能優勢的關鍵支撐。

隨著半導體技術迭代速度的不斷加快,先進封裝領域正迎來一場深度變革,而RDL在這場變革中脫穎而出,成為先進封裝異質集成的核心基石,持續吸引業界高度關注。作為實現芯片水平方向電氣延伸與互連的核心技術,RDL在 3D/2.5D 封裝集成及晶圓級封裝中發揮著不可替代的作用。其技術原理是通過在芯片表面精準沉積金屬層與相應介電層,構建出符合電路需求的金屬導線,并將原本集中的 I/O 端口重新布局到更開闊的區域,形成高效的表面陣列結構。這一技術創新不僅能大幅減薄芯片間的鍵合厚度、簡化封裝工藝,還能以更緊湊、更高效的方式規劃芯片布局,最終顯著縮小器件的整體面積,為高密度封裝方案提供有力支持。

值得注意的是,光敏聚酰亞胺(PSPI)作為 RDL 圖案化過程中的關鍵材料,其技術路線的演進與下游先進封裝的需求變化高度綁定,直接影響 RDL 技術的性能表現與應用拓展,在先進封裝產業鏈中占據著重要地位。

PSPI 賦能多元先進封裝,適配不同終端應用場景

PART.02

圖1 清晰呈現了PSPI各類先進封裝技術中的應用路徑,及其對應的代表性應用與終端場景。從圖中可見,PSPI 在不同技術路線的先進封裝中均承擔關鍵角色,而各類封裝技術則憑借獨特性能優勢,精準適配多元化的應用需求與終端場景,形成了完整的技術 - 應用 - 終端產業鏈條。

FI - WLP(扇入型晶圓級封裝)具備工藝相對成熟、成本較低且集成度適中的優勢,能助力藍牙 MCU、NOR 閃存、藍牙 SoC 等應用。這些應用對應可穿戴設備、智能手機等終端,FI - WLP 可滿足此類終端對芯片小型化、低功耗且兼具一定性能的需求,讓可穿戴設備更輕薄便攜,為智能手機提供基礎且穩定的無線連接、存儲等功能支撐。FO - WLP/PLP(扇出型晶圓級封裝 / 扇出型面板級封裝)擁有更高集成度、可實現多芯片集成的優點,支撐 AP(手機)、AP ( 手表)、PMIC 等眾多應用,覆蓋智能手機、平板電腦、基站等終端。對于智能手機、平板電腦,其能提升芯片運算與多任務處理能力,讓設備運行更流暢;在基站等通信終端中,可保障芯片在復雜環境下長時間穩定運行,增強通信的可靠性與效率。 2.5D 和 3D 封裝技術則憑借超高集成度、能實現芯片間高密度互連的特性,為 AI 芯片、服務器 CPU、DRAM 等高性能應用提供支持,賦能服務器、數據中心、人工智能、汽車電子等終端。在人工智能領域,可助力芯片實現強大的運算能力與高效散熱,滿足海量數據處理需求;在汽車電子,尤其是輔助駕駛芯片應用中,能增強芯片可靠性與安全性,為駕駛安全保駕護航;對于服務器和數據中心,可提升數據處理與存儲的速度及效率,保障業務的高效開展。

2.5D 和 3D 封裝技術則憑借超高集成度、能實現芯片間高密度互連的特性,為 AI 芯片、服務器 CPU、DRAM 等高性能應用提供支持,賦能服務器、數據中心、人工智能、汽車電子等終端。在人工智能領域,可助力芯片實現強大的運算能力與高效散熱,滿足海量數據處理需求;在汽車電子,尤其是輔助駕駛芯片應用中,能增強芯片可靠性與安全性,為駕駛安全保駕護航;對于服務器和數據中心,可提升數據處理與存儲的速度及效率,保障業務的高效開展。

未來半導體封裝PSPI發展技術路線

PART.03

在先進封裝技術向高密度、高性能、高可靠性持續演進的過程中,不同應用場景(如2.5D/3D 封裝、扇出型晶圓級封裝等)對核心材料PSPI性能要求呈現顯著差異化特征。圖 2 可見,為適配多元化封裝場景的功能需求,PSPI 的技術發展正聚焦三大核心方向:微細化、低溫化、低介電,三者共同構成未來 PSPI 材料的關鍵技術突破路徑。

01 // RDL 微細化技術演進、企業方案及 PSPI 適配創新

首先,當前,4 層 RDL 技術已進入大規模成熟應用階段,良率穩定達到 99% 的高水平,憑借可靠的性能與成本優勢,能夠覆蓋全球約 85% 的半導體封裝需求,成為消費電子、物聯網等中高端封裝場景的主流方案。但隨著AI 芯片、HBM 存儲、高端服務器 CPU 等高性能場景對互連密度、信號傳輸效率的要求持續提升,RDL 微細化技術正加速向更高層數、更細線寬 / 線距(L/S)突破,具體演進路徑清晰可見:短期(2023-2024 年):頭部廠商已實現 2/2μm L/S 的 RDL 技術量產,支撐 2.5D 封裝、中高端 FO-WLP 等工藝需求;中期(2025-2026 年):L/S 將進一步縮減至 1/1μm,層數從 4 層提升至 6-8 層,以適配 Chiplet 異質集成、高帶寬 HBM3e/HBM4 堆疊等場景;長期(2027 年以后):L/S 有望突破 0.5/0.5μm,層數突破 8 層甚至達到 12 層以上,滿足 3D IC 高密度堆疊、超高速信號傳輸的極致需求。

表1:各企業的 RDL 技術方案與進展

編號 | 企業名稱 | 封裝技術名稱 | RDL情況 |

1 | 臺積電 | CoWoS-R | 采用InFO 技術和 RDL 中介層實現 HBM 和 SoC 集成,RDL 中介層有多達 6 個銅層用于布線,最小 4μm 間距(2μm 線寬 / 間距) |

CoWoS-L | 結合CoWoS-S 和 InFO 優點,使夾層與 LSI 芯片互連,通過 RDL 層進行電源和信號傳輸,LSI 芯片通過多層亞微米銅線實現芯片間高布線密度互連 | ||

InFO | 具有高密度RDL,可實現各種應用的高密度互連和性能,InFO_oS 有更高密度的 2/2μm RDL 線寬 / 間距,可提供多達 14 個重新分布層;Info_LSI 技術使用硅橋(RDL L/S:0.4/0.4μm)以及 RDL 層代替整塊硅 | ||

2 | I-CubeE | 采用集成硅橋的RDL 中介層,能利用嵌入 FO-PLP 中間并用作接口的硅橋的小 L/S 優勢,實現硅芯片之間的高效連接 | |

R-Cube | 通過高密度RDL 實現邏輯到邏輯和邏輯到 HBM 模塊的連接 | ||

2.5D | 配備2/2um 的 L/S,以及集成了 4 個 HBM 模塊的大型中介層(約為 1600mm2) | ||

3 | ASE 集團 | VIPack | 利用先進的重布線層制程等技術,實現超高密度和性能設計的三維異質封裝結構 |

FOCoS-CF | 具備高層數(>6 層)和細線 / 間距(L /S = 1μm/1μm),由兩個面朝下的 ASIC 小芯片組成,通過 Cu 過孔直接與 RDL 連接,Si 芯片和扇出 RDL (L/S 2/2 um) 之間沒有微凸塊 | ||

FOCoS-CL | 具備高層數(>6 層)和細線 / 間距(L /S = 1μm/1μm),由并排配置的三個小芯片(1 個 ASIC 芯片和 2 個 HBM)構建而成,ASIC 芯片和 2 個 HBM 通過 RDL (L/S 2/2 um) 和 Cu 微凸塊連接 | ||

FOCoS-Bridge | 一種2.5D 封裝,具有 ASIC 和 HBM 兩個芯片,兩者通過嵌入 RDL 的硅橋芯片實現超細間距互連,硅橋芯片 (L/S 0.6/0.6 um) 嵌入扇出 RDL 層 (L/S 10/10 um),用于在 ASIC 和 HBM 之間建立連接 | ||

4 | 日月光 | 無 | RDL 層數大于 6 層,L/S 為 1 - 1.5μm |

5 | 安靠科技 | SWIFT /HDFO | SWIFT 是最先進的高密度扇出結構,可實現 2/2 μm 線 / 間距特性;HDFO 基于 SWIFT 開發,保持了高密度連線,出色的信號質量,無需 TSV |

SLIM | 利用前道代工,在硅片表面的無機介質層上制作1μm,甚至亞微米金屬布線,L/S 小于 2um | ||

6 | 長電科技 | XDFOI | 可實現線寬和線距低至2 微米的多個重新分布層 (RDL),將部分分布層轉移到 RSI 基板上,利用 RSI 線寬和線距縮小至 2 微米的優勢,減少芯片互連間距 |

7 | 通富微電 | 2.5D/3D | 基于ChipLast 工藝的 Fan-out 技術,實現了 5 層 RDL 超大尺寸封裝(65×65mm);FO 系列中重分布 L/S 為 2/2um |

8 | 華天科技 | eSiFO | 在高密度晶圓級扇出型封裝技術方面,L/S 為 2/2um,RDL Layer 為 6 P5M,封裝尺寸 15×15mm |

eSinC | 在高密度晶圓級扇出型封裝技術方面,L/S 為 2/2um,RDL Layer 為 6 P5M,封裝尺寸最大可以達到 40mm×40mm | ||

9 | 甬矽電子 | / | 目前最小線寬可達5um,最小線間距可達 5um,運用于量產產品上的細線寬為最小線寬 8um,最小線間距 8um |

10 | 云天半 導體 | 玻璃通孔技術 | 用大馬士革工藝在玻璃基表面制備三層RDL 堆疊,采用無機薄膜材料作為介質層進行制備,實現更細更高精度的金屬布線 |

來源:公開資料、光界咨詢(OPTO)整理

RDL 微細化技術的推進,對作為關鍵絕緣與圖案化材料的 PSPI 提出了場景化適配要求,不同封裝類型的核心需求差異顯著:應用處理器(AP)的 FO-WLP/PLP 封裝聚焦小型化與高 I/O 密度,對 PSPI 的高分辨率性能要求突出。需 PSPI 在光刻過程中精準實現微細線路成型,保障 2-4μm L/S 線路的邊緣粗糙度控制在較低水平,避免因線路缺陷導致的信號損耗或短路問題;由于2.5D 集成封裝需同時實現芯片間高密度互連與高速信號傳輸,PSPI 需兼具微細線路加工能力與低介電特性。一方面需支持 1-2μm L/S 的精細布線,確保 RDL 互連密度;另一方面需將介電常數(Dk)控制在 3.0 以下,降低信號延遲與串擾,保障高頻場景下的信號完整性。為匹配RDL 微細化的技術節奏,PSPI 材料與制程工藝正同步開展多維度創新:材料類型與規格適配方面,負性PSPI 因具備更優異的光刻分辨率、更低的線寬偏差,已成為微細化場景的核心開發方向,研發重點集中在提升其在 1/1μm 及以下 L/S 場景的圖案化精度與固化后力學穩定性;同時,非感光型材料的開發也聚焦 “耐久性 + 微細化適配” 雙重目標,通過分子結構改性,在支持 1μm 以下 L/S 的同時,提升耐濕熱、抗熱沖擊性能,滿足長期可靠性需求。

02// 低溫PSPI需求及旭化成市場格局與產能挑戰

傳統PSPI 固化溫度在 300-350℃,需專用耐高溫設備,成本與能耗高。高溫還會使金屬互連材料與 PI 反應,影響電氣性能,因熱膨脹系數差異致晶圓問題,制約封裝精細發展,威脅芯片可靠性,難以契合高集成封裝需求。先進封裝如FO-WLP、2.5D/3D 興起,對 PSPI 性能提出新要求。FO-WLP 中,EMC 耐溫低于 250℃,PSPI 固化溫度需同步降。2.5D/3D 封裝,芯片堆疊多、互連密,PSPI 要在低溫下實現高精度光刻與低應力固化,降低 PSPI 固化溫度成關鍵難題。低溫固化PSPI 是先進封裝升級必然,其能解決高溫對結構和材料的損傷,適配高端場景。目前,低溫固化溫度170℃產品量產,更低溫產品研發正推進。日本旭化成作為低溫PSPI 領域的絕對龍頭企業,據光界咨詢(OPTO)數據顯示,其在全球半導體封裝用低溫 PSPI 市場中占據約 50% 的份額,行業地位顯著。然而,隨著AI 芯片、HBM 存儲等先進封裝需求的爆發式增長,市場對低溫 PSPI 的需求同步激增,旭化成卻面臨產能難以匹配需求的困境。2025 年間有消息傳出,因產能缺口,旭化成向部分客戶發出通知,其核心產品 PIMEL 系列 PSPI 存在斷供風險。盡管旭化成已宣布啟動擴產計劃以緩解供需矛盾,但受限于產能建設周期、設備調試等因素,短期內產能釋放有限,未來仍存在因需求持續超預期而再次出現斷供的可能性。

03// PSPI 低介電性能的場景需求與技術演進

在RDL應用場景中,PSPI的低介電性能已成為保障信號傳輸效率的關鍵指標,不同場景對介電損耗(Df)的要求呈現明確的梯度化特征:針對AiP應用,為減少高頻信號在傳輸過程中的損耗,需 PSPI 具備低介電特性,確保天線與芯片間信號傳遞的完整性,適配 5G、毫米波等高頻通信需求;在 RDL 應用場景,當前主流要求 PSPI 的介電損耗(Df)達到 0.004~0.005 等級,以滿足芯片間高密度互連的信號穩定性需求。隨著半導體技術向高速傳輸升級,低介電性能的要求將進一步嚴苛。為適配SerDes 200Gbps 以上的高速傳輸場景,行業正積極探討采用 Df 為 0.002 等級的 PSPI 產品;從長期技術演進來看,預計未來還將涌現對 Df 低至 0.0015 以下的 PSPI 產品需求,以突破更高速度信號傳輸的介損瓶頸,支撐高端服務器、AI 芯片等高性能場景的發展。

本土企業半導體封裝PSPI開發動向

PART.04

應用端相關行業專家表示,光敏聚酰亞胺國產化在基礎物性上部分可與進口材料對標,甚至部分單項指標更優,但實際工程驗證推進遲緩,尚未大規模量產。原因之一半導體領域對新材料態度保守,客戶端接受度低;質量管理體系有待完善,材料品質穩定性不足;且材料推出時間晚,驗證機會少,工藝條件也需優化。破局之策為產業鏈上下游協同推進、合作共贏;技術創新,發展有特色的材料和工藝體系。

在產品技術開發方面,國內相關企業持續布局,以波米科技為代表,其技術聚焦于功率半導體器件制造和半導體先進封裝用高性能聚酰亞胺材料領域。半導體封裝方面其PSPI 產品正朝著 “高溫→低溫→超低溫” 固化溫度、“Bumping→RDL (4P4M)→RDL (≥6P6M)” 應用場景的 “三級跳” 目標邁進。

其中,高溫固化型已批量供應,用于先進封裝 Bumping 技術;低溫固化型通過下游頭部客戶認證,用于 RDL (4P4M) 技術,產品基本定型;超低溫固化型處于研發階段,膜性能及光刻工藝達標,其研發和產業化入選相關科研項目,以滿足未來 2.5D/3D 封裝、Chiplet 等領域 RDL (≥6P6M) 技術需求。

-

半導體

+關注

關注

339文章

30725瀏覽量

264046 -

驅動芯片

+關注

關注

14文章

1643瀏覽量

57955 -

先進封裝

+關注

關注

2文章

533瀏覽量

1026

發布評論請先 登錄

未來半導體先進封裝PSPI發展技術路線趨勢解析

未來半導體先進封裝PSPI發展技術路線趨勢解析

評論