該CDCE72010是一款高性能、低相位噪聲和低偏斜時鐘同步器,可將VCXO(壓控晶體振蕩器)或VCO(壓控振蕩器)頻率同步到兩個參考時鐘之一。時鐘路徑是完全可編程的,為用戶提供了高度的靈活性。以下關系適用于分隔線:

頻率(VCXO_IN 或 AUX_IN)/頻率(PRI_REF 或 SEC_REF)= (PN)/(RM)

VC(X)O_IN時鐘通過選擇外部VC(X)O和環路濾波器組件,工作頻率高達1.5GHz。PLL環路帶寬和阻尼系數可以調整以滿足不同的系統要求。

*附件:cdce72010.pdf

該CDCE72010可以鎖定到兩個參考時鐘輸入(PRI_REF和SEC_REF)之一,并支持頻率保持模式,以實現故障安全和系統冗余。CDCE72010的輸出是用戶可定義的,可以是多達 10 個 LVPECL/LVDS 輸出或多達 20 個 LVCMOS 輸出的任意組合。內置同步鎖存器確保所有輸出同步,實現極低的輸出偏斜。

所有器件設置,包括輸出信號、分壓器值選擇、輸入選擇等,都可通過SPI(4線串行外設接口)進行編程。SPI 允許單獨控制設備設置。

該器件在3.3V環境中工作,工作溫度范圍為–40°C至+85°C。

該CDCE72010采用 64 引腳無鉛“綠色”塑料四方扁平封裝,帶有增強型底部導熱墊以實現散熱。德州儀器 (TI) 的封裝代號為 RGC (S-PQFP-N64)。

特性

- 高性能 LVPECL、LVDS、LVCMOS PLL 時鐘同步器

- 兩個參考時鐘輸入(初級和次級時鐘),用于冗余

支持,可手動或自動選擇 - 接受兩個高達 500MHz 的差分輸入(LVPECL 或 LVDS)基準電壓源

(或兩個高達 250MHz 的 LVCMOS 輸入)作為 PLL 基準電壓源 - VCXO_IN時鐘與兩個參考時鐘之一同步

- VCXO_IN頻率高達 1.5GHz (LVPECL),

LVDS 為 800MHz,LVCMOS 電平信令為

250MHz - 輸出可以是LVPECL、LVDS和LVCMOS

的組合(多達10個差分LVPECL或LVDS輸出或多達

20個LVCMOS輸出),輸出9可以轉換為

輔助輸入,作為第二個VC(X)O。 - 輸出分頻器可選擇在每個輸出上單獨分配 1、2、3、4、5、6、8、10、

12、16、18、20、24、28、30、32、36、40、42、48、50、56、60、64、70

或 80 最多 8 個分頻器。(除輸出 0 和 9 外

,輸出 0 跟隨輸出 1 分壓器,輸出 9

跟隨輸出 8 分壓器) - SPI可控器件設置

- 通過SPI接口進行單獨的輸出使能控制

- 集成片上非易失性存儲器 (EEPROM),無需向器件施加高壓即可存儲設置

- 可選配置引腳,可在存儲在EEPROM中的兩個默認設置

之間進行選擇 - 低 PLL 環路帶寬的高效抖動清除

- 極低相位噪聲PLL內核

- 可編程相位偏移(輸入基準到輸出)

- 200μA至3mA的寬電荷泵電流范圍

- 預設電荷泵至V

CC_CP/2用于快速設置VC(X)O中心頻率,通過SPI總線控制 - SERDES 啟動模式(取決于 VCXO 范圍)

- 輔助輸入:輸出 9 可作為第二個 VCXO 輸入來驅動

所有輸出或用作 PLL 反饋信號 - RESET或HOLD輸入引腳,用作復位或保持功能

- REFERENCE SELECT用于在主參考時鐘和次參考

時鐘之間進行手動選擇 - POWER DOWN (PD) 將設備置于待機模式

- 模擬和數字 PLL 鎖定指示器

- 用于單端輸入信號的內部生成的VBB偏置電壓

- 由HOLD引腳或SPI總線激活頻率保持模式,以改善

故障安全作 - 輸入到所有輸出偏斜控制

- 每個輸出分頻器的每個輸出的單獨偏斜控制

- 封裝在QFN-64封裝中

- ESD保護超過2kV HBM

- 工業溫度范圍為 –40°C 至 85°

參數

方框圖

?1. 產品概述?

CDCE72010是德州儀器(TI)推出的一款高性能時鐘同步器、抖動清除器和時鐘分配器,支持多種時鐘輸入和輸出配置,適用于高端電信、無線通信及精密測試設備。

?2. 關鍵特性?

- ?輸入支持?:

- 2路參考時鐘輸入(主/備),支持手動或自動切換。

- 支持差分輸入(LVPECL/LVDS,最高500MHz)或單端輸入(LVCMOS,最高250MHz)。

- ?輸出配置?:

- 最多10路差分輸出(LVPECL/LVDS)或20路單端輸出(LVCMOS)。

- 輸出分頻器可獨立配置,支持1至80的分頻比。

- ?靈活控制?:

- 通過SPI接口編程控制,支持非易失性存儲器(EEPROM)存儲配置。

- 支持頻率保持模式(Hold-Over),提升系統冗余性。

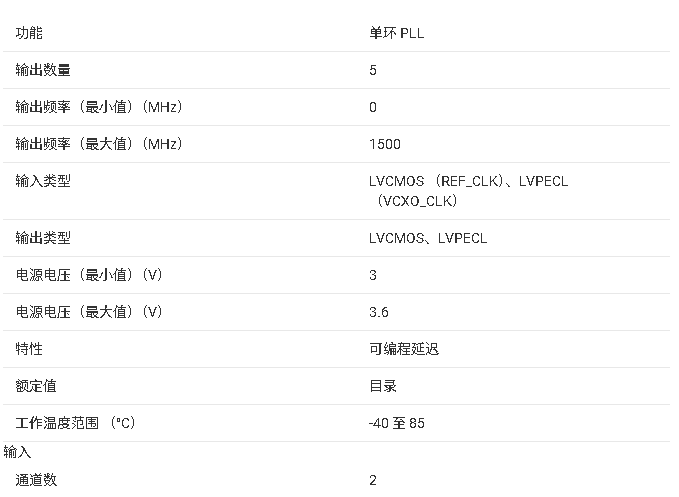

?3. 技術參數?

- ?頻率范圍?:

- VCXO輸入頻率:最高1.5GHz(LVPECL)、800MHz(LVDS)、250MHz(LVCMOS)。

- 輸出頻率:支持分頻后的多種頻率組合。

- ?抖動性能?:低相位噪聲PLL核心,支持高效抖動清除。

- ?工作溫度?:工業級(-40°C至85°C)。

?4. 應用場景?

- 高端電信設備時鐘分配。

- 無線基站時鐘同步。

- 高精度測試儀器時鐘管理。

?5. 封裝與接口?

- 64引腳QFN封裝,帶底部散熱焊盤。

- 支持SPI接口配置,提供引腳控制模式(CD模式)。

?6. 設計支持?

-

可編程

+關注

關注

2文章

1328瀏覽量

41525 -

分配器

+關注

關注

0文章

213瀏覽量

27400 -

晶體振蕩器

+關注

關注

9文章

749瀏覽量

33353 -

清除器

+關注

關注

0文章

56瀏覽量

6105 -

同步器

+關注

關注

1文章

117瀏覽量

15676

發布評論請先 登錄

CDCE72010時鐘頻率問題

為什么CDCE72010時鐘頻率增加3/2會導致DAC中產生的正弦波頻率降低2/3?

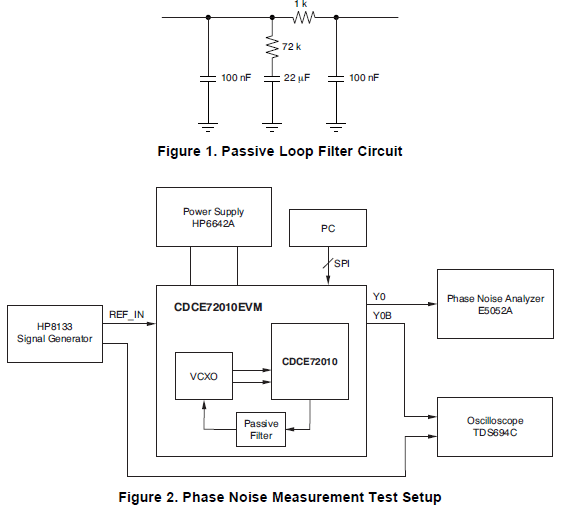

CDCE72010抖動清理器和同步器PLL器件上獲取的相位噪聲數據的資料概述

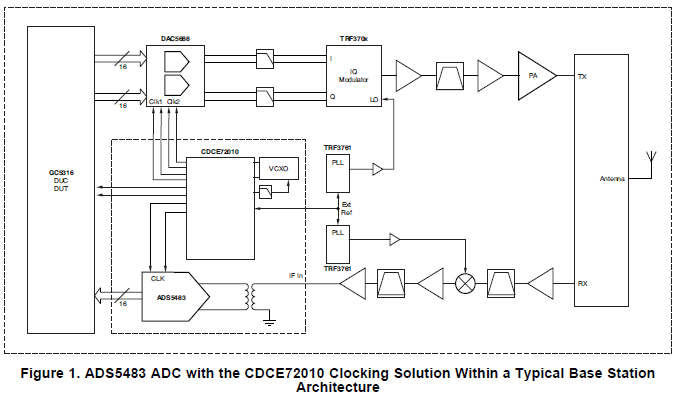

高速ADC設備使用的CDCE72010時鐘合成器芯片的詳細資料概述

CDCE72010時鐘合成器芯片作為高速模數轉換器時鐘信號的解決方案

?CDCE72010 高性能時鐘同步器、抖動清除器和時鐘分配器總結

?CDCE72010 高性能時鐘同步器、抖動清除器和時鐘分配器總結

評論