該CDCM61002是一款高度通用的低抖動頻率合成器,可從低頻晶體或LVCMOS輸入生成兩個低抖動時鐘輸出,可在低壓正發射極耦合邏輯(LVPECL)、低壓差分信號(LVDS)或低壓互補金屬氧化物半導體(LVCMOS)輸出之間進行選擇,適用于各種有線和數據通信應用。該CDCM61002具有板載PLL,只需通過控制引腳即可輕松配置。整體輸出隨機抖動性能小于 1ps、RMS(從 10 kHz 到 20 MHz),使該器件成為 SONET、以太網、光纖通道和 SAN 等要求苛刻應用的完美選擇。該CDCM61002采用小型32引腳、5mm×5mm QFN封裝。

*附件:cdcm61002.pdf

該CDCM61002是一款高性能、低相位噪聲、全集成壓控振蕩器(VCO)時鐘合成器,具有兩個通用輸出緩沖器,可配置為與LVPECL、LVDS或LVCMOS兼容。每個通用輸出也可以轉換為兩個LVCMOS輸出。此外,LVCMOS 旁路輸出時鐘可在輸出配置中提供,有助于晶體負載,以實現精確所需的輸入頻率。它有一個完全集成、低噪聲、基于LC的VCO,工作頻率范圍為1.75 GHz至2.05 GHz。

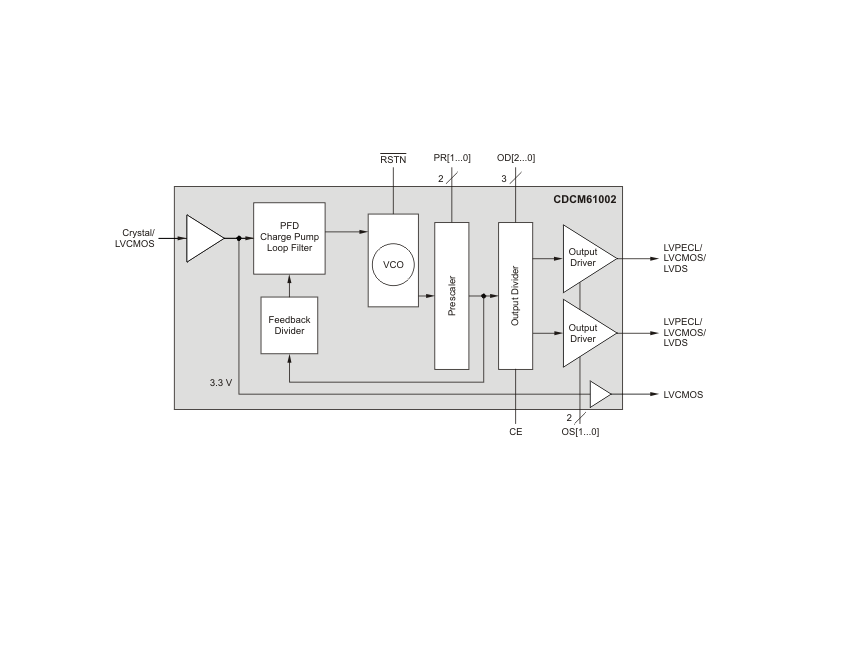

鎖相環 (PLL) 使 VCO 相對于輸入同步,輸入可以是低頻晶體。輸出共享一個來自VCO內核的輸出分壓器。所有器件設置都通過控制引腳結構進行管理,該結構有兩個控制預分頻器和反饋分頻器的引腳,三個控制輸出分頻器的引腳,兩個控制輸出類型的引腳,以及一個控制輸出使能的引腳。每當PLL設置(包括輸入頻率、預分頻器分頻器或反饋分頻器)發生變化時,都必須通過Reset控制引腳發出復位(器件復位為低電平有效)。復位啟動 PLL 重新校準過程以確保 PLL 鎖定。當器件處于復位狀態時,輸出和分頻關閉。

輸出頻率(f 外 )與輸入時鐘的頻率成正比(f 在 ).反饋分頻器、輸出分頻器和VCO頻率集f外關于 f 在 .有關常見有線和數據通信應用程序的配置設置,請參閱。對于其他應用,用于計算所需輸出所需的精確晶體振蕩器頻率。

通過使用控制引腳,可以從 1、2、3、4、6 或 8 中選擇輸出分壓器。反饋分頻器和預分頻器分頻器組合可以分別從 25 和 3、24 和 3、20 和 4 或 15 和 5 中進行選擇,也可以使用控制引腳。顯示了CDCM61002的高級框圖。

該器件在3.3 V電源環境中工作,工作溫度范圍為–40°C至+85°C。

特性

- 一個晶體/LVCMOS基準輸入,包括24.8832 MHz、25 MHz和

26.5625 MHz - 輸入頻率范圍:21.875 MHz 至

28.47 MHz - 片上VCO工作頻率范圍為1.75 GHz至2.05 GHz

- 2 個輸出可用:

- 引腳可選擇 LVPECL、LVDS 或 2-LVCMOS;工作電壓為 3.3 V

- 提供LVCMOS旁路輸出

- 輸出頻率可通過單個輸出分頻器的 /1、/2、/3、/4、/6、/8 選擇

- 支持常見的 LVPECL/LVDS 輸出頻率:

- 62.5 兆赫、74.25 兆赫、75 兆赫、77.76 兆赫、100 兆赫、106.25 兆赫、125 兆赫、

150 兆赫、155.52 兆赫、156.25 兆赫、159.375 兆赫、187.5 兆赫、200 兆赫、212.5 兆赫、

250 兆赫、311.04 兆赫、312.5 兆赫、622.08 兆赫、625 兆赫

- 62.5 兆赫、74.25 兆赫、75 兆赫、77.76 兆赫、100 兆赫、106.25 兆赫、125 兆赫、

- 支持常見的LVCMOS輸出頻率:

- 62.5 兆赫、74.25 兆赫、75 兆赫、77.76 兆赫、100 兆赫、106.25 兆赫、125 兆赫、

150 兆赫、155.52 兆赫、156.25 兆赫、159.375 兆赫、187.5 兆赫、200 兆赫、212.5 兆赫、

250 兆赫

- 62.5 兆赫、74.25 兆赫、75 兆赫、77.76 兆赫、100 兆赫、106.25 兆赫、125 兆赫、

- 輸出頻率范圍:43.75 MHz 至 683.264 MHz

- 內部PLL環路帶寬:400 kHz

- 高性能 PLL 內核:

- 相位噪聲通常為–146 dBc/Hz,5 MHz失調,625 MHz LVPECL輸出

- 隨機抖動通常為 0.509 ps,RMS(10 kHz 至 20 MHz),適用于 625 MHz LVPECL 輸出

- 輸出占空比校正至 50% (± 5%)

- LVPECL輸出上的低輸出偏斜為20 ps

- 使用控制引腳進行分頻器編程:

- 兩個引腳,用于預分頻器/反饋分頻器

- 三個用于輸出分壓器的引腳

- 兩個用于輸出選擇的引腳

- 提供芯片使能控制引腳

- 3.3V 內核和 I/O 電源

- 工業溫度范圍:–40°C 至 +85°C

- 5mm × 5mm、32引腳、QFN (RHB) 封裝

- ESD 保護超過 2 kV (HBM)

參數

方框圖

?1. 產品概述?

CDCM61002是德州儀器(TI)推出的高性能、低抖動時鐘發生器,集成電壓控制振蕩器(VCO),支持多種輸出配置(LVPECL/LVDS/LVCMOS)。主要特性包括:

- ?輸入頻率范圍?:21.875 MHz至28.47 MHz(支持晶體/LVCMOS參考輸入)。

- ?VCO頻率范圍?:1.75 GHz至2.05 GHz。

- ?輸出頻率范圍?:43.75 MHz至683.264 MHz(通過分頻器可調)。

- ?低抖動性能?:隨機抖動典型值0.509 ps(RMS,10 kHz–20 MHz)。

- ?輸出類型?:2路可配置輸出(LVPECL/LVDS/2-LVCMOS)和1路LVCMOS旁路輸出。

?2. 關鍵特性?

- ?靈活配置?:通過控制引腳設置分頻比(/1至/8)、輸出類型及使能狀態。

- ?低相位噪聲?:典型值-146 dBc/Hz(625 MHz LVPECL輸出,5 MHz偏移)。

- ?應用場景?:SONET、以太網、光纖通道、SATA、HDTV等高速數據通信系統。

- ?封裝與工作條件?:5 mm × 5 mm 32引腳QFN封裝,工業級溫度范圍(-40°C至+85°C)。

?3. 功能模塊?

- ?PLL核心?:集成400 kHz帶寬鎖相環,支持快速鎖定。

- ?VCO校準?:上電或復位時自動校準,確保頻率穩定性。

- ?電源管理?:3.3 V供電,內置LDO穩壓器,需外接10 μF電容(REG_CAP1/2引腳)。

?4. 設計注意事項?

- ?熱管理?:需將封裝底部散熱焊盤焊接至PCB以降低結溫。

- ?電源濾波?:建議使用鐵氧體磁珠隔離模擬與數字電源,減少噪聲干擾。

- ?輸出端接?:

- ?LVPECL?:150 Ω終端電阻至VCC-2 V。

- ?LVDS?:100 Ω差分終端。

- ?LVCMOS?:串聯22 Ω電阻匹配傳輸線阻抗。

?5. 典型配置示例?

- ? 輸入25 MHz,輸出312.5 MHz(LVPECL) ?:功耗約432.3 mW(含外部電阻損耗)。

- ? 輸入26.5625 MHz,輸出212.5 MHz(LVCMOS) ?:功耗約405.24 mW(驅動5 pF負載)。

?6. 文檔附加信息?

?結論?

CDCM61002是一款高集成度、低抖動的時鐘解決方案,適用于對時序要求嚴苛的通信和數據處理系統,其靈活的配置和優異的性能使其成為替代傳統晶體振蕩器的理想選擇。

-

合成器

+關注

關注

0文章

316瀏覽量

27877 -

pll

+關注

關注

6文章

981瀏覽量

138156 -

數據通信

+關注

關注

2文章

526瀏覽量

35090 -

時鐘發生器

+關注

關注

1文章

306瀏覽量

70052 -

LVCMOS

+關注

關注

1文章

142瀏覽量

11994

發布評論請先 登錄

請問CDCM61002配置出來的時鐘有偏差怎么解決?

評估低抖動PLL時鐘發生器的電源噪聲抑制性能

CDCM61004四路輸出、集成VCO、低抖動時鐘發生器數據表

CDCM61002兩路輸出、集成VCO、低抖動時鐘發生器數據表

?CDCM9102低噪聲雙通道100MHz時鐘發生器技術文檔總結

?CDCM61002 低抖動時鐘發生器技術文檔總結

?CDCM61002 低抖動時鐘發生器技術文檔總結

評論