9月11 日,D&R IP-SoC Days China 2025在上海淳大萬麗酒店舉辦。作為D&R重要合作伙伴,晟聯科攜112G SerDes、PCIe 6.0及16G UCIe 三大高速接口 IP及解決方案亮相,并發表主題演講,全面展示其在高性能計算、IOD 等領域的創新應用。

演講直擊:超節點崛起,IOD成破局關鍵

晟聯科專家以《“戰國時代” Scale-up 生態下的高速互聯接口 IP 方案》為題,從生態趨勢、IOD 價值到產品落地展開分享,引發全場關注。

當前 AI 算力需求爆發,傳統架構面臨 “單節點擴展受限、多芯片通信損耗大” 等瓶頸,超節點架構成為行業共識 —— 通過三大核心能力構建 Scale-up 生態 “性能底座”:

· 高帶寬域構建:64 卡組網實現多 GPU / 計算節點高密度互聯,破解數據傳輸瓶頸;

· 無損網絡保障:集成 CBFC/PFC/LLR 技術,丟包率每降低 1%,模型訓練推理效率提升 10%;

· 超低延遲突破:端到端延遲控制在 500ns 左右,大幅提升訓練與推理效率。

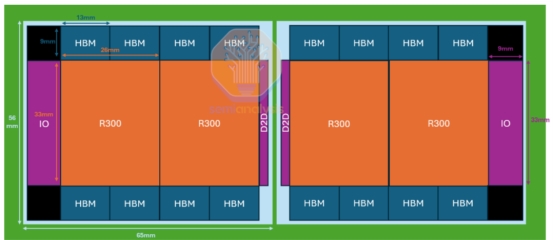

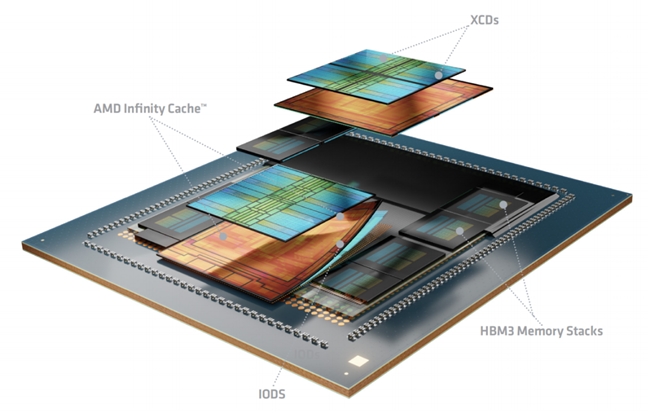

然而,國內外廠商自研協議(UALink、騰訊 ETH-X、移動OISA、英偉達 NVLink 等)并存導致接口不統一,IOD 架構成為關鍵解決。目前 NVIDIA Rubin 系列、AMD MI350 系列等頭部 GPU 均已采用 IOD,通過 “計算 Die 與 IO Die 解耦迭代”,既縮短上市周期,又為算力Die預留更大面積空間。

▲NVIDIA Rubin和Rubin Ultra采用IOD架構

▲ AMD MI350 Series采用IOD架構

IOD 架構以 Scale-up 協議為核心,集成 SerDes(串行通信)、UCIe-AP (芯粒互聯)、PCIe(對外互聯)三大模塊,關鍵指標亮眼:

? SerDes總帶寬:112Gbps * 32lane = 3.2Tb/s

? PCIe總帶寬:64Gbps * 16 = 1Tb/s

? UCIe-AP總帶寬:32GT/s * 64pin * 3module= 6.0Tb/s

? 封裝方式:Advanced Package

? 工藝:7/6nm

而GPU + IOD 框架進一步聚焦“算力核心(GPU)+互連樞紐(IOD)”協調,對接口 IP 的 “高帶寬、低延遲、兼容性” 提出更高要求 —— 這正是晟聯科的核心優勢所在。

晟聯科:接口IP技術適配,Scale-up生態需求

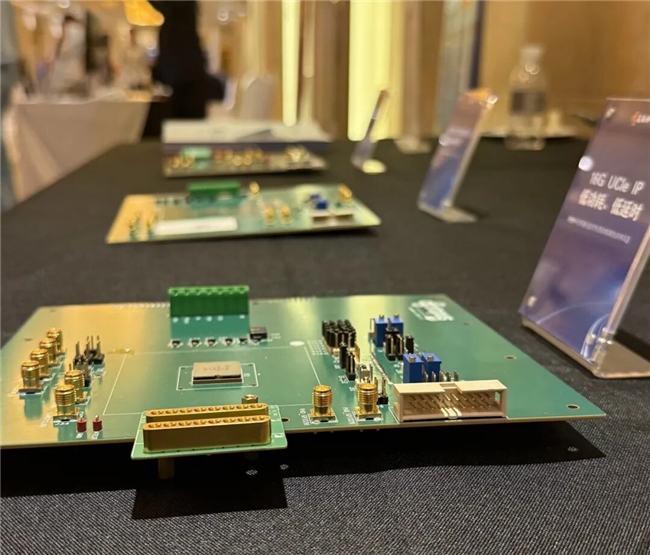

展會上,晟聯科 112G SerDes、PCIe 6.0、16G UCIe 三款 IP 方案,精準匹配超節點與 IOD 架構需求,成為現場焦點。

IP-SoC Days現場

112G SerDes:IOD 與超節點的 “高速數據通道”

同步滿足 IOD 架構與超節點的互連需求,關鍵性能包括:

? 超長傳輸距離:高插入損耗信道下優異的BER性能

? 靈活可配:不同距離下實現最優的功耗和延遲

? 可靠性:優秀的pre-FEC和post-FEC誤碼率,經過多代硅驗證

? 從銅纜到光纖:支持IEEE802.3bj/cd/ck、InfiniBand EDR、OIF CEI-112G-LR/MR/XSR

16G UCIe:IOD 架構下的 “芯粒互聯通用語言”

適配 IOD 架構 Chiplet 異構集成,關鍵性能包括:

? 高速率:16GT/s-32GT/s

? 低延時:快至2.x ns,FDI-to-FDI

? 測試手段:提供Debug/CP/FT測試、錯誤注入、實時眼圖掃描、多種Loopback

? 兼容性:嚴格遵守UCIe 1.1/2.0規范

PCIe 6.0:IOD 與 Scale-up 生態的 “銜接樞紐”

可直接整合進 IOD 架構,關鍵性能包括:

? 長距離:高插入損耗信道下可靠的傳輸

? 優異性能:低功耗,低延時,面積小

? 可靠性:PAM4 DSP PHY技術歷經十多年技術架構演進,保障PCIe 6.0 IP的高可靠性

? PIPE v6.1:支持PIPE v6.1,與PCIe controller、CXL控制器兼容

賦能算力:鏈接“芯”未來

此次 D&R IP-SoC Days China 2025 之行,晟聯科充分展現了中國高速接口 IP 企業的技術實力。未來,公司將持續迭代先進工藝與高速率方案,以 “易鏈天下,穩定快速” 的 IP 體驗,助力全球客戶加速算力創新。

審核編輯 黃宇

-

接口

+關注

關注

33文章

9520瀏覽量

157027 -

SCALE

+關注

關注

3文章

15瀏覽量

14449

發布評論請先 登錄

是德科技推出一系列全新Scale-up驗證解決方案

Credo發布新品Blue Heron 224G AI Scale-Up Retimer芯片

THine發布無光學DSP芯片組,賦能下一代Scale-Up型AI網絡“Slow and Wide”互聯

2025 ICCAD | 晟聯科重磅展示PCIe PHY+CTRL集成方案,3D Interface IP引領創新互聯基石

軟通動力與金盤科技合作邁入新階段

華為發布全球最強算力超節點和集群

使用NVIDIA NVLink Fusion技術提升AI推理性能

華為超節點互聯技術引領AI基礎設施新范式

湖北東昱欣晟超充電池項目開工暨第2000萬支電芯下線

奇異摩爾亮相2025中國AI算力大會

晟聯科受邀出席臺積電技術研討會,高速接口IP組合及解決方案助推海量數據暢行

硅基覺醒已至前夜,聯發科攜手生態加速智能體化用戶體驗時代到來

奇異摩爾攜手UALink聯盟助力AI網絡繁榮發展

超節點崛起,晟聯科引領 Scale-up 生態進入新階段

超節點崛起,晟聯科引領 Scale-up 生態進入新階段

評論