11月21日,2025集成電路發展論壇(成渝)暨第三十一屆集成電路設計業展覽會(以下簡稱:ICCAD-Expo 2025)在成都西部國際博覽城盛大閉幕。

這場匯聚 300 余家行業領軍企業、超萬名專業觀眾的技術盛宴上,國內領先的高速接口 IP 及解決方案提供商晟聯科成為全場焦點:不僅首次公開展示 PCIe PHY+Controller 一體化方案,CEO 陳繼強更是受邀參與【IP與IC服務設計分論壇】,發表主題為《3D Interface IP,新一代架構算力芯片的互聯基石》的演講,全方位分享晟聯科在邊緣算力互聯領域的技術突破與產業落地成果。

▲ 晟聯科創始人&CEO 陳繼強

主題演講:3D Interface IP,筑牢算力芯片底層基石

隨著高性能計算正在經歷一場新的革命,大模型推理推動算力競爭從通用芯片轉向專用芯片。3D堆疊突破內部帶寬后,芯片堆疊之間互聯設計卻成了新的瓶頸。

陳繼強首先介紹了晟聯科3D接口IP的技術成果,晟聯科的互聯方案讓專用芯片客戶無需攻克數模混合設計的難題,就能構建Tbps級數據航道。這不僅是接口技術的進步,更是讓3D IC真正釋放澎湃算力的互聯基石!

他表示,隨著AI 產業競爭重心正從云端訓練向邊緣推理快速遷移。數據顯示,到 2027 年推理算力負載占比逼近 80%,其中邊緣推理部署占比達 50% 以上,自動駕駛、智能工廠、AI 手機等場景的規模化落地,推動高效、可擴展、成本最優的推理算力成為產業發展新引擎。

面對邊緣場景對高速推理、高可靠性、低成本功耗的三重核心訴求,傳統架構難以突破 "內存墻" 瓶頸。在典型推理任務中,存儲的帶寬的利用率不到50%,計算在等存儲。而存算一體架構通過將計算單元嵌入存儲陣列,從根本上減少數據搬運,可將算力利用率提升 20% 以上,成為破解邊緣推理困境的關鍵技術路徑。

01技術破局:eLink-xD 系列突破TSV互聯瓶頸

陳繼強強調,存算一體架構雖打破 "內存墻",卻面臨 3D 堆疊帶來的互聯設計復雜性新瓶頸,TSV 互聯質量直接決定系統最終性能。為此,晟聯科針對性打造 eLink 系列高速互聯解決方案技術矩陣:eLink-xD 系列提供先進 Die-to-Die 連接能力,eLink-2D 解決片內互聯挑戰,eLink-3D 突破 TSV 互聯瓶頸。

02落地實力:從系統級封裝到全場景適配,解決大規模芯片設計的時序收斂難題

從架構到實體落地,eLink-xD 已實現系統級封裝(SiP)的成熟應用,兼容 Logic-on-Memory、Logic-on-IO、Memory-on-Logic 混合堆疊三種主流 3D IO 實現形態,適配 HBM、異構集成等多樣化場景。其內置鏈路訓練、時延鎖定、溫度自適應機制,實現超越 1E-15 的 BER 可靠性,可從容應對高低溫、強干擾等嚴苛環境。

03 3D布局:更高性能,助力多應用高速互聯

演講最后,陳繼強公布晟聯科 3DIO 技術研發路徑圖:現階段聚焦成熟工藝下的可靠性通信設計,未來利用更先進工藝節點進行功能迭代,進一步提升帶寬、帶寬密度與能效,從而覆蓋更多場景。

同時,晟聯科已構建包含 56G/112G SerDes、PCIe 6.0、UCIe、3D IO 的完整高速IP互聯技術矩陣,累計賦能客戶超 100 億美元設備出貨,成為全球芯片企業可靠的互聯技術伙伴。

晟聯科精彩直擊: PCIe PHY+Controller 方案首秀

此次ICCAD-Expo 2025展會上,晟聯科D83、D84 展臺人氣爆棚,三大高速接口 IP 解決方案集中亮相,成為專業觀眾駐足交流的核心區域。

01 重磅首發:PCIe PHY+Controller 方案實現高速互通實測

展臺上,晟聯科重點展示了PCIe PHY+Controller 全棧方案引發行業廣泛關注,現場完成兩大關鍵實測驗證:

·實現PCIe 5 應用<-> Transaction Layer <-> Physical Layer的高速互通測試;

·實現晟聯科PCIe測試板與商用Server CPU的高速互通測試。

該方案通過物理層(PHY)與控制器(Controller)的深度集成,無需額外適配即可快速部署,大幅降低客戶集成成本與研發周期。其全面兼容 PCIe Gen1-Gen5 規范,覆蓋2.5GT/s 至 32GT/s 速率,可靈活匹配邊緣智能、高性能計算等多場景需求,為設備提供穩定高效的高速互聯支撐,精準契合大算力時代的技術剛需。

▲ 現場觀眾觀看PCIe Demo

以技術為核心,賦能算力生態新發展

從 PCIe PHY+Controller 一體化方案的實測落地,到 eLink-xD 系列解決方案的全場景適配,再到 3DIO 技術的未來布局,晟聯科正以 "系統級互聯伙伴" 的定位,持續破解算力互聯瓶頸,為邊緣計算、AI 推理等領域提供核心技術支撐,助力中國集成電路產業鏈高質量發展。

未來,晟聯科將繼續深耕高速接口 IP 技術研發,推動更多創新方案落地應用,與行業伙伴攜手構建共贏的算力互聯生態!

審核編輯 黃宇

-

集成電路

+關注

關注

5461文章

12634瀏覽量

375359 -

PCIe

+關注

關注

16文章

1467瀏覽量

88792 -

ICCAD

+關注

關注

0文章

87瀏覽量

6542

發布評論請先 登錄

中國移動咪咕客廳大屏2D轉3D沉浸先鋒體驗官北京招募啟幕

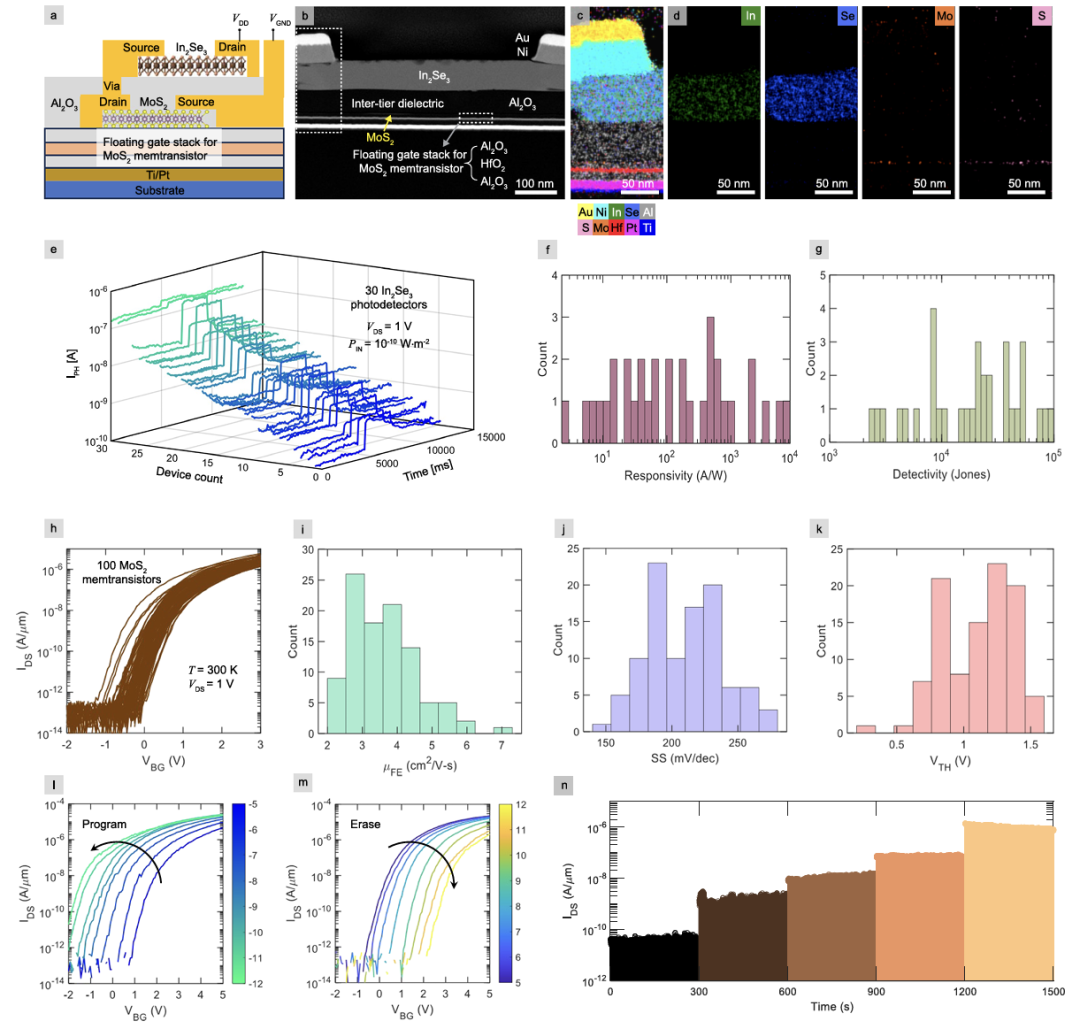

2D材料3D集成實現光電儲備池計算

安路科技亮相ICCAD-Expo 2025

創飛芯ICCAD-Expo 2025圓滿落幕

歌爾光學亮相2025法蘭克福國際精密成型及3D打印制造展覽會

奇捷科技亮相ICCAD-Expo 2025

ICCAD 2025:Imagination展示E系列GPU創新技術與多元生態應用

iSUN3D即將推出單組分彈性樹脂3D打印解決方案!

拓普聯科亮相2025德國EUHA國際聽力展,以創新驅動聲學未來

洛微科技攜4D FMCW激光雷達與3D感知方案閃耀光博會,引領行業新趨勢

一站式定制芯片及IP供應商燦芯半導體推出PCIe 4.0 PHY IP

CES Asia 2025蓄勢待發,聚焦低空經濟與AI,引領未來產業新變革

晟聯科受邀出席臺積電技術研討會,高速接口IP組合及解決方案助推海量數據暢行

2025 ICCAD | 晟聯科重磅展示PCIe PHY+CTRL集成方案,3D Interface IP引領創新互聯基石

2025 ICCAD | 晟聯科重磅展示PCIe PHY+CTRL集成方案,3D Interface IP引領創新互聯基石

評論