該TPIC6A595是一款單片、高壓、大電流電源邏輯8位移位寄存器,設計用于需要相對高負載功率的系統。該器件在輸出端包含一個內置電壓鉗位,用于電感瞬態保護。功率驅動器應用包括繼電器、螺線管和其他中電流或高壓負載。每個漏極開路DMOS晶體管都具有獨立的斬波限流電路,以防止短路時損壞。

*附件:tpic6a595.pdf

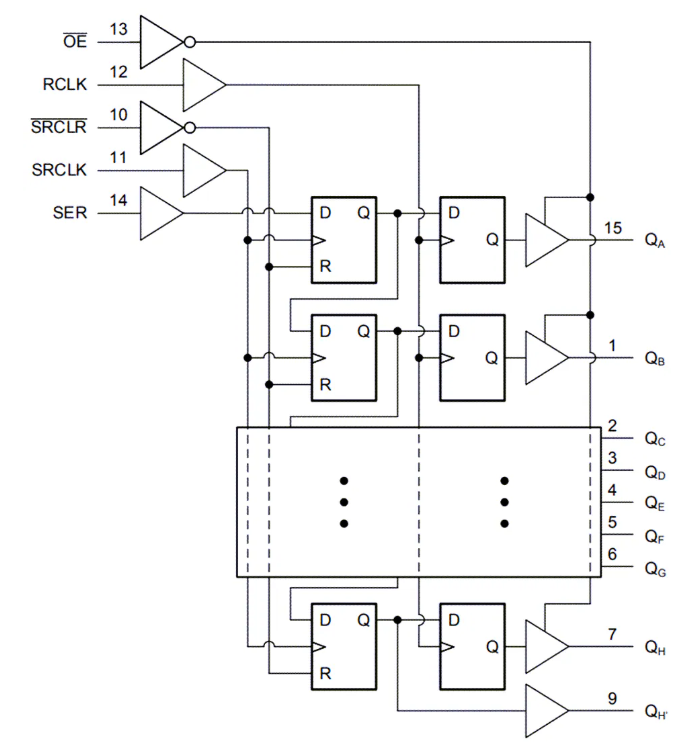

該器件包含一個 8 位串行輸入并行輸出移位寄存器,該寄存器為 8 位 D 型存儲寄存器供電。數據分別通過移位寄存器時鐘 (SRCK) 和寄存器時鐘 (RCK) 上升沿的移位寄存器和存儲寄存器傳輸。當移位寄存器清除 (SRCLR) 為高電平時,存儲寄存器將數據傳輸到輸出緩沖器。寫入數據和讀取數據僅在 RCK 較低時有效。當SRCLR為低電平時,輸入移位寄存器被清除。當輸出使能(G)保持為高電平時,輸出緩沖器中的所有數據都保持為低電平,并且所有漏極輸出都關斷。當G保持低電平時,來自存儲寄存器的數據對輸出緩沖器是透明的。串行輸出 (SER OUT) 允許將數據從移位寄存器級聯到其他器件。

輸出為低側開漏 DMOS 晶體管,輸出額定值為 50V,連續灌電流能力為 350mA。當輸出緩沖器中的數據為低電平時,DMOS晶體管輸出關斷。當數據為高電平時,DMOS晶體管輸出具有灌電流能力。

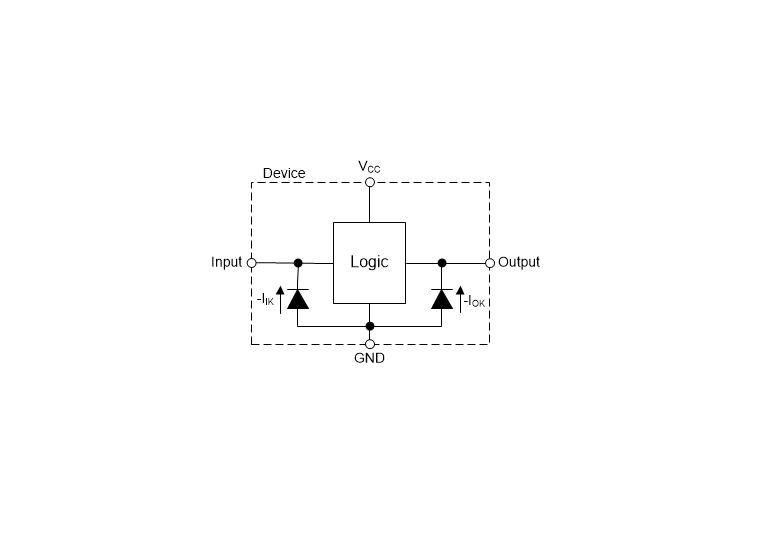

提供單獨的電源接地 (PGND) 和邏輯接地 (LGND) 端子,以促進最大的系統靈活性。所有 PGND 端子均內部連接,每個 PGND 端子必須外部連接到電源系統接地,以最大限度地減少寄生阻抗。LGND 和 PGND 之間的單點連接必須以減少邏輯和負載電路之間串擾的方式從外部進行。

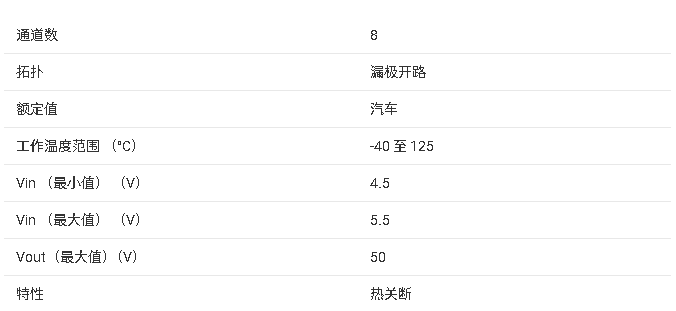

該TPIC6A595采用熱增強型正直插式 (NE) 封裝和寬體表面貼裝 (DW) 封裝。該TPIC6A595的特點是在 -40 至 125°C 的工作箱溫度范圍內運行。

特性

- 低 rDS(on):1Ω(典型值)

- 輸出短路保護

- 雪崩能量:75mJ

- 8個350mA DMOS輸出

- 50V 開關能力

- 設備是可級聯的

- 低功耗

參數

?1. 核心特性?

- ?高性能輸出?:8路開漏DMOS晶體管輸出,每路支持50V耐壓及350mA連續灌電流能力,內置短路保護和75mJ雪崩能量吸收。

- ?低功耗設計?:典型導通電阻1Ω,邏輯與功率地分離設計降低干擾。

- ?級聯功能?:通過SER OUT引腳支持多設備串聯擴展。

?2. 關鍵功能?

- ?數據控制?:

- 串行輸入(SER IN)通過上升沿時鐘(SRCK)移位至8位寄存器。

- 存儲寄存器在RCK上升沿鎖存數據,SRCLR低電平清零寄存器。

- 輸出使能(G)控制DMOS開關,支持全局PWM調光。

- ?保護機制?:獨立電流斬波限流電路,防止輸出短路損壞。

?3. 電氣參數?

- ?工作條件?:邏輯電壓4.5V

5.5V(超壓至7V可能影響可靠性),溫度范圍-40°C125°C。 - ?開關特性?:傳播延遲典型值30ns(高→低)、125ns(低→高),輸出上升/下降時間60ns/30ns。

?4. 封裝與型號?

- ?封裝選項?:

- PDIP-20(NE):24.0mm×6.86mm,適合通孔安裝。

- SOIC-24(DW):15.4mm×7.5mm,表貼封裝。

- ?型號標識?:如TPIC6A595DW(SOIC)、TPIC6A595NE(PDIP)。

?5. 應用場景?

?6. 設計注意事項?

- ?布局建議?:功率地(PGND)與邏輯地(LGND)單點連接以降低噪聲。

- ?熱管理?:PDIP封裝最大功耗2.5W(25°C時),需根據工況降額使用。

?7. 文檔支持?

- 提供詳細時序圖、熱阻曲線及測試電路,涵蓋雪崩能量、反向恢復電流等參數測量方法。

-

晶體管

+關注

關注

78文章

10395瀏覽量

147723 -

移位寄存器

+關注

關注

4文章

340瀏覽量

23332 -

DMOS

+關注

關注

0文章

45瀏覽量

15249 -

漏極開路

+關注

關注

0文章

31瀏覽量

8649 -

瞬態保護

+關注

關注

1文章

16瀏覽量

5892

發布評論請先 登錄

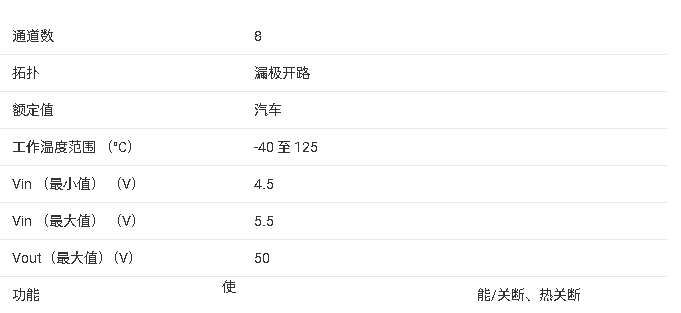

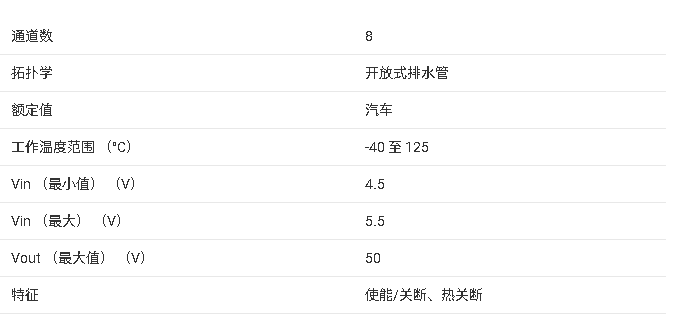

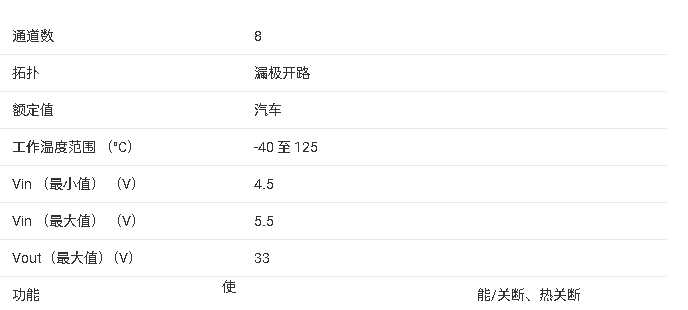

?TPIC6B596 8位移位寄存器技術文檔總結

?TPIC6C595 8位移位寄存器數據手冊總結

?TPIC6B595 8位功率移位寄存器技術文檔總結

?TPIC6A595 8位移位寄存器技術文檔總結

?TPIC6A595 8位移位寄存器技術文檔總結

評論