文章來源:學習那些事

原文作者:小陳婆婆

本文介紹了三維集成電路設計中TSV(硅通孔)技術的設計優化。

在三維集成電路設計中,TSV(硅通孔)技術通過垂直互連顯著提升了系統集成密度與性能,但其物理尺寸效應與寄生參數對互連特性的影響已成為設計優化的核心挑戰,本文分述如下:

RLC延時模型

信號反射

多目標協同優化算法

RLC延時模型

在寄生效應分析方面,TSV的RC特性對互連延時與功耗的影響尤為關鍵。三維集成技術通過壓縮全局互連線長,使最大互連延時較二維系統降低40%~50%,但TSV RC效應在中小規模電路中逐漸凸顯。當門電路規模降至1mm2時,包含TSV的三維系統延時達0.45ns,接近二維系統的0.5ns。

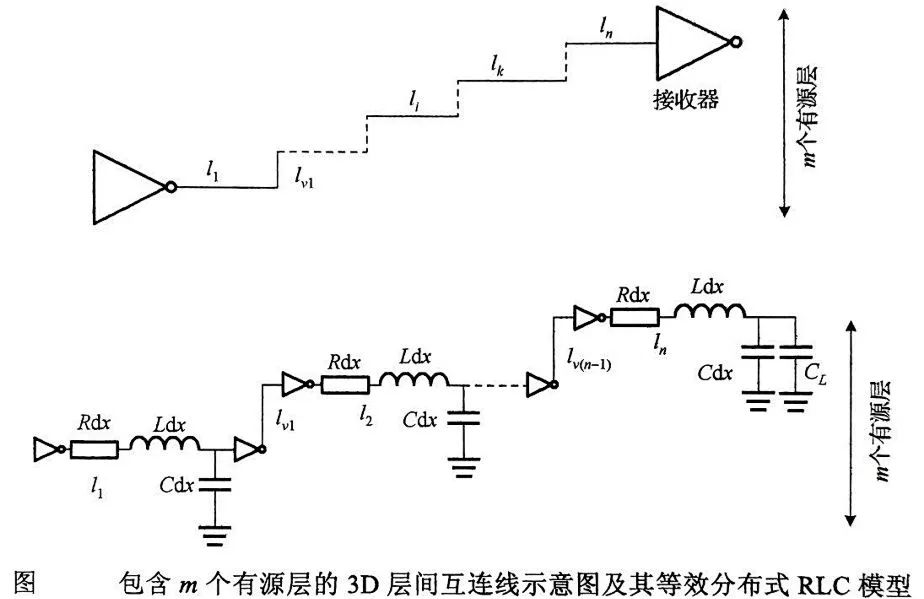

為應對高頻信號下的電感效應,提出了分布式RLC互連延時模型,將互連線等效為均勻的RLC傳輸線。該模型表明,隨著系統時鐘頻率增大與信號上升時間縮短,互連電感效應成為不可忽視的因素,尤其在采用寬厚金屬線的全局信號線和時鐘線中,電感導致的延時增大、電壓過沖和感性串擾問題更為顯著。

通過合理布局TSV并優化各層互連線段長,可有效降低全局互連延時。近期研究突破包括“智能TSV屏蔽”技術,通過動態關閉空閑TSV,將中小規模電路的TSV功耗降低30%;“分布式緩沖器-TSV協同設計”方法,使緩沖器數目減少25%的同時保持延時性能不變。此外,TSV熱-電耦合分析模塊,可實時預測不同布局方案下的功耗-延時乘積,設計效率提升40%。

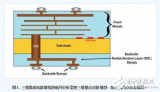

在材料與工藝創新方面,玻璃通孔(GTV)技術,通過低介電常數玻璃基板替代傳統硅基,將TSV寄生電容降低40%,為高頻應用開辟了新路徑;石墨烯包覆TSV結構,成功將TSV電阻降低至銅互連的1/10,顯著緩解了TSV RC效應。這些進展表明,精確量化TSV效應并開發跨層優化技術,已成為釋放三維集成潛力的關鍵。

信號反射

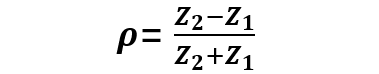

在三維集成電路設計中,信號完整性已成為制約高速互連性能的核心挑戰,其中反射效應因TSV阻抗突變而尤為顯著。當信號沿分布式RLC傳輸線傳播時,瞬態阻抗的變化會導致部分信號反射,引發振鈴、過沖等失真問題,這一問題在大規模集成系統中因信號上升時間縮短而進一步加劇。反射系數ρ作為衡量阻抗不連續性的關鍵指標,定義為反射電壓與入射電壓的比值,其表達式為:

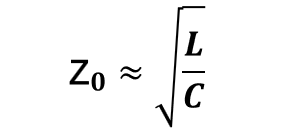

式中,Z?與Z?分別為信號傳播路徑中相鄰區域的特征阻抗。在高頻條件下,互連電阻R與電導G的影響可忽略,特征阻抗可簡化為:

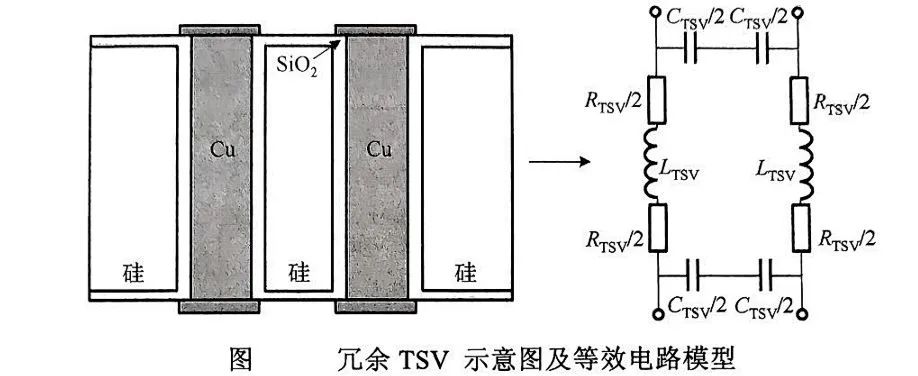

其中,L與C為互連線單位長度的分布電感與電容。對于垂直TSV而言,其等效電感LTSV與電容CTSV與物理尺寸(半徑rTSV、高度hTSV)強相關,因此優化TSV幾何參數成為減小反射系數的直接手段。

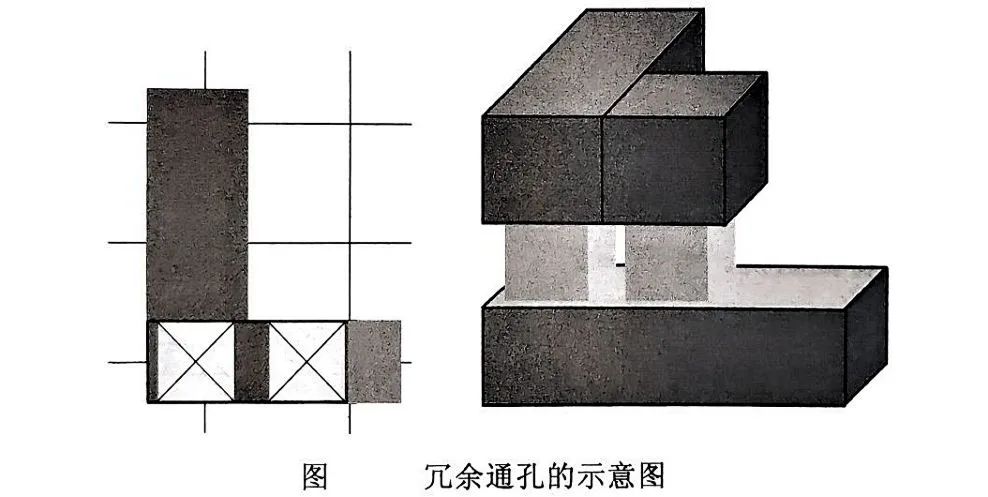

然而,實際工藝中TSV尺寸受設計規則嚴格限制,冗余通孔技術通過并行插入多個通孔,在提升制造良率的同時,等效調整了TSV的電學特性,實現與單個大尺寸TSV相近的阻抗匹配效果。

近期行業進展為信號完整性優化提供了新思路。例如,3nm 3D IC工藝中引入“自適應阻抗匹配”技術,通過動態調節緩沖器輸出阻抗,使Z?與Z?實時匹配,將反射系數降低至0.1以下;“分布式TSV陣列”設計,利用多個小尺寸TSV并行連接,在保持垂直互連密度的同時,將特征阻抗波動控制在5%以內。此外,TSV反射分析模塊,可精準預測不同布局方案下的信號失真程度,設計周期縮短40%。在材料創新方面,碳納米管(CNT)TSV技術,通過低電阻率材料將TSV等效電感降低30%,顯著緩解了阻抗突變問題。

這些技術突破表明,精確量化TSV電學特性并開發跨層優化技術,已成為保障3D IC信號完整性的關鍵。未來,隨著晶圓級異構集成技術的演進,TSV尺寸效應與寄生效應的協同優化將持續深化,為高頻、高速三維集成系統提供性能保障。

多目標協同優化算法

在三維集成電路設計中,信號傳輸延遲與反射畸變控制是互連優化領域的核心挑戰。基于傳輸線理論分析可知,三維互連系統的時延特性不僅與分段連線長度及硅通孔(TSV)物理尺寸相關,更受到信號反射系數的顯著影響。為同時實現低時延、高傳輸速率與長距離信號完整性,需建立多目標協同優化框架,對TSV插入位置、冗余通孔數目及分段線長進行聯合設計。

具體而言,硅通孔高度受限于襯底減薄工藝水平,在特定技術節點下可視為定值,因此優化問題可轉化為最小化互連總時延與反射系數的組合目標。

算法執行流程遵循閉環優化策略:首先初始化冗余通孔配置,基于傳輸線模型計算初始反射系數;繼而通過布局優化算法確定最佳分段線長及對應時延;再通過尺寸優化調整冗余通孔數目,獲得改進后的反射系數與次優時延;若次優時延未達收斂閾值,則循環執行布局-尺寸優化步驟,直至獲得全局最優解,同步確定最佳分段線長配置及冗余通孔分布。

值得關注的是,隨著先進封裝技術向5nm及以下節點演進,多物理場耦合效應對TSV優化的影響日益顯著。近期研究顯示,基于機器學習的代理模型可有效提升多目標優化效率,例如采用深度強化學習實現時延與反射的快速權衡。此外,2024年IEEE國際固態電路會議(ISSCC)報道的混合鍵合技術,通過亞微米級對準精度顯著降低了TSV間距需求,為三維互連優化提供了新的設計自由度。這些技術進展表明,多目標協同優化算法正朝著與工藝技術深度融合的方向發展,未來將更注重設計-制造協同(DTCO)框架的構建。

-

集成電路

+關注

關注

5458文章

12609瀏覽量

375023 -

TSV

+關注

關注

4文章

137瀏覽量

82709 -

硅通孔

+關注

關注

2文章

29瀏覽量

12128

原文標題:?三維集成電路的TSV布局設計

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

世界級專家為你解讀:晶圓級三維系統集成技術

有償,用matlab仿真三維電路互連線尺寸調整對延時功耗帶寬影響

三維集成電路系統的電網分析

三維集成電路(IC)設計中的溫度控制

Integrity 3D-IC早期三維布圖綜合功能

10.9.6 三維集成電路測試∈《集成電路產業全書》

10.5.2 基于TSV的三維集成電路∈《集成電路產業全書》

?三維集成電路的TSV布局設計

?三維集成電路的TSV布局設計

評論