作為焊料廠家,我們常說“封裝技術(shù)的升級(jí),本質(zhì)是凸點(diǎn)的升級(jí)”。從早期的插裝芯片到如今的3D堆疊,凸點(diǎn)制作始終是連接芯片與外部世界的核心環(huán)節(jié)。今天就從焊料廠家工程師的視角,簡單回顧封裝的發(fā)展,聊聊凸點(diǎn)制作的“進(jìn)化史”,以及作為焊料的錫膏如何一路適配這些變化。?

一、凸點(diǎn)制作在封裝流程中的“定位”:始終是“互連橋梁”?

無論哪種封裝形式,凸點(diǎn)制作都處于芯片與基板/載板互連的前端環(huán)節(jié),相當(dāng)于給芯片“裝插頭”。

具體來說:?在晶圓級(jí)封裝中,它是切割前的最后一步——在晶圓上做好凸點(diǎn),再切割成單顆芯片。在傳統(tǒng)封裝中,凸點(diǎn)緊隨芯片切割之后,是芯片貼裝到基板前的關(guān)鍵工序。簡單說,沒有凸點(diǎn),芯片就是“孤島”,無法與外界傳輸信號(hào)。?

二、封裝形式升級(jí)倒逼凸點(diǎn)“迭代”:從“粗放”到“精密”?

1. 插裝時(shí)代(DIP/SOP):凸點(diǎn)只是“配角”?

封裝特點(diǎn):芯片通過長引腳插入 PCB 孔中,引腳間距≥2.54mm,對(duì)互連精度要求低

凸點(diǎn)角色:此時(shí)還沒有“獨(dú)立凸點(diǎn)” 概念,僅在引線鍵合處形成微小焊點(diǎn),相當(dāng)于“臨時(shí)固定點(diǎn)”。?

材料應(yīng)用:以錫鉛合金為主(熔點(diǎn) 183℃),成本低、潤濕性好。?

工藝:手工蘸取焊錫膏點(diǎn)涂,再經(jīng)簡易加熱固化,焊點(diǎn)直徑≥500μm,幾乎無精度要求。

錫膏狀態(tài):顆粒度 T3 級(jí)(25-45μm),助焊劑含量高,能容忍焊盤氧化。?

2. 面陣封裝時(shí)代(BGA/CSP):凸點(diǎn)成為“主角”?

封裝特點(diǎn):I/O 引腳從邊緣擴(kuò)展到整個(gè)芯片表面,間距縮小至0.8-1.2mm,需要密集的 “點(diǎn)接觸”。?

凸點(diǎn)角色:替代長引腳成為主要互連結(jié)構(gòu),直接決定封裝尺寸和信號(hào)傳輸效率。?

材料變化:無鉛化推動(dòng)錫基焊料主流化,SAC305成為首選,熔點(diǎn)217℃,滿足RoHS要求;部分高端場景開始試用銅柱凸點(diǎn)(導(dǎo)電性提升5倍)。?

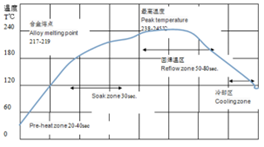

工藝升級(jí):電鍍工藝普及,能做出高度一致的凸點(diǎn)(偏差≤5μm);印刷——回流工藝也開始應(yīng)用,通過鋼網(wǎng)將錫膏印在焊盤上,回流后形成凸點(diǎn)。?

錫膏進(jìn)化:顆粒度提升至T5級(jí)(15-25μm),觸變性優(yōu)化,能在0.8mm間距下避免橋連。?

3. 晶圓級(jí)封裝(WLP):凸點(diǎn)進(jìn)入“微米級(jí)戰(zhàn)場”?

封裝特點(diǎn):封裝尺寸接近芯片尺寸,I/O間距縮小至0.3-0.5mm,要求凸點(diǎn)“微型化 + 高密度”。?

凸點(diǎn)角色:不僅是互連點(diǎn),還要承擔(dān)信號(hào)重分布功能(配合RDL)。?

材料突破:銅柱 + 錫帽結(jié)構(gòu)成為主流 —— 銅柱提供機(jī)械支撐,錫帽負(fù)責(zé)焊接,兼顧導(dǎo)電性與可靠性;低溫錫膏(Sn58Bi,138℃熔點(diǎn))開始用于多層堆疊,避免高溫?fù)p傷下層芯片。?

工藝革新:電鍍精度提升至±2μm,能做出直徑20-50μm的凸點(diǎn);印刷——回流工藝改用電鑄鋼網(wǎng),錫膏脫模更徹底。?

錫膏適配:顆粒度達(dá)T8/T9級(jí)(2-5μm),滿足0.3mm以下間距印刷,助焊劑改為低揮發(fā)配方,減少回流氣泡。?

4. Chiplet 與 3D IC 時(shí)代:凸點(diǎn)進(jìn)入 “納米級(jí)對(duì)決”?

封裝特點(diǎn):多芯片堆疊,垂直互連間距≤50μm,需要 “超小 + 超可靠” 的凸點(diǎn)。?

凸點(diǎn)角色:是芯片間直接通信的 “高速通道”,延遲要求≤10ps。?

材料革命:金屬間化合物(如 Cu?Sn、Ag?Sn)崛起,通過固態(tài)焊接形成,熔點(diǎn)>600℃,抗疲勞性是錫基的3倍;銅柱直徑縮小至10-30μm,表面鍍鎳金防氧化。?

工藝極限:電鍍銅柱垂直度偏差<1°,固態(tài)焊接壓力控制精度±1MPa;印刷——回流工藝面臨極限,逐漸被電鍍替代。?

錫膏定位:退為“輔助角色”,僅在頂層芯片與基板互連時(shí)使用,要求超低空洞率(<1%)和超細(xì)印刷(點(diǎn)徑<50μm)。?

三、錫膏的“生存智慧”:跟著封裝需求“變”?

從T3到T9級(jí)顆粒,從高助焊劑到低揮發(fā)配方,錫膏的進(jìn)化始終圍繞兩個(gè)核心:?

適配更小間距:早期BGA用T5級(jí)錫膏就能滿足0.8mm間距,而現(xiàn)在3D IC的凸點(diǎn)印刷需要 T8 級(jí),粉末粒徑小到能穿過頭發(fā)絲粗細(xì)的鋼網(wǎng)孔(20μm)。?

平衡可靠性與工藝性:在高溫封裝中,錫膏添加銀、銅元素提升耐熱性;在低溫堆疊中,改用 SnBi 合金降低熔點(diǎn);為減少空洞,助焊劑中加入活性更強(qiáng)的有機(jī)酸,同時(shí)控制揮發(fā)速度。?

傲牛科技為某Chiplet客戶定制的錫膏,通過調(diào)整觸變指數(shù)(從3.0到4.5),解決了 0.2mm間距印刷時(shí)的“塌邊”問題,良率從78%提升至95%,助焊劑中加入了與日本材料公司共同開發(fā)的空洞抑制劑,將空洞率降低至3%。?

四、未來趨勢:凸點(diǎn)還能 “小” 到什么程度??

行業(yè)預(yù)測,到2030年,Micro LED 的凸點(diǎn)直徑將縮小至5μm,這對(duì)錫膏提出了新挑戰(zhàn):粉末粒徑可能需要達(dá)到亞微米級(jí)(<1μm),印刷精度要控制在±1μm以內(nèi),這對(duì)于焊料廠家的研發(fā)和生產(chǎn)能力提出了新的要求,行業(yè)的變化和需求也在鞭策我們在不斷進(jìn)步和提升。?

-

DIP封裝

+關(guān)注

關(guān)注

1文章

42瀏覽量

14059 -

錫膏

+關(guān)注

關(guān)注

1文章

993瀏覽量

18303 -

3D封裝

+關(guān)注

關(guān)注

9文章

149瀏覽量

28335 -

chiplet

+關(guān)注

關(guān)注

6文章

496瀏覽量

13625 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

546瀏覽量

1043

發(fā)布評(píng)論請(qǐng)先 登錄

從手動(dòng)到全自動(dòng):錫膏印刷機(jī)的進(jìn)化史

淺談錫膏是如何制作的?

11 BGA封裝激光重熔釬料凸點(diǎn)制作技術(shù)

激光錫焊的原理及優(yōu)勢是什么,適配激光焊接工藝錫膏推薦

iPhone主板芯片及整機(jī)配置的進(jìn)化史

國內(nèi)使用的錫膏品牌,你知道幾個(gè)?

大學(xué)寢室門的進(jìn)化史:RFID的寢室門禁系統(tǒng)

從工藝到設(shè)備全方位解析錫膏在晶圓級(jí)封裝中的應(yīng)用

SiP 封裝與錫膏等焊料協(xié)同進(jìn)化之路?

聊聊倒裝芯片凸點(diǎn)(Bump)制作的發(fā)展史

晶圓級(jí)封裝Bump制作中錫膏和助焊劑的應(yīng)用解析

從DIP到Chiplet,聊聊凸點(diǎn)制作和錫膏適配的進(jìn)化史

從DIP到Chiplet,聊聊凸點(diǎn)制作和錫膏適配的進(jìn)化史

評(píng)論