RZT2H是多核處理器,啟動時,需要一個“主核”先啟動,然后主核根據規則,加載和啟動其他內核。本文以T2H內部的CR52雙核為例,說明T2H多核啟動流程。

LSI reset release時,其內置的BOOTROM總是從CR52_0開始執行,即我們可以把CR52_0定義為主核。如果系統配置為程序從External XSPI_FLASH 啟動,BOOTROM首先根據存放在external Flash起始位置的Parameter中的定義,從Flash中加載Loader程序。

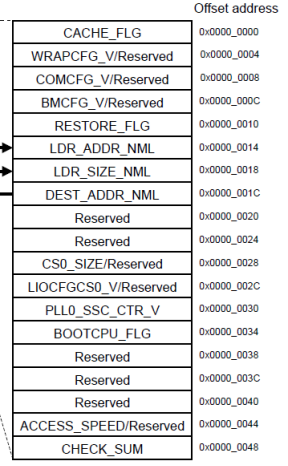

Parameters for the Loader:

存放在External Memory區域的起始位置,存放著與程序加載相關的關鍵信息,如例如在各個啟動模式下,啟動期間的CPU緩存設置,用于與外部存儲器通信的引導外設(xSPI或SDHI)的配置以及加載程序的size等等。

Parameters for Loader的結構如下:

除了上述信息,其中DSET_ADDR_NML是跟多核啟動相關的關鍵參數;該參數決定Loader Program的加載地址,而BOOTROM根據這個地址決定接下來在哪個核上,從哪個地址開始執行LOADER程序。

這里補充一下T2H程序結構和基本加載啟動流程:

T2H平臺,燒錄到External Flash上的內容邏輯上分成3部分:

上述的Parameter for Loader;

Loader program;

Application program;

啟動時,BOOTROM根據Parameter for Loader從Flash加載Loader program到指定位置開始執行,然后Loader program再加載Application program并跳轉執行。

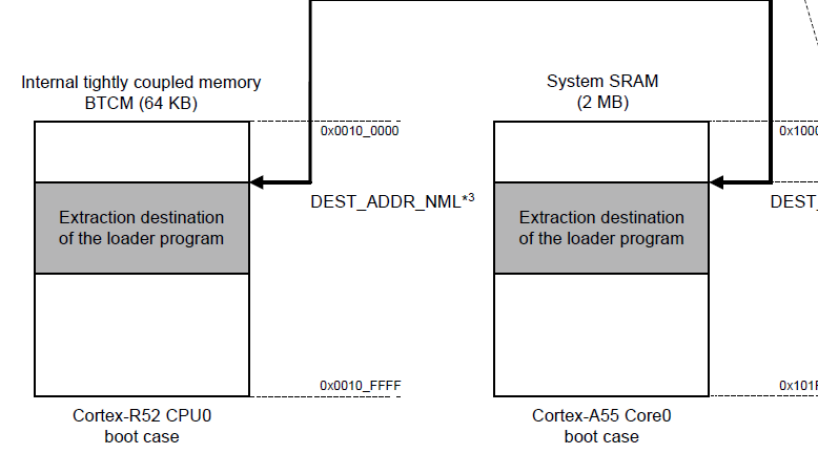

在T2H多核架構下(4xCA55+2xCR52)Loader parameter中的:DEST_ADDR_NML有2個可能的地址范圍,即BTCM7或者7System SRAM:

如果BOOTROM判斷到加載地址是在BTCM中,那CR52_0繼續執行(second boot CPU仍然是CR52_0),從加載地址開始執行LOADER PROGRAM,并完成整個啟動流程。

如果BOOTROM判斷到加載地址是SYSTEM,系統會認為second boot CPU是CA55_0,BOOTROM 就會Reset release CA55_0,并把CR52_0轉換到WFI狀態,然后讓CA55_0執行Loader program。

以上介紹了在T2H多核系統中的主核First boot CPU和Second boot CPU的啟動過程,但是其他的Core此時都還是在Reset 狀態,等待 Second boot CPU為其加載程序和釋放。

接下來以52雙核為例,說明CR52_0如何完成自身程序加載和加載并啟動CR52_1的過程;

在這個示例中,CR52_0用作Second boot CPU,以下步驟是CR52_0的Loader Program需要完成的工作:

根據FSP時鐘樹,配置LSI的各個Clock;

初始化Loader Program的Data段和BSS段;

配置ADDRESS_EXPANDER_INIT:

Address EXPANDER的作用是:通過映射的方法,使能32 bit Master訪問4G area之外的地址空間,詳見UM 13.4.5;

TrustedZone 400初始化;

COPY應用程序的PRG段/DATA段/BSS段,到相應的運行RAM空間。如果需要啟動其他內核,則把其他內核的PRG/DATA,也COPY到對應RAM區域,然后Release目標內核;

核間通信用到的信號量初始化;

Master MPU初始化;

GIC初始化和系統定義的中斷的初始化配置;

TFU初始化;

Main()跳轉應用;

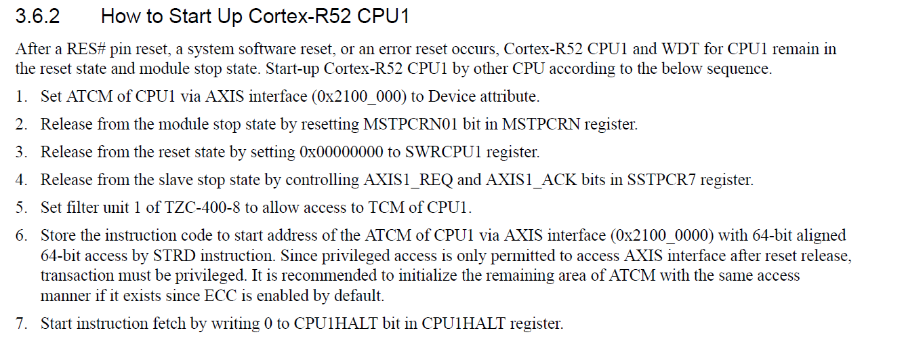

其中步驟5中啟動目標CPU(CR52_1)

的步驟如下圖:

上述步驟中需要特別強調的地方:

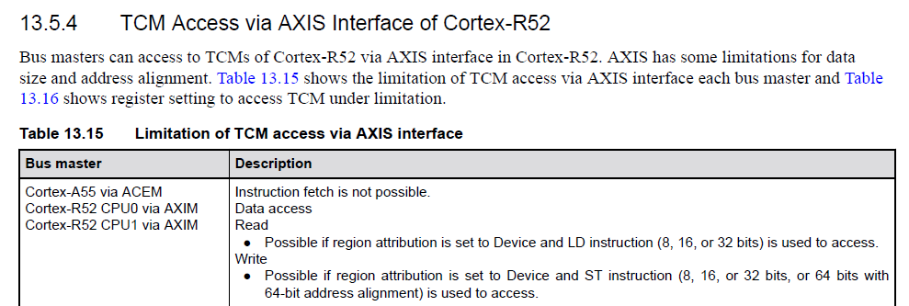

啟動過程,需要從CR52_0訪問CR52_1的ATCM空間。根據T2H的架構,這個訪問只能通過AXI總線,且必須把CR52_1的ATCM region通過MPU配置為Device屬性,并且只能使用LD和ST指令;

對應到代碼中,上面的7個步驟在函數SystemInit()文件startup.c中都能找到對應的實現;

重點說明函數bsp_cpu_reset_release()該函數實現上述步驟的2,3,4,6,7;

重點分析步驟6:

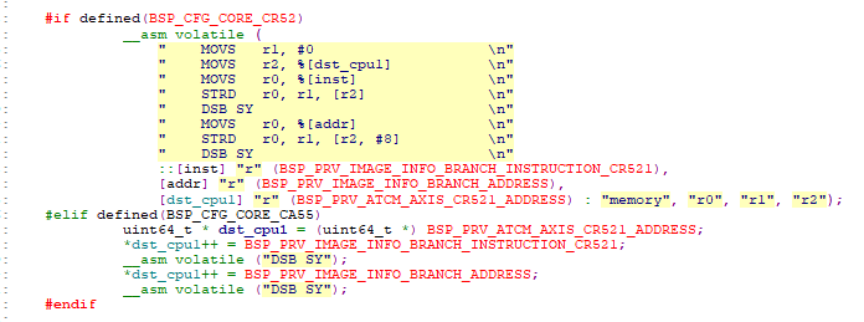

代碼段如下:

這段代碼完成的動作:

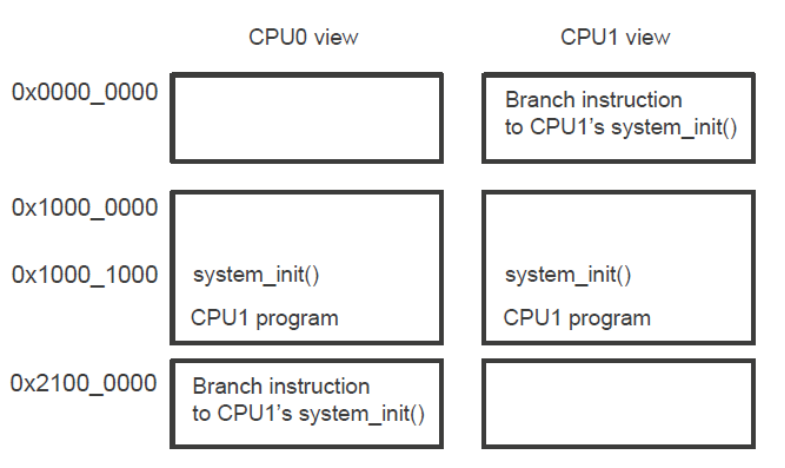

把1st分支指令[inst]經AXIS接口復制到CR52_1 ATCM的起始地址(dst_cpu1:0x2100_000);

復制跳轉指令要用到的目標地址(addr);

操作到的存儲地址如圖示:

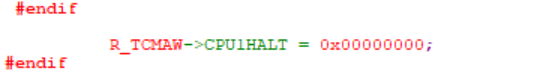

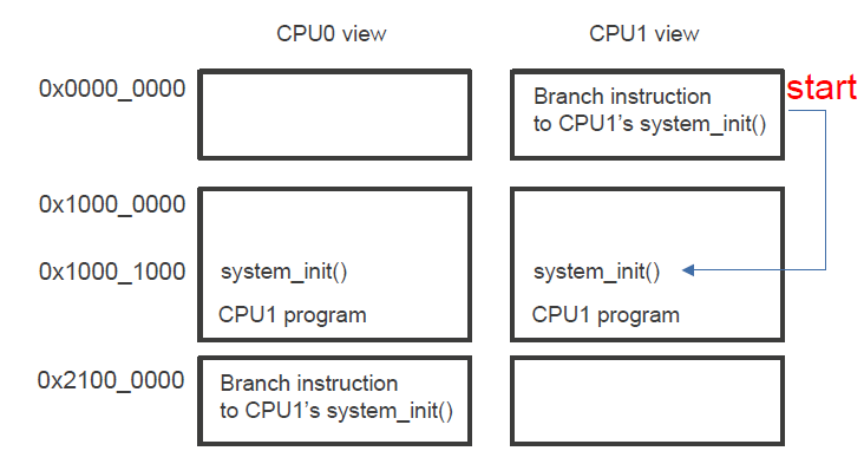

最后步驟7:

CR52_1跳轉到入口函數system_init,開始執行:

以上,以雙CR52 Core為例,說明了T2H多核系統的BOOT流程。

延伸閱讀:

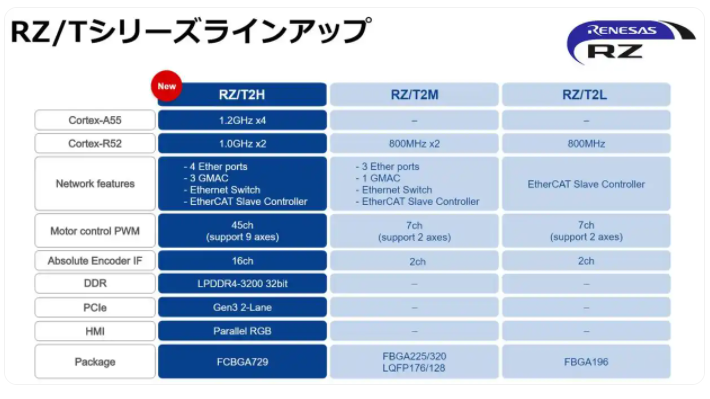

日本瑞薩電子此前量產面向工業設備的 MPU(微處理器單元)RZ / T2H,預計用于機器人等,號稱 CPU 軟件處理性能比以前提高了 20~30%。一個芯片可以同時控制最多 9 軸的電機。

RZ / T2H 的 CPU 采用四個 Arm Cortex-A55 內核,最高主頻為 1.2GHz,支持 LPDDR4-3200 32bit 內存;實時 CPU 包括兩個 Cortex-R52,最高主頻 1GHz。

-

機器人

+關注

關注

213文章

31193瀏覽量

222950 -

瑞薩

+關注

關注

37文章

22498瀏覽量

90977 -

代碼

+關注

關注

30文章

4973瀏覽量

74152 -

Boot

+關注

關注

0文章

154瀏覽量

37798

發布評論請先 登錄

瑞薩系列-米爾RZ/T2H核心板開發板 高端MPU,驅控一體單芯片方案

瑞芯微SOC智能視覺AI處理器

RK3576機器人核心:三屏異顯+八路攝像頭,重塑機器人交互與感知

宇樹科技發布H2仿生人形機器人

自制巡線解迷宮機器人(上)

工業機器人的特點

明遠智睿SSD2351開發板:語音機器人領域的變革力量

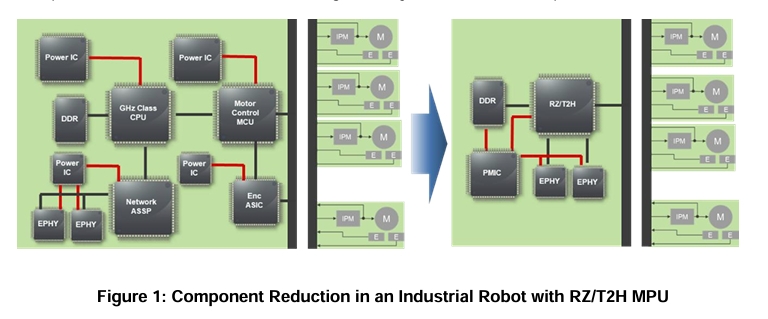

使用RZ/T2H MPU提高工業機器人性能并顯著減少組件數量和開發工時的方法

瑞薩機器人處理器RZT2H CR52雙核BOOT流程和例程代碼分析

瑞薩機器人處理器RZT2H CR52雙核BOOT流程和例程代碼分析

評論