01簡介

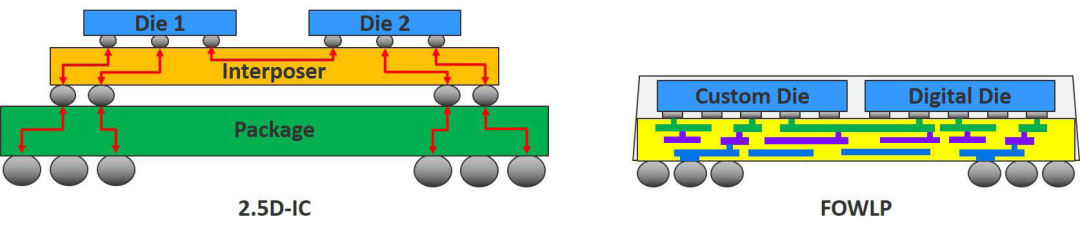

高密度先進封裝 (HDAP) 設計如今已成為真實的產品。過去十年里,HDAP 技術的所有變化形式都承諾通過集成使用不同技術節點構建的多個集成電路 (IC) 芯片(異構集成),來獲得改進的外形參數和功能。下圖顯示了兩種流行的 HDAP 技術:2.5D(中介層)和扇出型晶圓級封裝 (FOWLP) 設計。

圖:基于中介層的 2.5D IC 和 FOWLP 設計是最常用的 HDAP 技術

同任何電子產品一樣,HDAP 設計也需要廣泛的驗證,確保它們能夠按預期運行,并且能夠可靠地制造出足夠的數量以滿足市場需求。但事實證明,自動化 HDAP 驗證對電子設計自動化 (EDA) 行業來說頗具挑戰,因為它需要結合 IC 和封裝驗證的元素。在確定問題、建議或制定解決方案方面,人們投入了大量的時間和研究。類似于集成電路工藝設計套件 (PDK) 的合格裝配設計套件 (ADK) 的一般概念,至少已在有限的程度上變為現實。HDAP 的裝配級版圖和電路圖比較 (LVS) 驗證,現在至少有了一種 EDA 解決方案。HDAP 的布線后仿真(模擬)和布線后 STA(數字)流程的價值,更是眾所周知。人們認識到,需要一種方法來生成 HDAP 系統級連接,同時兼顧芯片、封裝和芯片/封裝接口寄生效應。

在推動 HDAP 成為一個可行的市場選擇方面,雖然上述所有工作都很珍貴,但現在似乎有必要評估這一過程的成熟度和范圍,并展望其未來的發展。為此,我們將聚焦其中一個目標:封裝 LVS 驗證。

02HDAP 物理驗證成熟度

隨著 HDAP 技術的日益發展和成熟,設計人員需要 EDA 工具公司、晶圓代工廠和封測代工廠 (OSAT) 提供合格、可靠的 EDA 設計和驗證流程。完成設計后,第一步自然是 HDAP 的物理驗證。HDAP 設計包含通過封裝連接的多個異構芯片。雖然 HDAP 中每個芯片自身的功能都已經過驗證,但 HDAP 設計人員如何確保整個 HDAP 在制造后仍能按預期運行呢?

這個問題代表了一種不連續性,也是傳統封裝設計中不存在的全新挑戰。在過去,單憑肉眼檢查就足以確認芯片是否正確連接到封裝,繼而連接到最終產品,如印刷電路板 (PCB)。對 HDAP 設計而言,情況并非如此。

盡管 EDA 公司、晶圓代工廠/OSAT 和 HDAP 設計公司已合作多年,共同構建 HDAP 物理驗證流程,但這個流程還遠遠談不上 “成熟”。各方需要學習的地方還很多。

03驗證數據完整性

下面我們來考慮一下面向 HDAP 設計的版圖和電路圖比較 (LVS) 驗證。除非版圖設計中內置的幾何形狀實現了原始原理圖/設計意圖所需的連接,否則片上系統 (SoC) 就無法獲批投入制造。LVS 驗證是 SoC 領域一個成熟、完善的自動化流程。用于 SoC 的 EDA LVS 工具需要一組一致的基本輸入:

■ 版圖數據庫(格式可以是 GDSII、OASIS 或 LEF/DEF)

■源網表(格式可以是 SPICE 或 Verilog)

■ LVS 規則集(基于 EDA 公司專有語法的格式)

設計公司、晶圓代工廠和 EDA 供應商都理解并同意,如果沒有某種形式的上述三種輸入,SoC LVS 驗證便無從談起。LVS 規則集通常由晶圓代工廠創建并提供,獨立于任何單一 SoC 設計,版圖數據庫和源網表則由設計公司創建。

回到 HDAP LVS 驗證,我們馬上就能發現重要的差異。最明顯且最關鍵的一點是,設計公司、晶圓代工廠/OSAT 和 EDA 公司在 HDAP LVS 流程所需的輸入集上沒有達成一致。存在這種脫節的原因有三個:所有權、數據可用性和設計依賴性。

所有權

由于 HDAP 仍是一種新興技術,HDAP 驗證的責任在不同公司往往由不同的團隊承擔。例如,一些設計公司傾向于將 2.5D 設計和驗證視為 “SoC 為主,封裝為輔” 的活動。這類設計的設計和驗證責任通常落到了 SoC 和/或計算機輔助設計 (CAD) 團隊的身上,他們在 SoC 驗證要求和格式方面有著豐富的經驗。而對于 FOWLP 封裝,設計和驗證被視為 “SoC 為輔,封裝為主” 的活動,因此該責任通常由不太熟悉 SoC 驗證要求和格式的封裝團隊承擔。保持這種多樣性的底線是,晶圓代工廠/OSAT 和 EDA 公司在支持采用不同方法且具有不同要求的 HDAP 設計公司時,必須做好靈活應對的準備。

數據可用性

為了實現對整個 HDAP 的 LVS 驗證,所有組件的所有數據都必須可用。例如,FOWLP 設計人員需要 die1 版圖設計數據庫、die2 版圖設計數據庫、FOWLP 設計數據庫,以及某種形式的 FOWLP 系統源網表。現在,如果 FOWLP 設計數據庫(由封裝團隊負責)已準備就緒,而芯片數據庫(由 SoC 團隊負責)仍在開發中,將會出現什么情況?對 FOWLP 設計人員來說,如果等到所有芯片構建完畢并經過驗證再運行 FOWLP LVS,結果發現 FOWLP 設計數據庫中充斥了短路、開路和其他錯誤,將是完全行不通的。設計人員必須在完成完整的 LVS 驗證之前的早期驗證期間,采取一些做法來修復明顯的問題。為了實現和支持這種早期驗證,EDA 公司必須提供一種自動化 HDAP LVS 檢查方法,并且能夠在尚未取得所有最終組件的情況下運行。

設計依賴性

在 SoC LVS 驗證中,LVS 規則集僅依賴于 SoC 技術節點信息(即 GDSII 層)。但是,HDAP LVS 卻增加了另一個復雜問題:芯片布局。HDAP LVS 規則集依賴于中介層、 die1、die2 等 GDSII 層,也依賴于芯片(以及 2.5D 設計的中介層)的布局位置。反過來,這些信息則高度依賴于 HDAP 設計本身。晶圓代工廠/OSAT 構建 HDAP LVS 規則集將是一個面面俱到的過程,需要考慮所有可能的芯片和中介層布局組合。盡管 “一個中介層上兩個芯片” 的設計在過去是可能的,但隨著 HDAP 中的裸片和基底數量的增加,很快就變得不切實際了。

04克服數據 “不完整性”

因此,我們認識到,與已經存在了幾十年的 SoC 驗證流程相比,設計端的 HDAP 驗證流程還遠遠不夠成熟。這導致每個設計公司(以及潛在的每個 HDAP 設計周期)都可能具有不同類型的驗證數據。這種情況下,EDA 公司為 HDAP 驗證強制執行某一組數據要求是不切實際的。相反,EDA 公司必須非常靈活,從某種意義上說,應始終能夠利用可獲取的數據實現某種類型的 HDAP LVS 驗證。下面我們來探討一下,不同情況下的不同流程中的 LVS 驗證可能是什么樣子。

不含原理圖/設計意圖的封裝/中介層連接檢查

采用標準格式的 “源網表” 在封裝領域是個相對較新的概念。傳統上,封裝設計人員使用手動電子表格來規劃從裸片到封裝再到印刷電路板 (PCB) 上的外部 I/O 的連接。盡管在 HDAP 驗證中應用這類方法非常困難,但一些設計人員出于不同的原因(傳統、管腳數目太少等)仍在使用電子表格。不用說,根據設計公司的舊有方法,這些電子表格可能有不同的格式和組織形式,所以 EDA 公司很難支持所有可能的電子表格。

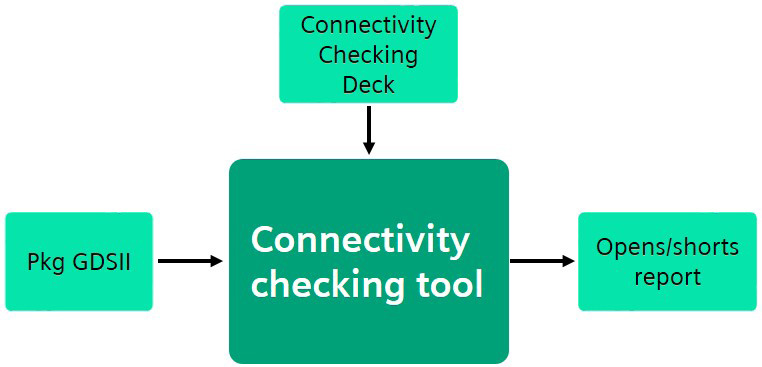

好吧,如果各種舊式電子表格不可用,設計人員還有封裝設計數據庫。難道就沒有什么簡單的開路/短路檢查辦法嗎?事實上,可能真有。鑒于設計人員擁有的數據量(僅限于封裝設計數據庫),EDA 工具可以使用一種仍對他們有用的簡單方法:

■ 如果封裝設計數據庫中的兩個形狀具有相同的文本標簽,但在物理上是斷開連接的,則應報告為 “開路”

■如果封裝設計數據庫中的兩個形狀具有不同的文本標簽,但在物理上是相連接的,則應報告為 “短路”

盡管這不是全面的 LVS(因為沒有可比較的設計意圖),但如果還沒有源網表,則仍不失為一種有價值的開路/短路檢查。下圖顯示了這種簡單的開路/短路檢查器的方框圖。

圖:不含設計意圖的封裝連接檢查

不含裸片管腳的封裝/中介層 LVS

下一個案例介紹一種更復雜的情形。驗證數據現在包括封裝設計數據庫和源網表,這樣設計人員應該能夠運行真正的 LVS 驗證。他們的第一個念頭可能是,使用與 SoC LVS 相同的 LVS 工具和方法。但是,SoC 中的 LVS 概念依賴于 SoC 版圖設計數據庫和源網表中的“器件”的存在。器件可以是有源(晶體管)或無源(電阻器、電容器等)器件。由于大多數 2.5D-IC 和 FOWLP 設計不含任何器件(僅包含金屬布線),所以 SoC LVS 工具并不實用,因為它們并非針對 HDAP LVS 問題。

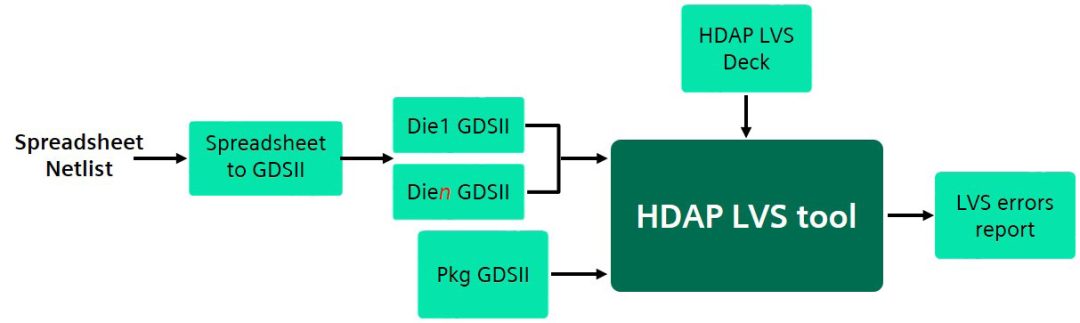

更為可行的解決方案是使用 HDAP 裝配級 LVS 工具,默認情況下,這些工具會考慮封裝中不存在器件的情況。但此類工具不僅需要用于裝配級 LVS 的封裝版圖設計數據庫,還需要裸片的版圖設計數據庫。不過,這一限制是可以解決的。裝配級 LVS 工具經過強化,可以從輸入電子表格網表(其中包括裸片凸塊 (x,y) 坐標和管腳名稱)自動生成“占位符”裸片凸塊(表示裸片)。然后可以在裝配設計數據庫中使用此 “裸片占位符” 設計數據庫。設計人員僅使用封裝版圖設計數據庫和輸入電子表格網表,就能成功運行 HDAP LVS。下圖顯示了不含裸片管腳的 HDAP LVS 流程的方框圖。

圖:不含裸片管腳的 HDAP LVS

盡管這類流程為客戶提供了價值(捕獲封裝設計數據庫中的任何物理短路/開路),但不能保證完整的裝配能夠成功運行。如果 HDAP 中的裸片與封裝之間存在錯位怎么辦?

裝配級 LVS/LVL

在 HDAP 中,版圖與版圖比較 (LVL) 驗證跟 LVS 同樣重要,尤其在需要旋轉或縮放時(例如,將裸片收縮 10%,旋轉 90°,然后布置在封裝上)。設計人員必須確保,經過這類處理之后,封裝凸塊與裸片凸塊之間仍有足夠的重疊。

僅幾何裸片接口

如果封裝設計人員能夠獲得裸片接口(凸塊)GDSII 層,那么除了封裝 LVS 之外,他們還可以執行 LVL 驗證。設計人員可以使用 EDA 工具自動將裸片布置在封裝/中介層的頂面,并驗證對齊情況(根據需要)。

從連接的角度來看,將裸片和封裝都納入裝配級 LVS 時,通常會面臨一個挑戰:SoC 團隊可能使用與封裝團隊不同的方法來命名裸片管腳/網絡。SoC 設計人員的 SoC 版圖設計數據庫中可能有一個名為 “A” 的裸片管腳,而在系統源網表和封裝設計數據庫中,該管腳被稱為 “A_B”。這種差異會導致許多虛假的 LVS 違規。但這一狀況與此流程無關,因為 HDAP 設計人員從裸片導入的數據是 “接口物理幾何形狀”,而不是“接口邏輯管腳”。

也就是說,如果 SoC 設計數據庫或封裝設計數據庫中存在額外管腳,則在使用此流程時不會捕獲到該管腳。

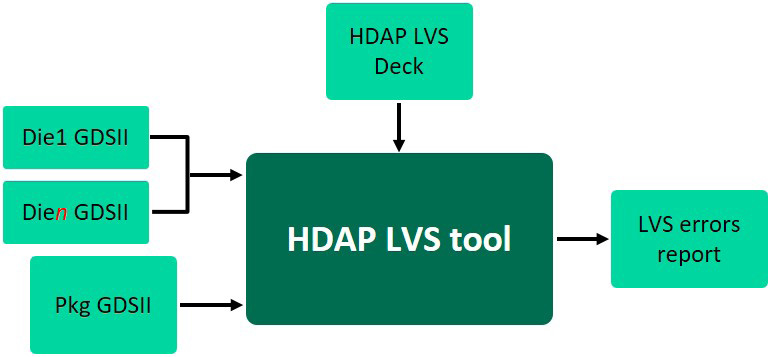

幾何裸片接口 + 邏輯裸片管腳

在此流程中,來自裸片的所有接口信息(幾何形狀和管腳)全部可用。HDAP 設計人員可以將此流程作為 signoff 流程來運行,因為其中包括了綜合驗證所需的全部數據。設計人員可以驗證所有可能的違規:

■ 裝配級 LVS

■裝配級 LVL

■額外/缺失的管腳

至于 SoC 與封裝之間管腳名稱/網絡名稱不匹配的挑戰, EDA 公司提供了新穎的方法來解決這類問題,避免導致虛假的 LVS 違規。例如,HDAP 設計人員可以在輸入中將這類不一致標注為豁免。下圖顯示了包含裸片管腳的裝配級 LVS/LVL 流程。

圖:裝配級 LVS/LVL,包括裸片管腳

05HDAP LVS 流程

西門子提供了完整的自動化流程,可支持 HDAP 設計人員運行靈活的 HDAP LVS 驗證流程,同時兼顧各種級別的數據 “不完整性” Xpedition Substrate Integrator (xSI) 工具可執行 HDAP 系統級連接關系管理和規劃。xSI 工具生成系統源網表(采用電子表格格式),其中包括連接信息和裸片/封裝管腳的 x,y 位置。利用 Calibre 3DSTACK 工具可實現靈活的 HDAP 物理驗證(LVS 和 LVL),執行上述任意和所有三種流程。Calibre 3DSTACK HDAP 規則集可使用 xSI 工具自動生成,以兼顧 HDAP 規則集的設計依賴性。

06總結

隨著 HDAP 技術逐漸成為主流,HDAP 設計人員需要來自晶圓代工廠/OSAT 和 EDA 公司的可靠設計與驗證流程。但與成熟的傳統 SoC 驗證流程相比,目前可用的 HDAP 驗證流程還遠遠不夠成熟。在許多情況下,HDAP LVS “sign off”所需的驗證數據可能并不完整。EDA 公司必須提供工具和流程來兼顧各種級別的數據可用性,同時繼續支持 HDAP 設計人員執行有用且有價值的 HDAP LVS 流程。

-

芯片

+關注

關注

463文章

54320瀏覽量

468515 -

集成電路

+關注

關注

5462文章

12653瀏覽量

375466 -

LVS

+關注

關注

1文章

38瀏覽量

10521 -

先進封裝

+關注

關注

2文章

558瀏覽量

1055

原文標題:一文了解 HDAP LVS/LVL 驗證

文章出處:【微信號:Mentor明導,微信公眾號:西門子EDA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

請教:6G 確定性通信原型驗證,FPGA+SDR 方案該怎么搭?

RDMA設計35:基于 SV 的驗證平臺

_timer_start()函數功能雖然正常,但實現是否未達預期,怎么處理?

如何驗證電能質量在線監測裝置的抗干擾能力?

ulog_tag_lvl_filter_set()函數無法實現按照文檔說明那樣實現按模塊過濾,怎么解決?

如何驗證硬件冗余設計的有效性?

NVMe高速傳輸之擺脫XDMA設計24: UVM 驗證包設計

電能質量在線監測裝置數據驗證的流程是什么?

芯華章RISC-V敏捷驗證方案再升級

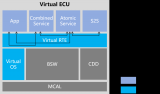

技術解讀 | 光庭信息虛擬ECU技術賦能SOA化MCU軟件的早期驗證與集成加速

《電子發燒友電子設計周報》聚焦硬科技領域核心價值 第14期:2025.06.2--2025.06.6

芯華章攜手EDA國創中心推出數字芯片驗證大模型ChatDV

硬件輔助驗證(HAV) 對軟件驗證的價值

FPGA EDA軟件的位流驗證

面向HDAP設計的LVS/LVL驗證

面向HDAP設計的LVS/LVL驗證

評論