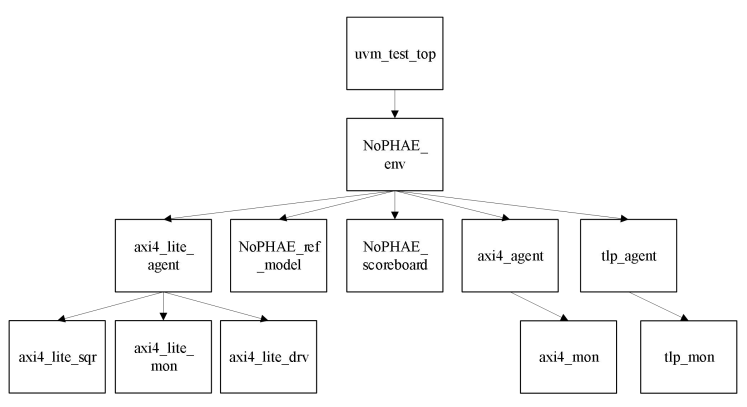

UVM 驗證包設計結構如圖 1 所示。 UVM 驗證包的主要功能是對 DUT 提供激勵, 仿真驗證對應的功能, 并對測試結果進行自動對比分析與統計。 驗證包包含一個NoPHAE_env 驗證環境, 驗證環境下包含 axi4_lite_agent、 axi4_agent、 tlp_agent、NoPHAE_ref_model、 NoPHAE_scorebarod 組件。

圖1 UVM 驗證包設計結構圖

Axi4_lite_agent 負責對接 AXI4-Lite 接口。 在 DUT 使用的三個接口中, AXI4-Lite接口用于連接系統控制模塊, 實現系統控制功能, 所以激勵的添加主要通過 AXI4-Lite接口。 在 axi4_lite_agent 中包含 axi4_lite_drv、 axi4_lite_mon、 axi4_lite_sqr 三個組件,分別提供 axi4_lite 總線的主機驅動器( driver)、 監測器( monitor) 和序列發生器(sequencer)。 驅動器從序列發生器獲取事務, 并將其轉換為 AXI4-Lite 接口信號;監測器從接口上監測信號, 將其組成事務發送到參考模型和計分板; 序列發生器根據測試用例產生事務。

Axi4_agent 負責監測 AXI4 總線接口。 由于 AXI4 總線接口用于進行數據傳輸,在驗證平臺中該總線接口實際與 AXI BRAM IP 對接, 不需要添加特殊的激勵。 因此, axi4_agent 中只包含了一個 monitor, 將總線信號轉換為 AXI4 事務發送到計分板。

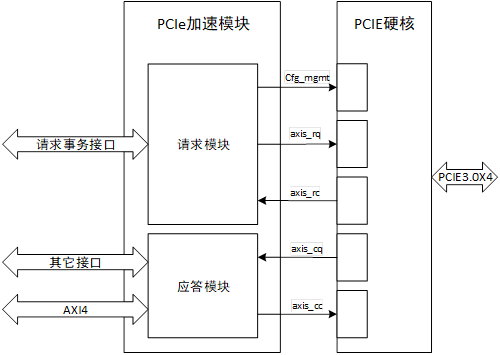

Tlp_agent 負責監測分離的 PCIE 集成塊接口, 分別是一個 cfg_mgmt 接口, 四個axis 接口, 這些接口信號均可轉換為 PCIe TLP 事務。 這些接口與 NVMe 子系統模型對接, 因此 tlp_agent 中只包含一個 monitor, 將監測到的 PCIe TLP 事務發送到計分板。

NoPHAE_ref_model 是模擬 DUT 設計功能的參考模型, 該模型從 axi4_lite_agent的監測器獲取寄存器配置信息, 根據這些信息將預期的 AXI4 事務和 PCIe TLP 事務發送到 NoPHAE_scorebarod。

NoPHAE_scorebarod 計分板負責收集各個接口監測器監測到的傳輸事務, 并將這些事務與參考模型給出的預期事務進行對比, 并統計對比結果, 根據結果判斷測試用例執行是否成功。

B站已給出相關性能的視頻,如想進一步了解,請搜索B站用戶:專注與守望

鏈接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click

-

PCIe

+關注

關注

16文章

1464瀏覽量

88567 -

UVM

+關注

關注

0文章

183瀏覽量

20040 -

高速存儲

+關注

關注

0文章

15瀏覽量

6089 -

nvme

+關注

關注

0文章

299瀏覽量

23848

發布評論請先 登錄

NVMe高速傳輸之擺脫XDMA設計九:隊列管理模塊設計(上)

NVMe高速傳輸之擺脫XDMA設計18:UVM驗證平臺

NVMe高速傳輸之擺脫XDMA設計14: PCIe應答模塊設計

NVMe高速傳輸之擺脫XDMA設計20: PCIe應答模塊設計

NVMe高速傳輸之擺脫XDMA設計23:UVM驗證平臺

NVMe高速傳輸之擺脫XDMA設計30: NVMe 設備模型設計

NVMe高速傳輸之擺脫XDMA設計42:DMA 讀寫功能驗證與分析

NVMe高速傳輸之擺脫XDMA設計43:如何上板驗證?

NVMe IP高速傳輸卻不依賴XDMA設計之八:系統初始化

NVMe IP高速傳輸卻不依賴XDMA設計之九:隊列管理模塊(上)

NVMe高速傳輸之擺脫XDMA設計24: UVM 驗證包設計

NVMe高速傳輸之擺脫XDMA設計24: UVM 驗證包設計

評論