源漏擴展結構(Source/Drain Extension,SDE)在控制 MOS 器件的短溝道效應中起到重要作用。SDE(源漏擴展結構)引入了一個淺的源漏擴展區,以連接溝道和源漏區域。結深的微縮歸因于 SDE 深度的降低。隨著 CMOS尺寸的降低,為控制短溝道效應,結深也需要相應的降低。然而,降低源漏擴展區的深度會導致更高的電阻。這兩個互相矛盾的趨勢要求新的工藝技術能夠在更淺的區域形成高活化和低擴散的高濃度結。

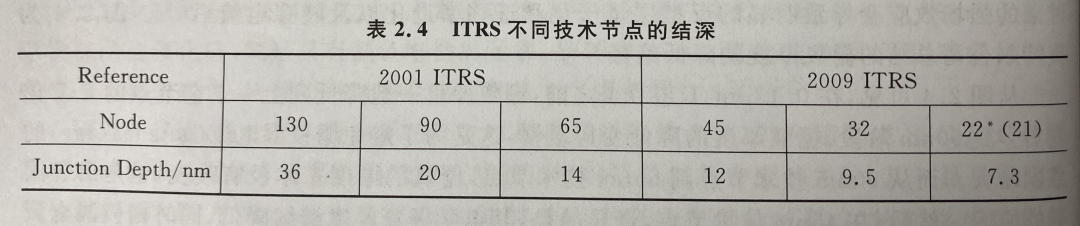

根據ITRS 提供的數據,不同技術節點的結深歸納如表2.4所示。

結(junction)的制造工藝包含離子注入工藝和注入后退火工藝。離子注入需要小心控制以在最小化的注入損傷下,在近表面獲得高摻雜濃度。為滿足上述需求,新的工藝技術,比如無定型化技術、分子離子注入技術和冷注入技術,已經得到應用。為得到摻雜劑的高活化和有限的摻雜劑擴散,注入后退火的熱預算非常關鍵。由于將摻雜原子置入晶格中的活化過程相比摻雜劑的擴散過程需要更高的活化能,快速升降溫的熱過程有利于高活化和低擴散。針對該目的而開發的毫秒級和亞毫秒級的退火技術已經應用于大規模工業生產。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

工藝

+關注

關注

4文章

716瀏覽量

30369 -

制造工藝

+關注

關注

2文章

214瀏覽量

21303 -

MOS

+關注

關注

32文章

1749瀏覽量

100974

原文標題:源漏工程

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

漏源電壓VDS相關資料下載

1、電壓負載 在具有直流穩壓大功率電路的應用中,通常首先考慮選擇漏源電壓VDS。這里的理由是,在實際工作環境中,MOSFET的最大峰值漏極-源極電壓小于器件規格的標稱

發表于 11-12 08:12

漏源電壓振蕩嚴重

全橋單向DC-DC變換器中,MOSFET漏源電壓波形如圖所示振蕩很嚴重,這種現象在1kHz的時候不明顯,50khz的時候如圖所示很明顯,請問是為什么?

發表于 04-25 11:19

PNP與NPN哪個是“源”與”漏“的渾水

源型與漏型是PNP與NPN放大電路的電流流向的一種形象化表述,最初是由日系PLC引入這樣的簡稱,在日系語系用中文字表達的一種方式,在原來的中國學校教育中并不怎么使用“源型”與“漏型”這

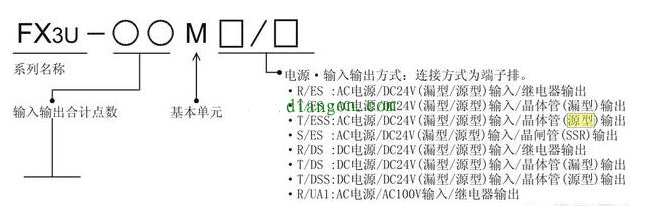

三菱PLC源型和漏型的區別

三菱plc源型和漏型的區別,咱們先說下三菱plc的基本單元的輸入驅動電源有兩種,一種是交流電源100V輸入驅動(少見),一種是直流電源24V輸入驅動(常見的),交流型的不存在漏源型之分

發表于 03-25 09:30

?3.3w次閱讀

柵極源極漏極怎么區分?漏極 源極 柵極相當于三極管的哪極?

什么是漏極?什么是源極?什么是柵極?柵極源極漏極怎么區分?漏極 源極 柵極相當于三極管的哪極?

mos芯片源極漏極柵極在哪 mos管怎么判斷漏柵源極

之間的連接是理解該器件工作原理的關鍵。 MOS管結構簡介: MOS管是由一片半導體材料(通常是硅)構成的,通過在硅片上摻雜不同類型的雜質形成兩個PN結。這些雜質摻入區域形成了源極和漏極,而柵極是通過在硅片上形成一層金屬(通常是鋁

MOS管源極和漏極是什么意思

(Source, S)和漏極(Drain, D)是兩個關鍵的電極,它們與柵極(Gate, G)共同構成了MOS管的基本結構。以下是對MOS管源極和漏極的詳細解釋,包括它們的定義、功能、

源漏嵌入SiC應變技術簡介

源漏區嵌入SiC 應變技術被廣泛用于提高90nm 及以下工藝制程 NMOS 的速度,它是通過外延生長技術在源漏嵌入 SiC 應變材料,利用硅和碳晶格常數不同,從而對溝道和襯底硅產生應力

晶體管的漏極與源極有什么區別

在探討晶體管的漏極(Drain)與源極(Source)的區別時,我們首先需要明確晶體管的基本結構和工作原理。晶體管,尤其是場效應晶體管(FET),是一種通過控制輸入回路的電場效應來控制輸出回路電流的電子器件。在FET中,

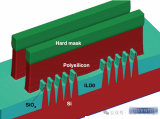

FinFet Process Flow-源漏極是怎樣形成的

本文介紹了FinFet Process Flow-源漏極是怎樣形成的。 在FinFET制造工藝中,當完成偽柵極結構后,接下來的關鍵步驟是形成源漏

源漏擴展結構概述

源漏擴展結構概述

評論