本文介紹了FinFet Process Flow-源漏極是怎樣形成的。

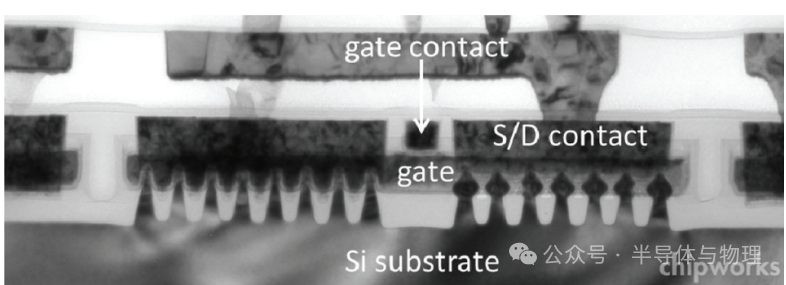

在FinFET制造工藝中,當完成偽柵極結構后,接下來的關鍵步驟是形成源漏極(Source/Drain)。這一階段對于確保器件性能和可靠性至關重要。以下是詳細的工藝流程描述,特別關注PMOS和NMOS源漏極形成的每一步及其作用。

FinFet Process Flow-Fin的形成,FinFet Process Flow-啞柵極的形成。

一、為柵極側壁沉積

晶圓清潔與側壁沉積

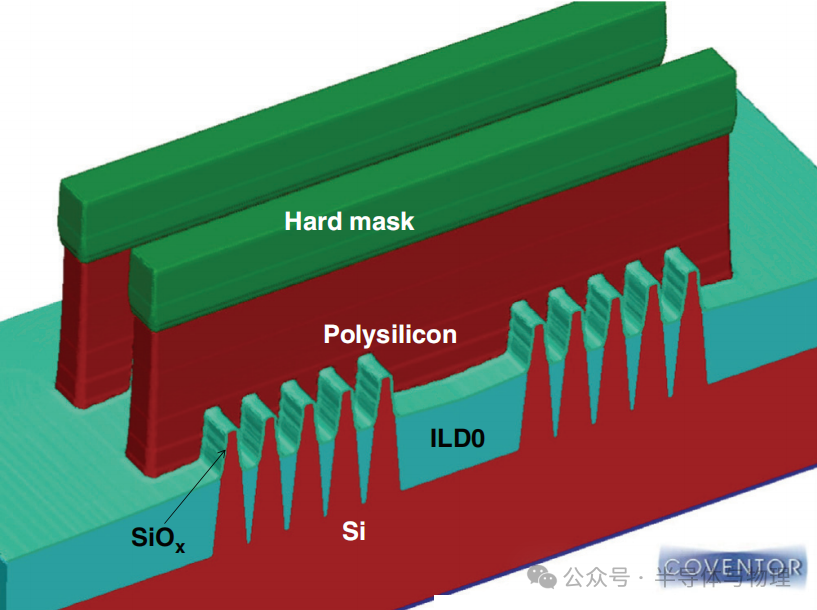

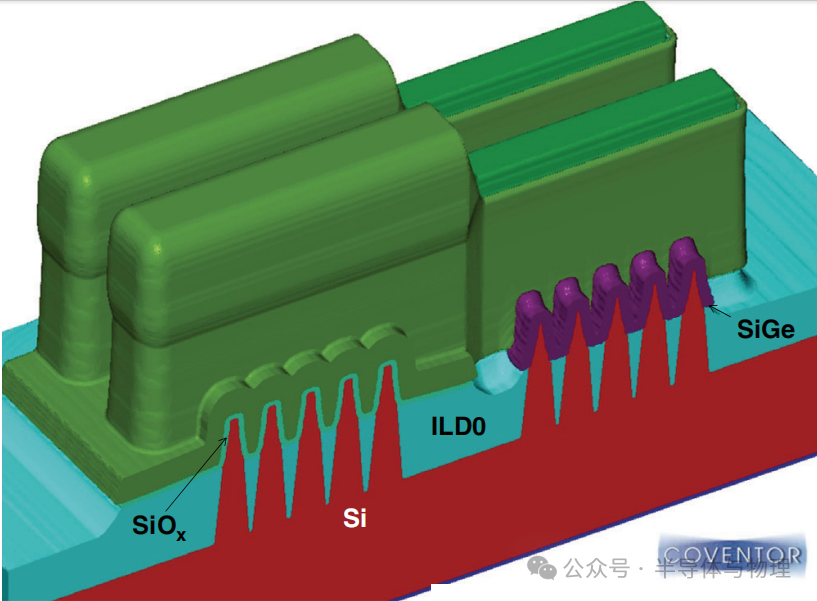

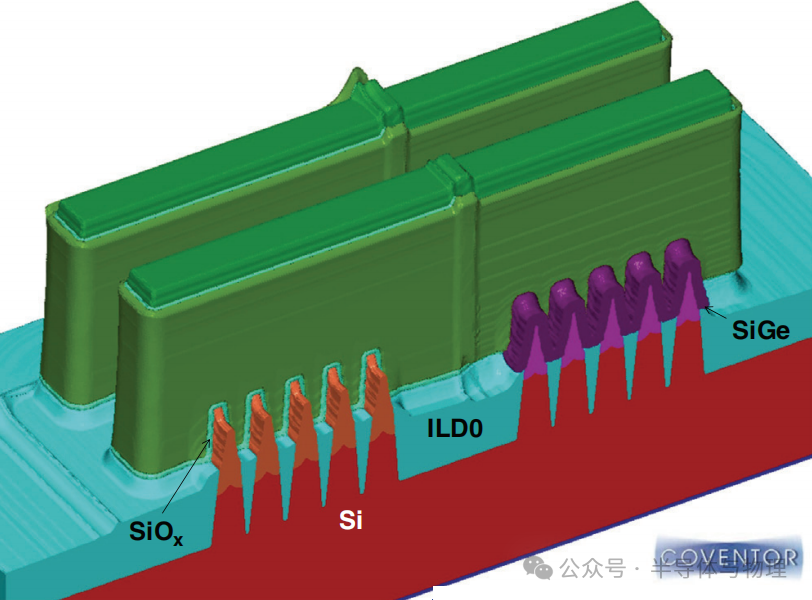

首先,在完成偽柵極結構后的晶圓上進行徹底清潔,以去除任何可能影響后續步驟的污染物。接著,沉積一層薄的側壁(通常為氧化硅SiOx)芯片制造:薄膜工藝,這層材料作為后續側壁間隔物的基礎,并有助于保護鰭片免受直接損傷。

二、PMOS源漏極形成

PMOS光刻芯片制造:光刻工藝原理與流程

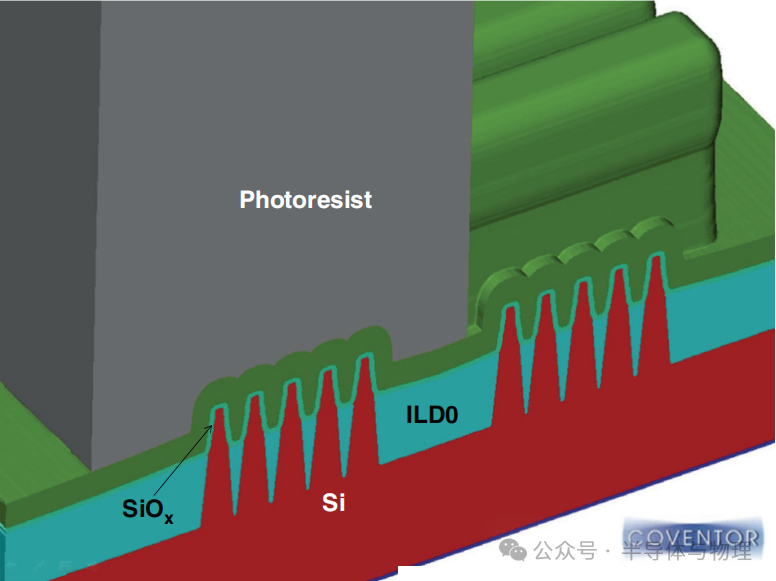

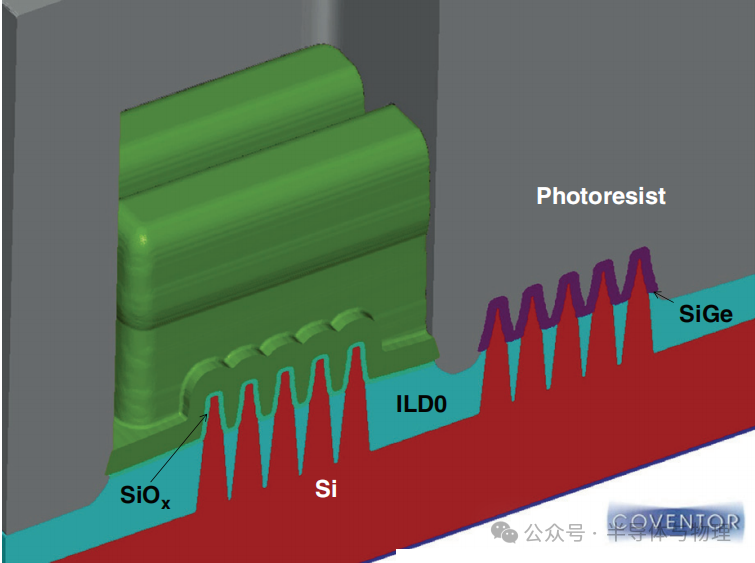

為了允許PMOS源漏極的形成,應用一個PMOS掩模,使得NMOS區域被光刻膠(PR)覆蓋。

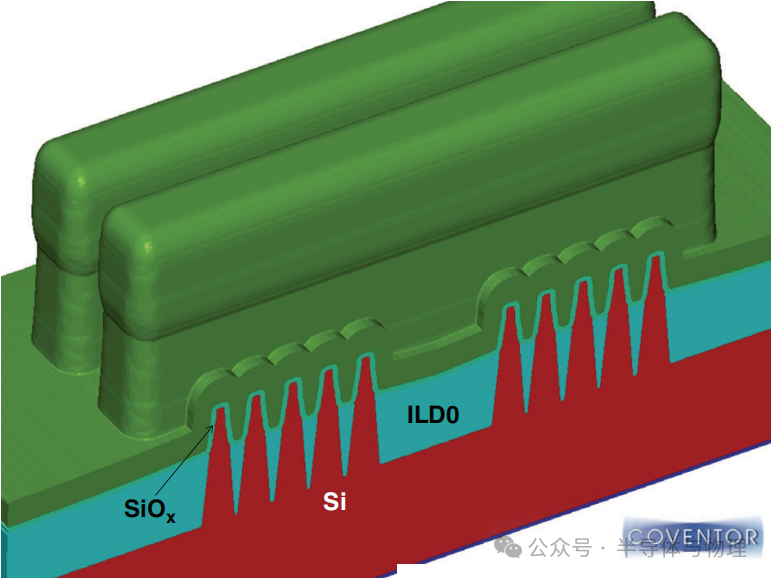

PMOS側壁間隔物蝕刻與鰭片間隔物移除

在PMOS區域,通過蝕刻去除側壁間隔物并移除鰭片上的SiO2間隔物。此步驟為后續的選擇性外延生長(Selective Epitaxial Growth,芯片制造中的SiGe)做好了準備。

光刻膠剝離與晶圓清洗

完成上述蝕刻后,剝離光刻膠并清洗晶圓,以清除任何殘留物質,保證接下來的生長過程不受污染。

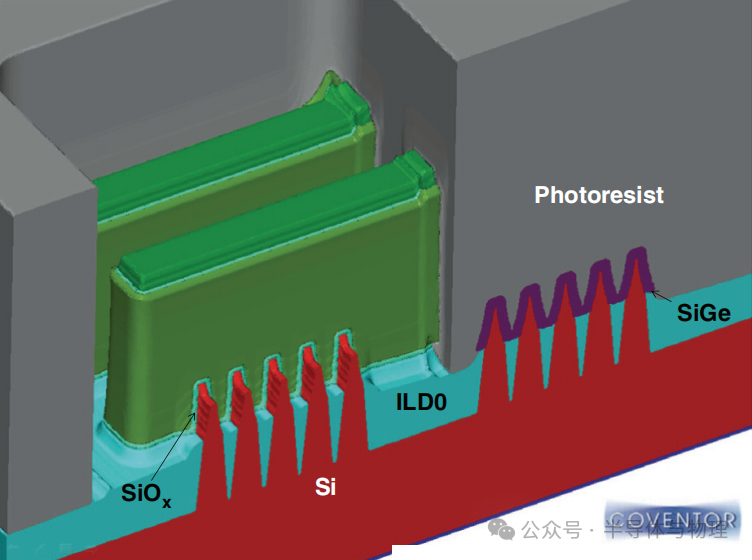

硅凹陷與SiGe選擇性外延生長

接下來,通過蝕刻使硅表面略微凹陷,然后在這些凹陷處生長重摻雜的p型SiGe。選擇性外延生長技術用于在此處形成高質量的SiGe晶體芯片制造中的SiGe,它不僅增加了PMOS器件的載流子遷移率,還提高了其性能。至此,PMOS器件的源漏極形成完畢。

三、NMOS源漏極形成

NMOS光刻

接下來,切換到NMOS區域,應用相應的光刻膠掩模,這次是PMOS區域被覆蓋,NMOS區域暴露出來。目的是為接下來的NMOS源漏極形成做準備。

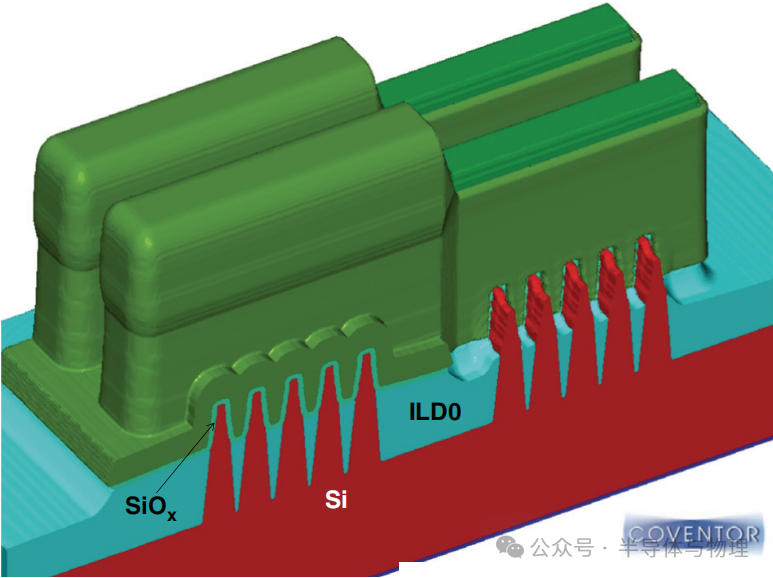

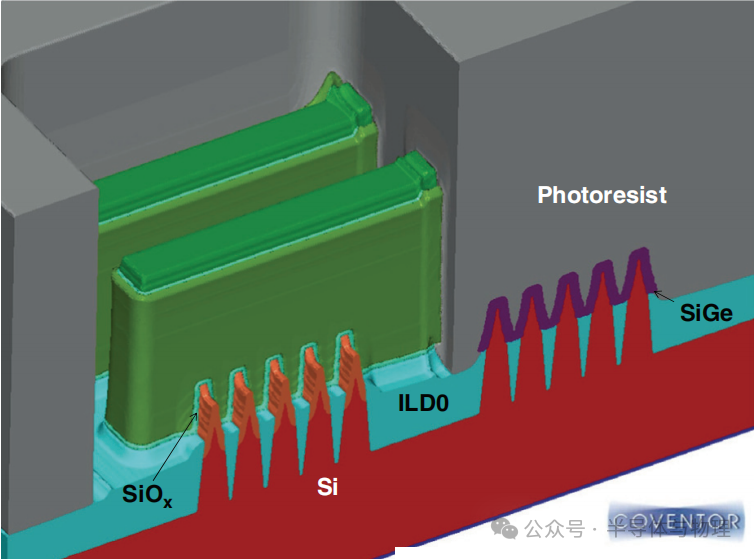

NMOS側壁間隔物蝕刻與鰭片間隔物移除

類似于PMOS的處理,蝕刻NMOS側壁間隔物并移除NMOS鰭片上的間隔物。

這是為了確保接下來的n型離子注入可以準確地定位到目標位置。

n型離子注入芯片制造:離子注入工藝

執行n型離子注入以重摻雜NMOS源漏極。該步驟旨在將大量的n型雜質引入到硅中,以創建低電阻的源漏區。

光刻膠剝離與晶圓清洗

再次剝離光刻膠并清洗晶圓,確保沒有殘留物質干擾接下來的退火過程。

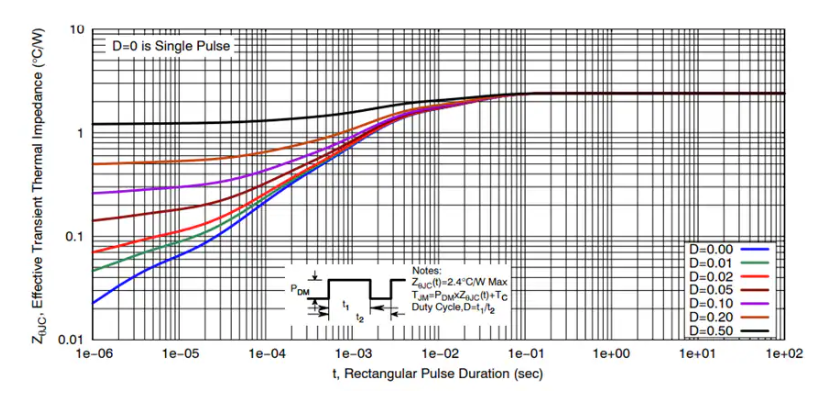

退火芯片制造:退火工藝

最后,通過退火激活摻雜劑。退火過程可以使摻雜原子進入硅晶格的適當位置,從而優化電學特性。

-

漏極

+關注

關注

0文章

35瀏覽量

11023 -

FinFET

+關注

關注

12文章

260瀏覽量

92302 -

Process

+關注

關注

0文章

17瀏覽量

12484

原文標題:FinFet Process Flow-源漏極形成

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

選型手冊:VS6808DH 共漏極雙通道 N 溝道增強型功率 MOSFET 晶體管

NVTFWS002N04XM功率MOSFET技術解析與應用指南

芯片漏印工裝

RDS(on)低至8.6mΩ,揚杰推出200V MOSFET Gen2.0系列

CYW20704 的 UART 4 針(TX/RX/CTS/RTS)是什么形式(推拉或漏極開路)嗎?

體硅FinFET和SOI FinFET的差異

源漏擴展結構概述

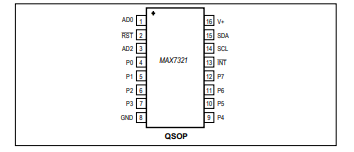

MAX7321 I2C端口擴展器,具有8路漏極開路I/O技術手冊

CCG5的VBUS_C_CTRL引腳預計是漏極開路輸出,但在這種情況下,漏極電流有多大?

半導體靜態參數都有哪些呢?你了解多少?

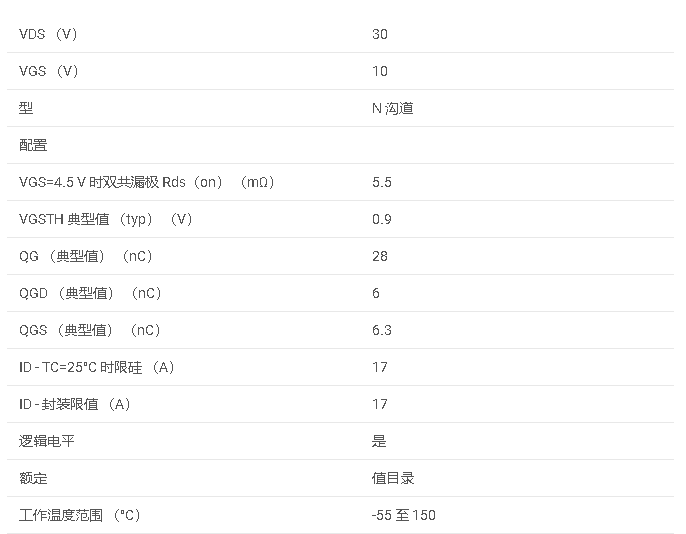

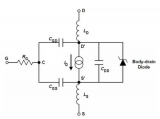

CSD87313DMS 30V、N 通道 NexFET? 功率 MOSFET、雙共漏 SON 3mm x 3mm、5.5mOhm數據手冊

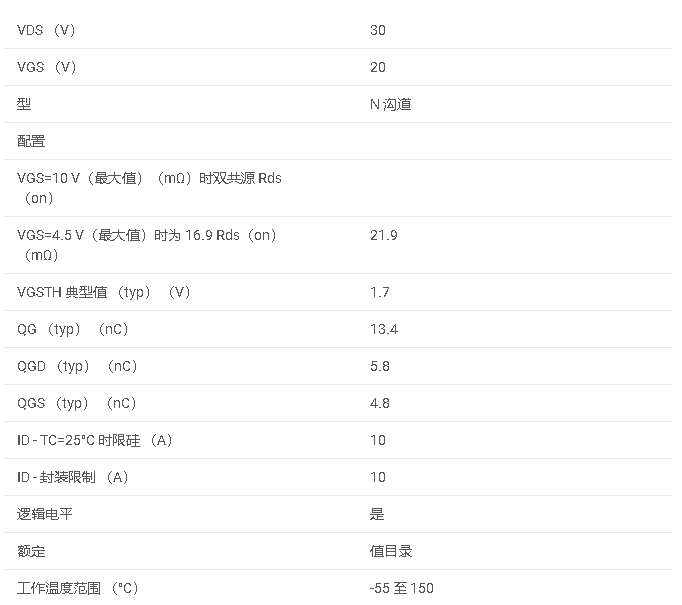

CSD87503Q3E 30V、N 通道 NexFET? 功率 MOSFET、雙共源 SON 3mm x 3mm、21.9mOhm技術手冊

FinFet Process Flow-源漏極是怎樣形成的

FinFet Process Flow-源漏極是怎樣形成的

評論