混合鍵合3D芯片技術將拯救摩爾定律。

為了繼續縮小電路尺寸,芯片制造商正在爭奪每一納米的空間。但在未來5年里,一項涉及幾百乃至幾千納米的更大尺度的技術可能同樣重要。

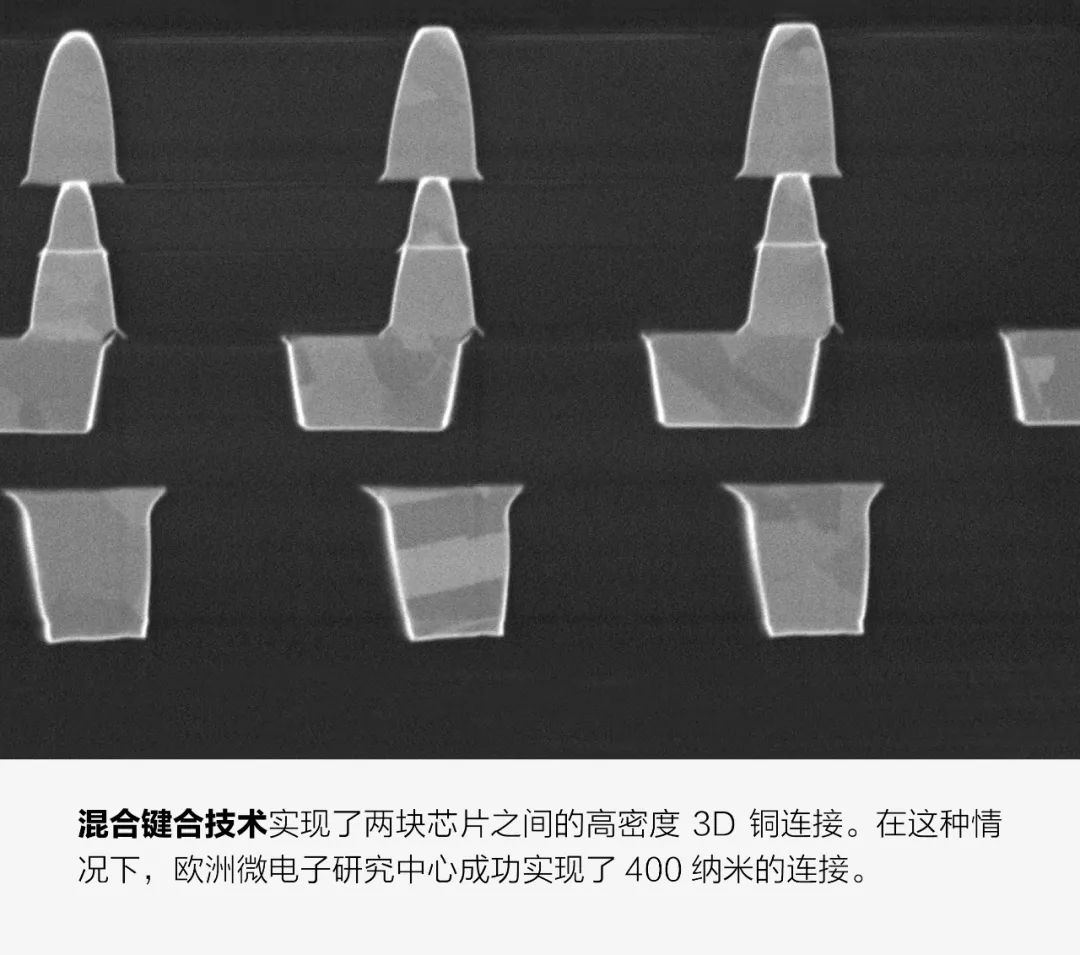

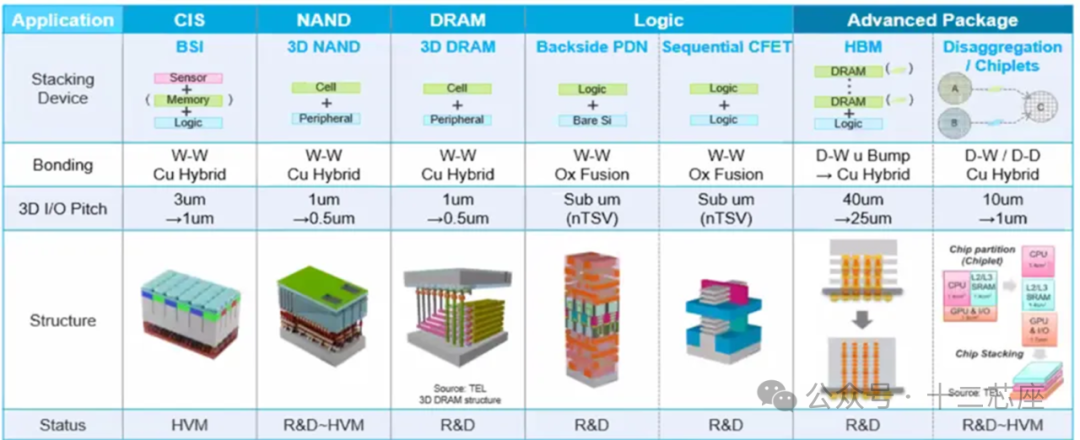

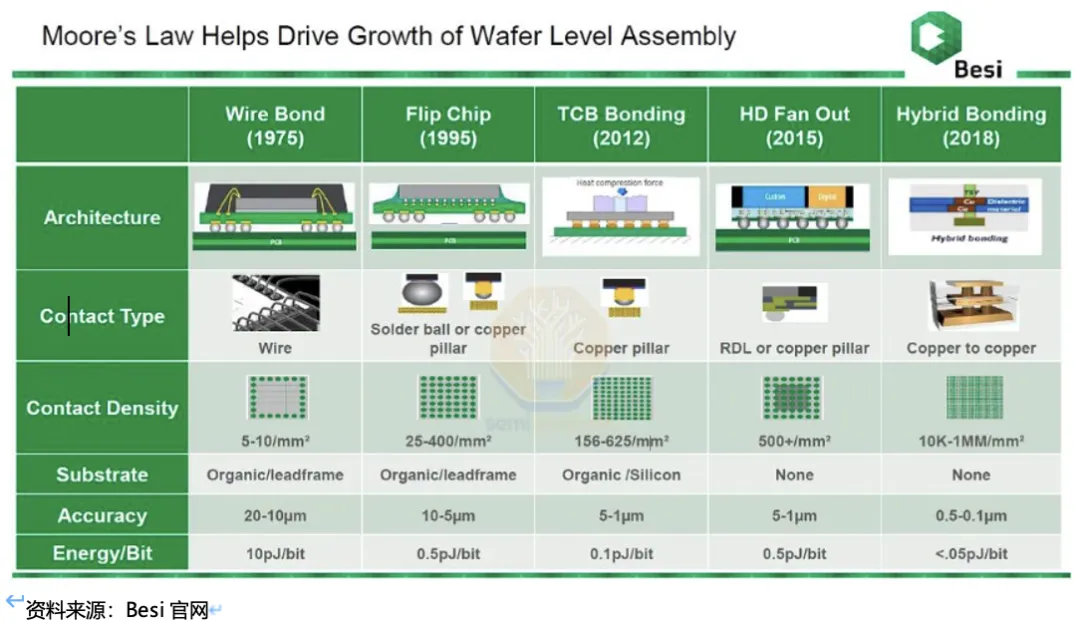

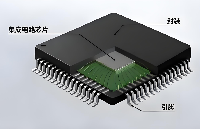

這項技術被稱為“混合鍵合”,可以將兩塊或多塊芯片疊放在同一個封裝中。這使芯片制造商能夠增加處理器和內存中的晶體管數量,雖然晶體管的縮小速度已普遍放緩,但這曾推動摩爾定律發展。2024年5月,在美國丹佛舉行的IEEE電子器件與技術大會(ECTC)上,來自世界各地的研究團隊圍繞這一技術公布了多項研究改進,其中一些成果可能會產生創紀錄的3D堆疊芯片連接密度:每平方毫米硅片約700萬個連接。

在IEEE電子器件與技術大會上,來自英特爾公司的石毅(Yi Shi,音)告訴與會工程師們,由于半導體工藝的新特性,所有這些連接都是必需的。摩爾定律現在被一種稱為系統技術協同優化(STCO)的概念主宰,根據這一概念,芯片的各項功能(如緩存、輸入/輸出和邏輯)分別使用最適合的技術制造。然后,可以采用混合鍵合和其他先進封裝技術將這些子系統組裝起來,使它們像單塊硅片一樣全力工作。但只有在連接密度足夠高,且在不同硅片之間傳輸數據的延遲或能耗都很小的情況下,這才能實現。

在所有先進封裝技術中,混合鍵合提供了最高密度的垂直連接。因此,Yole集團的技術和市場分析師加布里埃拉?佩雷拉(Gabriella Pereira)表示,它是先進封裝行業中增長最快的一部分。根據Yole集團的預測,到2029年,先進封裝行業整體市場規模將增長2倍以上,達到380億美元,屆時,混合鍵合預計將占據其中約一半的市場份額,雖然目前它僅占市場的一小部分。

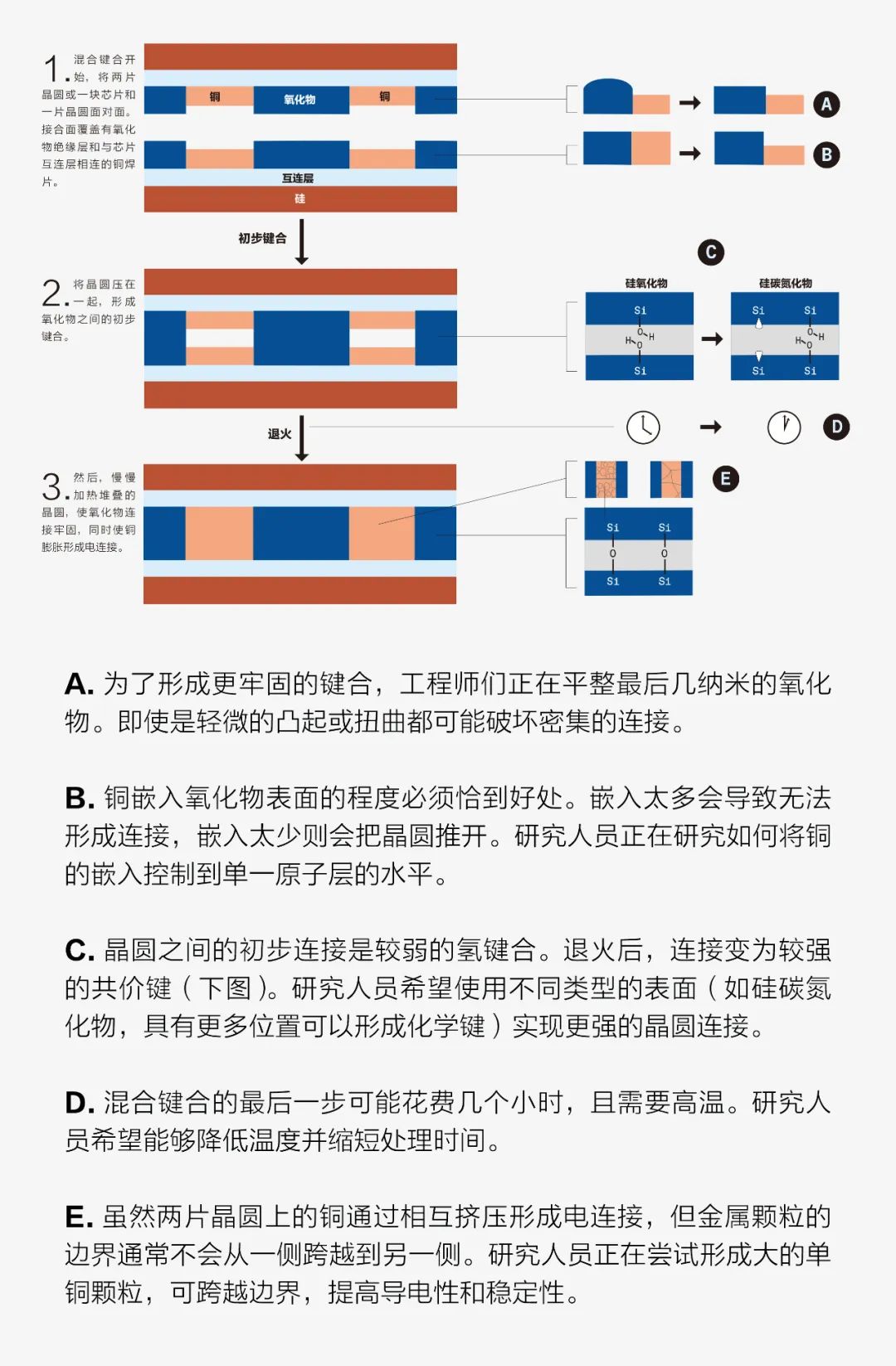

在混合鍵合中,每塊芯片的頂面均放置銅焊盤,周圍包著絕緣層,通常是硅氧化物,銅焊盤嵌在絕緣層表面。在對氧化物進行化學改性后,將兩塊芯片面對面擠壓在一起,使每塊芯片上嵌入的銅焊盤相互對齊。然后慢慢加熱夾層,使銅膨脹填滿間隙并熔化,從而將兩塊芯片連接起來。

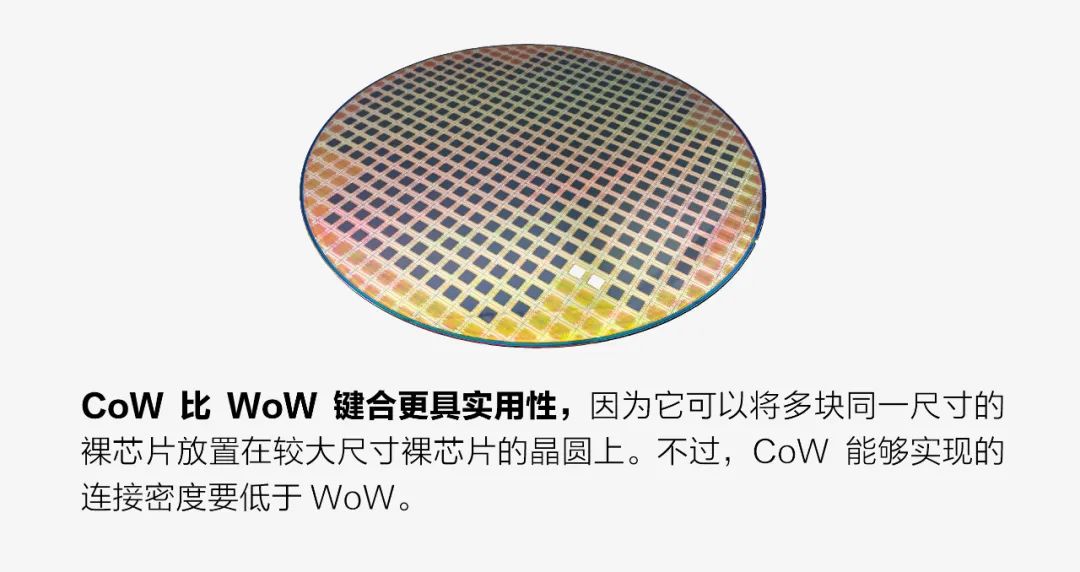

混合鍵合可以將一種尺寸的單塊芯片附著到一個更大尺寸芯片的完整晶圓上,也可以將兩片相同尺寸的完整晶圓鍵合在一起。佩雷拉表示,由于后者在相機芯片中得到了應用,其工藝比前者更加成熟。例如,歐洲微電子研究中心(Imec)的工程師們創造出了一些有史以來最密集的晶圓對晶圓鍵合,鍵合距離(或稱為間距)僅400納米。但對于芯片與晶圓鍵合,歐洲微電子研究中心實現的間距僅為2微米。

相比目前正在生產中的先進3D芯片的9微米間距,歐洲微電子研究中心的2微米間距是巨大的進步。而且比前一代技術(間距幾十微米的焊料“微凸塊”)有了更大的飛躍。

“使用現有設備,將晶圓與晶圓對齊比將芯片與晶圓對齊更容易。大多數微電子工藝都是為(整片)晶圓設計的。”法國研究機構CEA Leti的集成與封裝科學負責人簡-查爾斯?蘇里奧(Jean-Charles Souriau)說。但晶圓上芯片(CoW,或晶圓上裸芯片)技術正在高端處理器中大放異彩,如在AMD處理器中,這項技術被用于組裝其新型中央處理器(CPU)和人工智能加速器中的計算核心和緩存。

在這兩種場景中,為了進一步縮小間距,研究人員致力于使表面更加平整、鍵合晶圓粘接更好,并減少整個工藝的時間和復雜度。如果做到這一點,就可能會徹底改變芯片的設計方式。

間距緊密的WoW

最近的晶圓上晶圓(WoW)研究實現了 360到500納米的最緊湊間距,這要求在平整度方面投入巨大的精力。要以100納米級的精度將兩片晶圓鍵合在一起,整片晶圓必須幾乎完全平整。即便晶圓有最輕微的彎曲或扭曲,整個部分也將無法連接。

平整晶圓的工作通過一種名為化學機械平坦化(CMP)的工藝完成。它對芯片制造至關重要,特別是對于生產晶體管上方的互連層。

“對于混合鍵合,化學機械平坦化是我們必須控制的一項關鍵參數。”蘇里奧說。IEEE電子器件與技術大會上展示的結果表明,化學機械平坦化技術已提升到一個新水平,不僅能夠平整整個晶圓,還能夠減小銅焊片之間納米級的圓形絕緣層,確保更好的連接。

還有研究人員專注于確保這些平整的部件能夠牢固地粘在一起。他們嘗試使用不同的表面材料,如用硅碳氮化物代替硅氧化物,并采用不同的方案來對表面進行化學激活。最初,晶圓或裸芯片被擠壓在一起時,它們是通過相對較弱的氫鍵對接在一起的,人們擔心在后續工藝中它們無法保持原位。對接之后,晶圓和芯片會被慢慢加熱,在退火工藝中形成更強的化學鍵。這些鍵的強度如何(以及如何確定這一點)是IEEE電子器件與技術大會上展示的主要研究內容。

最終的鍵合強度有一部分來自銅連接。退火步驟使銅在間隙中膨脹,形成導電橋。三星的韓勝浩解釋說,控制這個間隙的大小是關鍵。如果膨脹過少,銅將無法熔化形成連接;而如果膨脹過多,晶圓將被推開。這是納米級的問題。韓勝浩報告了一種新的化學工藝研究,即每次蝕刻去除單一原子層的銅,他希望通過這種工藝實現精確控制。

連接的質量也很重要。芯片互連中的金屬不是單晶體,而是由許多顆粒組成的,顆粒朝向不同方向。即使銅膨脹后,金屬的顆粒邊界通常也不會從一側跨越到另一側。這種跨越應該會降低連接的電阻并提高其可靠性。日本東北大學的研究人員報告了一種新的冶金方案,最終可以生成跨越邊界的大型單銅顆粒。“這是一次重大變化。”日本東北大學副教授福島磯村說,“我們現在正在分析其背后的原因。”

IEEE電子器件與技術大會上討論的其他實驗側重如何簡化鍵合工藝。有幾項實驗試圖降低形成鍵合所需的退火溫度(通常在300℃左右),將長時間加熱對芯片造成的損害風險降到最小。應用材料公司的研究人員介紹了一種大幅縮短退火時間(從幾個小時縮短到5分鐘)的方法以及在這方面取得的進展。

表現出色的CoW

目前,CoW混合鍵合對新型中央處理器和圖形處理器制造商更加有用:芯片制造商可通過這項技術堆疊不同尺寸的芯片,并在芯片相互鍵合之前對每塊芯片進行測試,確保不會因為單個缺陷部件而毀掉整塊昂貴的中央處理器。

CoW面臨著WoW所面臨的全部困難,但可選擇的緩解辦法卻更少。例如,化學機械平坦化工藝用于平整晶圓,而不是單個裸芯片,一旦裸芯片從源晶圓中切割下來并測試,便沒有多少辦法可以改進其鍵合準備了。

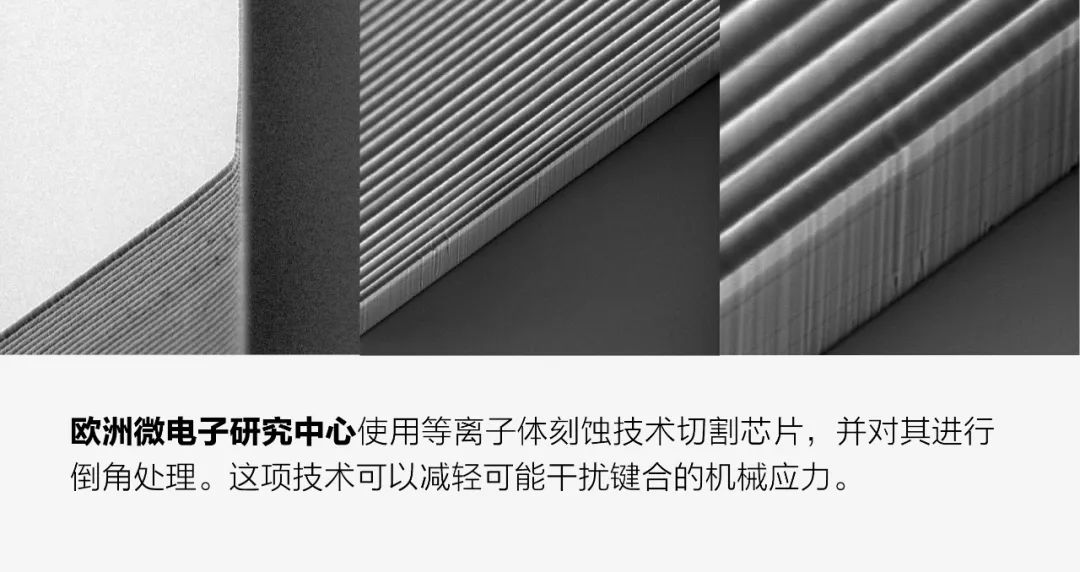

不過,英特爾的研究人員報告了具有3微米間距的CoW混合鍵合,同時,如上文提到的,歐洲微電子研究中心團隊實現了2微米間距,實現方式為:在中間過程仍將裸芯片附著在晶圓上,使其變得非常平整,同時在整個過程中保持裸芯片的清潔。兩個團隊都使用了等離子體蝕刻技術來切割裸芯片,而不是常用的專用刀片。等離子體蝕刻不會像刀片那樣導致邊緣碎裂,碎裂產生的碎片可能會干擾連接。歐洲微電子研究中心團隊還可通過這項技術改變裸芯片的形狀,制作倒角,減輕可能破壞連接的機械應力。

多位參加IEEE電子器件與技術大會的研究人員認為,CoW混合鍵合對未來的高帶寬內存(HBM)至關重要。高帶寬內存由多塊動態隨機存取存儲器(DRAM)裸芯片堆疊而成,目前有8到12層高,置于一塊控制邏輯芯片之上。它通常與高端圖形處理器放在同一封裝內,對于處理ChatGPT等大語言模型所需的海量數據至關重要。今天的高帶寬內存裸芯片堆疊采用的是微凸塊技術,兩層之間有被有機填料包裹的小焊球。

隨著人工智能進一步提高內存需求,動態隨機存取存儲器制造商希望在高帶寬內存芯片中堆疊20層,甚至是更多層。微凸塊的體積會占用空間,這意味著這些堆疊很快將因太高而無法與圖形處理器一起封裝。在這方面,混合鍵合可以降低高帶寬內存的高度,同時比較容易減少封裝中的余熱,因為層與層之間的熱阻會減少。

在IEEE電子器件與技術大會上,三星工程師展示了混合鍵合可以實現的16層堆疊的高帶寬內存。三星高級工程師李賢民表示:“我認為使用這項技術可以實現超過20層的堆疊。”其他CoW新技術也可以幫助將混合鍵合應用于高帶寬內存。蘇里奧說,CEA Leti的研究人員正在探索自對齊技術。這將助于確保僅通過化學工藝實現良好的CoW連接。每個表面的一部分被制成疏水性,另一部分為親水性,從而使表面自動滑入到位。

在IEEE電子器件與技術大會上,來自日本東北大學和雅馬哈機器人公司的研究人員報告了類似的方案,在動態隨機存取存儲器實驗芯片上,利用水的表面張力對齊的5微米焊片實現了優于50納米的精度。

混合鍵合的邊界

研究人員幾乎肯定會繼續縮小混合鍵合連接的間距。臺灣積體電路制造公司(以下簡稱臺積電)的開拓系統項目經理賈漢中(Han?Jong Chia,音)在IEEE電子器件與技術大會上表示,200納米的WoW間距不僅是可能的,而且是可取的。臺積電計劃在兩年內引入一種名為“背面供電”的技術。(英特爾計劃在2024年底引入)。這項技術將芯片粗大的電源傳輸互連放置在硅表面下方,而不是上方。臺積電研究人員通過計算得出,沒有了這些電源管道,最上層可以更好地連接較小的混合鍵合焊片。采用200納米鍵合焊片的背面供電裝置將大幅降低3D連接的電容,通過測量,其能效和信號速度將達到使用400納米鍵合焊片時的8倍。

賈漢中表示,如果鍵合間距進一步縮小,未來可能會實現跨越兩片晶圓的“折疊”電路塊。這樣,當電路塊內的一些長連接就可以走垂直捷徑,有助于提高計算速度并降低功耗。

混合鍵合可能不僅限于硅。CEA Leti的蘇里奧表示:“當下,我們在‘硅對硅晶圓’上取得了很大發展,不過我們也在探索氮化鎵和硅晶圓以及玻璃晶圓之間……以及所有材料之間的混合鍵合。”他所在的機構甚至介紹了用于量子計算芯片的混合鍵合研究,其中涉及對超導鈮而不是銅進行對齊和鍵合。

“很難說研究邊界在哪里,一切都在飛快發展。”蘇里奧說。

-

芯片

+關注

關注

463文章

54163瀏覽量

467777 -

3D

+關注

關注

9文章

3016瀏覽量

115367 -

摩爾定律

+關注

關注

4文章

640瀏覽量

81073

原文標題:銅連接 — 混合鍵合也許能拯救摩爾定律

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

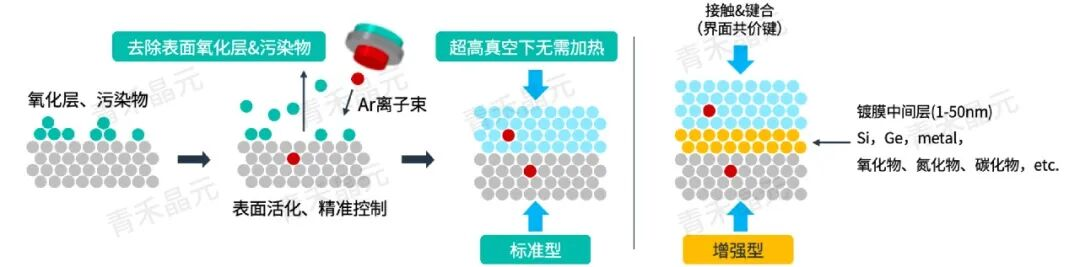

青禾晶元常溫鍵合方案,破解第三代半導體異質集成熱損傷難題

詳解先進封裝中的混合鍵合技術

芯片制造中的鍵合技術詳解

3D集成賽道加速!混合鍵合技術開啟晶體管萬億時代

晶心科技:摩爾定律放緩,RISC-V在高性能計算的重要性突顯

LG電子重兵布局混合鍵合設備研發,鎖定2028年大規模量產目標

從微米到納米,銅-銅混合鍵合重塑3D封裝技術格局

混合鍵合市場空間巨大,這些設備有機會迎來爆發

電力電子中的“摩爾定律”(1)

混合鍵合中的銅連接:或成摩爾定律救星

混合鍵合中的銅連接:或成摩爾定律救星

評論