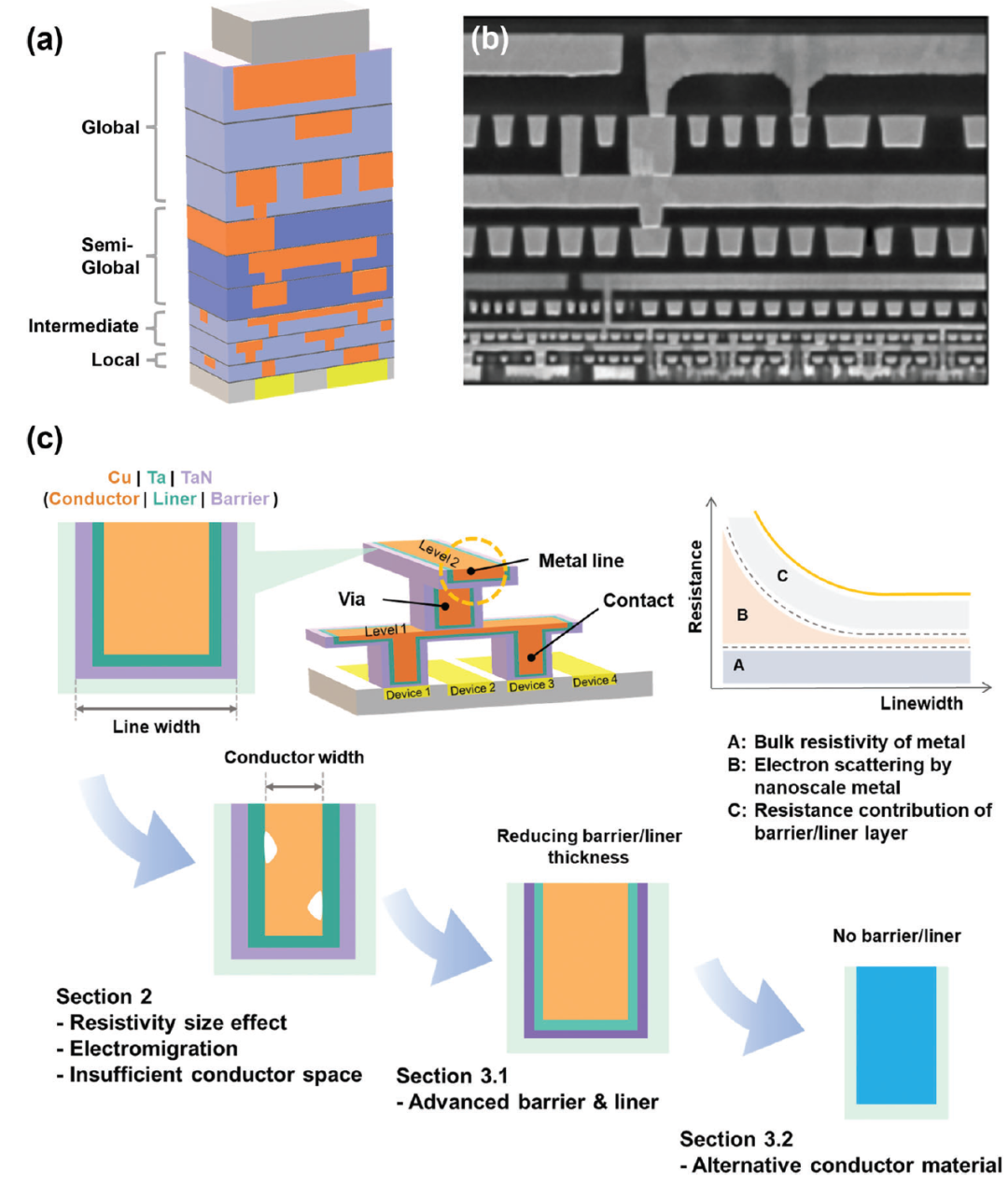

隨著集成電路的集成度越來越高,器件尺寸變得越來越小,金屬互連設計也緊跟這個趨勢,布線的密度增加了,更長的互連線會導致了更高的電阻。與此同時,互連體積的減少會引起電容耦合和串擾的幾率顯著增加。當互連尺寸很小時,RC 延遲的大小深刻影響著芯片的性能(R代表了互連線電阻,C代表了介質層分隔的金屬連線之間的寄生電容)。該延遲即時間,它應該足夠的小且能夠準確地傳遞信號。

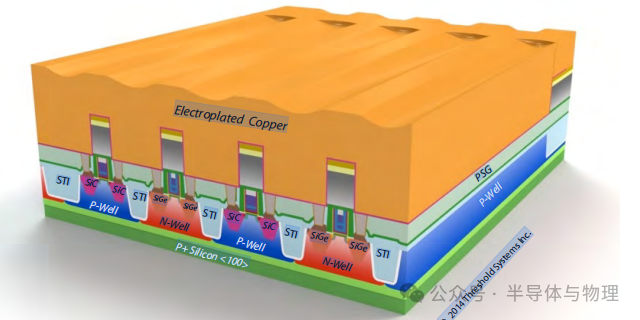

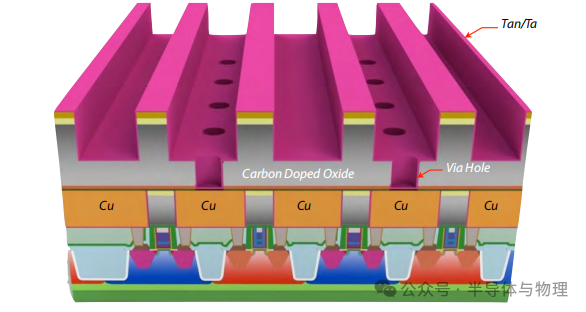

Liner:襯墊層,有助于金屬粘合;Barrier:阻擋層,阻止金屬擴散至介質層

有效減小RC延遲的方法之一是用銅互連代替過去的鋁互連;另一種方法是在互連線之間插入介電常數更低(Low-k)的材料,有效降低寄生電容和串擾。本文這里就不詳細展開了,讀者可以參閱《低介電常數材料的發展歷程簡介》

一、銅互連面臨的問題

目前銅互連已經發展成為主流工藝,并日益完善。然而銅互連也面臨一些問題。隨著線寬(Line Width)的縮小,采用銅作為互連材料的可靠性問題日益突出。列舉一個對比數據:工藝節點從45nm下降到22nm,RC延遲會增加7%,下降到10nm,RC延遲會增加22%,再下降到7nm,RC延遲會增加48%。

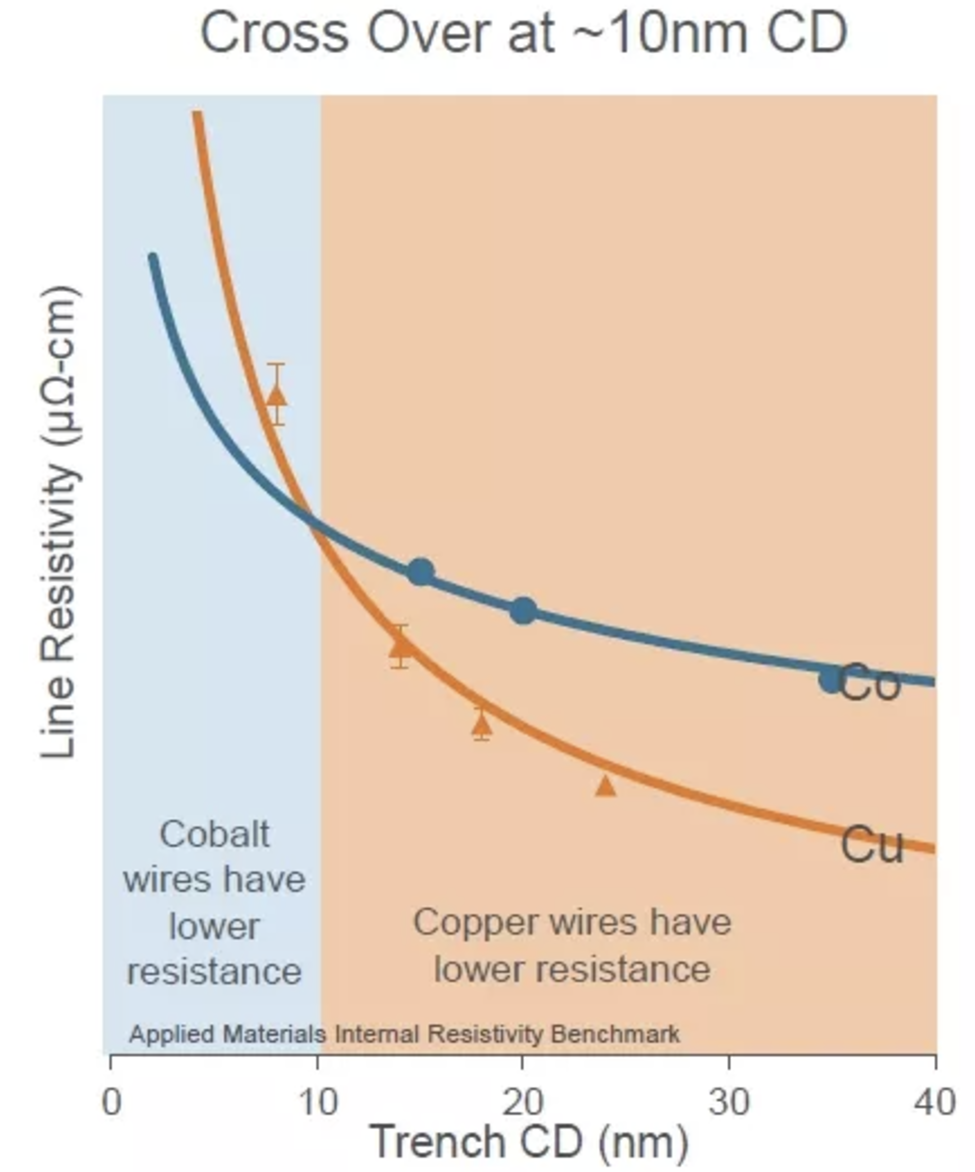

RC延遲增加的一個重要原因是,隨著線寬的縮小,互連線的電阻率在急劇增加,限制器件的性能并阻礙縮放。在宏觀尺度下,銅的體電阻率往往是影響線電阻率的主要因素,然而隨著線寬減小至銅的平均電子自由程(40nm)以下,表面和晶界的電子散射急劇增強,這種會導致線電阻率的急劇增加,并最終造成RC延遲升高。例如,當線寬從20nm下降到10nm時,線電阻率從約1.8μΩ/cm增加到約20μΩ/cm。這種在納米尺度上發生的載流子增強散射現象,被稱為尺寸效應(Size Effect)。

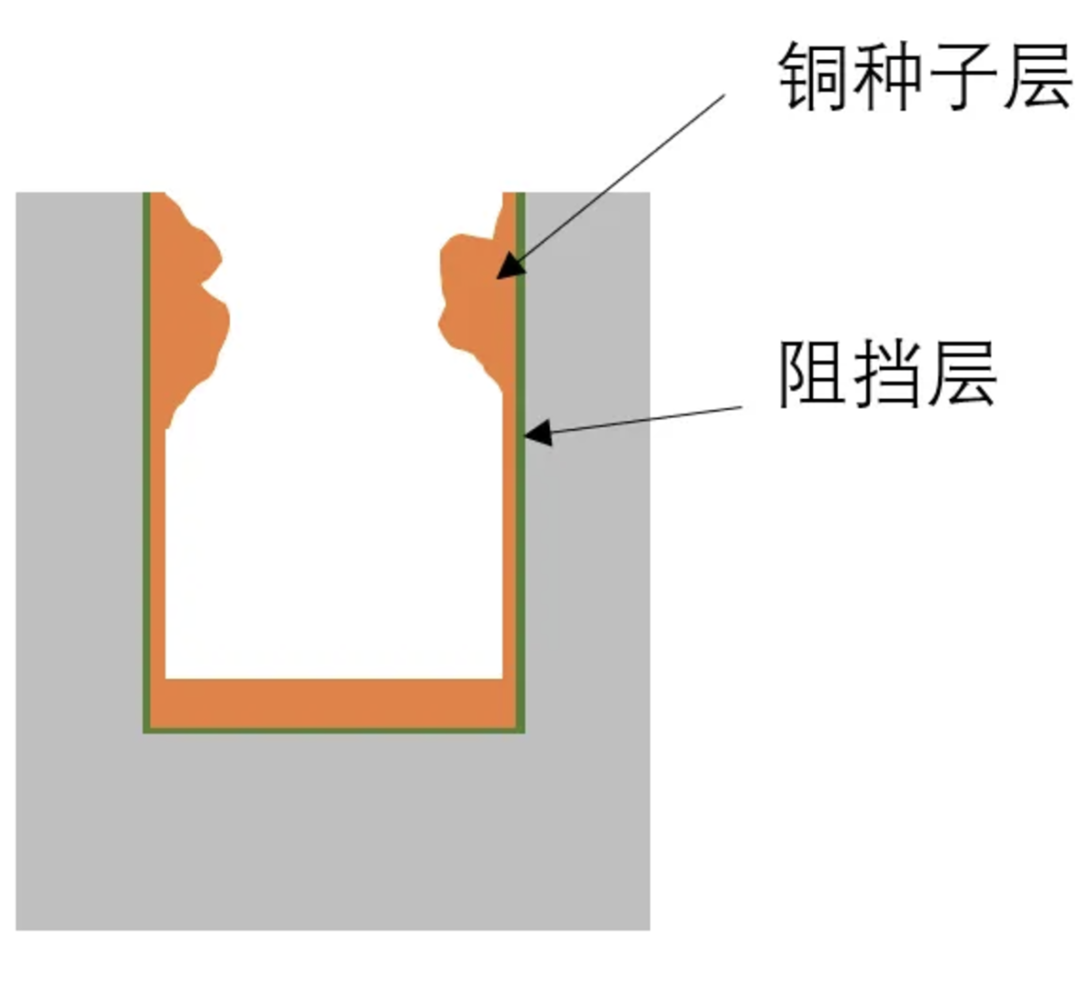

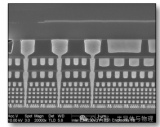

線寬的縮小除了導致線電阻率的增加,還伴隨著電流密度和器件工作溫度的升高,所產生的電遷移(EM)或應力空洞將嚴重損害互連材料的可靠性。如上圖,阻擋層、種子層以及電鍍工藝可能無法完美的契合,導致金屬淀積時很容易出現空洞等缺陷。在制作種子層時,通常會在溝槽或通孔的頂部產生懸垂,甚至溝槽頂部會存在開口不足的情況。此外,一些添加劑很容易在溝槽的開口處附著并堵塞,導致銅淀積不完整,形成空洞等缺陷。

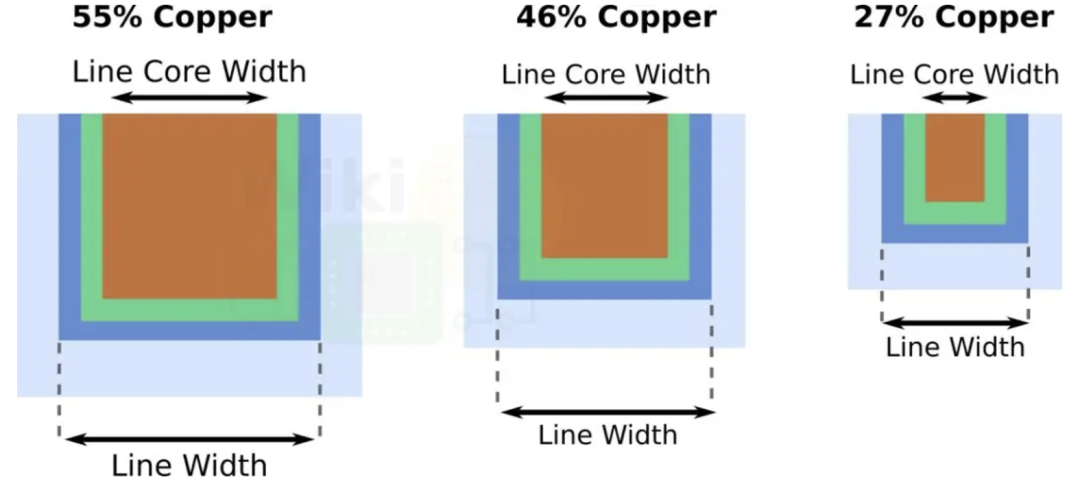

在阻擋層(體電阻率較高)厚度固定的前提下,隨著線寬縮小,溝槽內銅的比例會越來越低,這樣就進一步縮小了銅互連線的截面積。換句話說,不斷縮小互連尺寸會顯著增加阻擋層的體積比,從而加速互連線電阻率的升高。

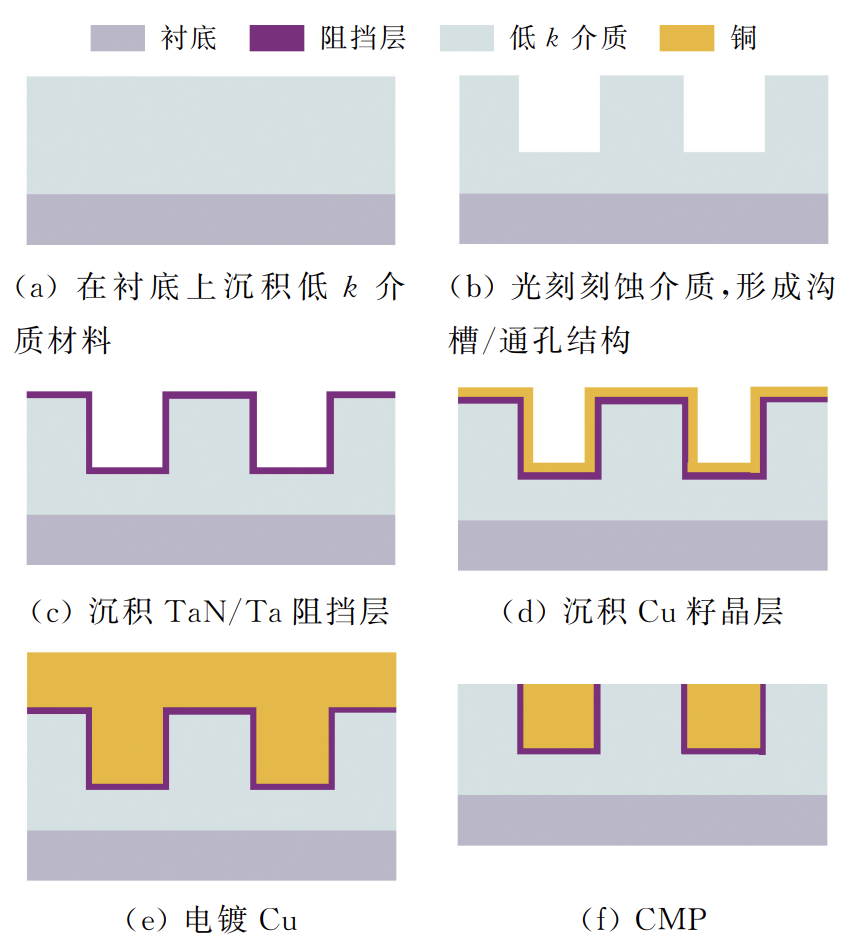

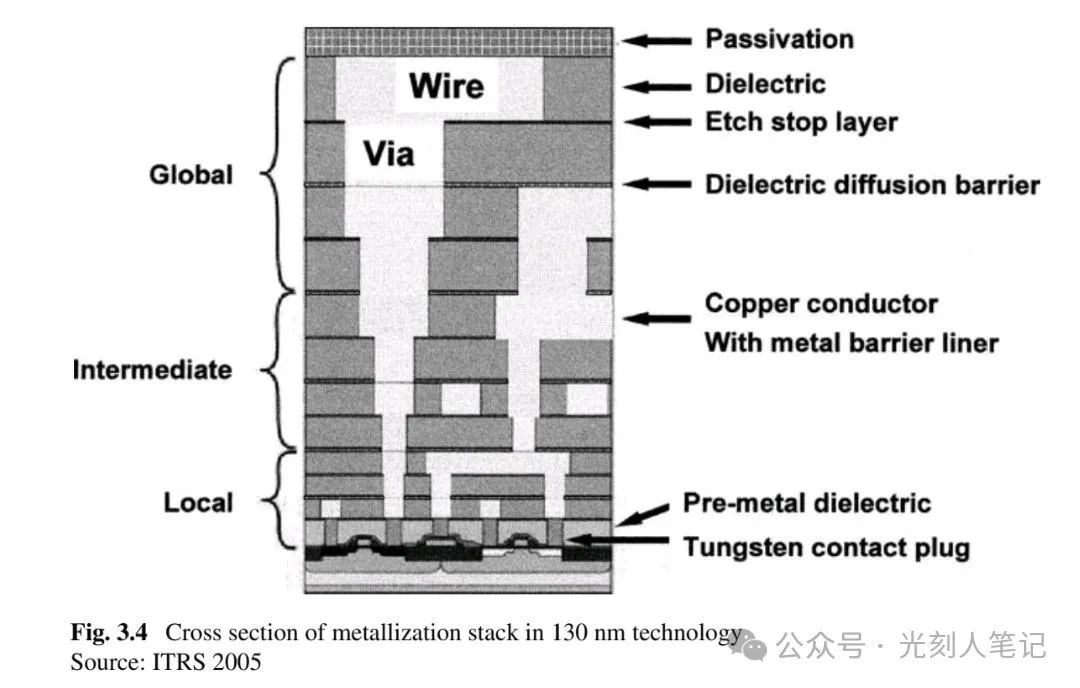

二、大馬士革鑲嵌工藝

由于銅不能產生揮發性的氯化物,很難用反應性離子刻蝕(RIE)的方法來制作互連線圖形,因此銅互連多采用大馬士革鑲嵌工藝(下圖)。在鑲嵌工藝中,先在低 k 介質層上刻蝕所需溝槽和通孔,然后沉積一層阻擋層,有時介質層也可充當阻擋層,再把銅淀積到這些溝槽或通孔中。最后用化學機械拋光的方法對互連線作整體平坦化,去掉多余物質。

大馬士革工藝通常有兩種:雙鑲嵌和單鑲嵌。所謂雙鑲嵌工藝是同時制備通孔及本層的工藝連線,而在單鑲嵌則是兩者被分別制備出來。由于雙鑲嵌比單鑲嵌工藝少大約30% 的工序,因此最為常用。銅淀積可以用化學氣相沉積(CVD)、濺射、電鍍等方法。由于濺射工藝的臺階覆蓋性差,CVD會有雜質在沉積過程中夾雜在薄膜里,且沉積速度慢,而電鍍的優勢在于設備成本低、工作溫度低、薄膜均勻、質量好,對通孔及溝槽的填充能力強。因此電鍍技術是銅淀積技術的主流。

三、阻擋層的發展歷程

阻擋層在增強金屬互連的機械完整性和電氣可靠性方面發揮著重要作用,可以防止金屬擴散并提供與周圍介質層之間牢固的附著。比如銅在低溫下會在硅和二氧化硅中迅速擴散,減少器件的少子壽命并造成pn結漏電流。當器件尺寸微縮時,阻擋層在保護器件免受金屬毒害方面起到關鍵作用。

好的阻擋層材料應該具有高熔點,因為擴散性與材料熔點直接相關。高熔點金屬(Cr、Ti、Nb、Mo、Ta 和 W)作為銅與硅之間的阻擋層被大量研究。從電阻率和使用二次離子質譜(SIMS)探測阻擋銅擴散這兩方面,證實在難熔金屬中 Ta和 W是性能較為優良的阻擋材料。

多晶薄膜有晶界的缺陷,并且晶界被認為是擴散的主要途徑,這限制了它們的應用。不過可以通過加入氮元素來填塞晶界,TaN和 WaN被證實是性能更為優秀的阻擋材料,如TaN阻擋層的熱穩定性達到了 650℃。三元非晶材料也是目前研究的熱點,在形成氮化過程中摻入硅形成三元非晶氮化物,如Ta36Si14N50由于晶界的消除其熱穩定性達到了 900℃。不過,這些二元和三元擴散阻擋層有太高的電阻率(100~1000μΩ/cm),而且穩定性也只是在厚度大于 10nm才有效。隨著線寬的縮小,阻擋層的厚度也只會越來越小,并且要求有接近于銅的低電阻率,這對阻擋層材料微結構的質量控制以及材料淀積工藝(如臺階覆蓋能力)提出了更高的要求。

在 14nm 以下的技術節點中,基于傳統PVD的Ta/TaN襯墊/阻擋層所能發揮作用變得愈發受限,究其主要原因:一是隨著線寬的縮小,體電阻率更高的Ta/TaN層占據了越來越高的布線橫截面,導致線電阻率增加;二是為了在14nm及以下技術節點中保持銅體積分數約在83%,必須將Ta/TaN襯墊/阻擋層薄化至小于3nm;三是使用PVD工藝難以制作小于3nm厚度下高度整體、連續和均勻的Ta/TaN層;四是在深槽內形成所需的具有連續、平滑和整合性的銅種子層(約2~3nm)與Ta/TaN阻擋層結合力很差。為了克服與金屬互連微縮相關的這些挑戰,研究人員發現選擇鈷(Co)作為銅的替代品極具吸引力,除了它具有較低的電阻率并在高深寬比孔內具有更好的整合覆蓋外,還可以直接在阻擋層上沉積而無需種子層,并且不會損傷襯底。相較于銅互連,鈷互連所需的阻擋層會更薄。這就是鈷互連的故事起源,本文就不過多展開了。

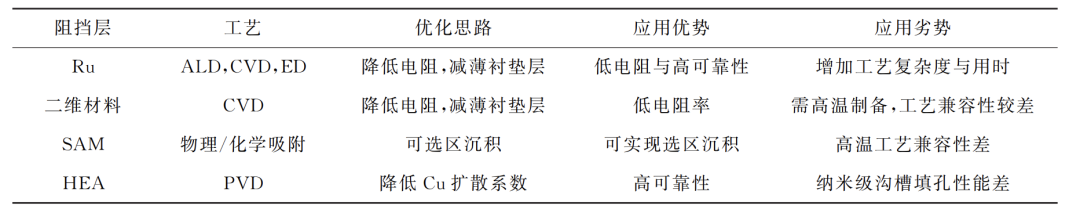

當然隨著先進工藝的發展,多種新型阻擋層候選材料及其工藝處在不同研發和驗證階段,其往往具有比傳統材料 TaN/Ta 更小的電阻率和更優秀的阻擋性能,但也面臨著材料體系優化、制備和工藝兼容性、技術成熟度等巨大挑戰。新一代阻擋層材料,包括如鉑族金屬基材料(PGM)、二維材料、自組裝單分子層(Self-Assembled Molecular Layers,SAM)和高熵合金(High-Entropy Alloy, HEA)等有望在不遠的將來得到技術應用。

-

集成電路

+關注

關注

5452文章

12571瀏覽量

374523 -

RC

+關注

關注

0文章

239瀏覽量

50776

原文標題:【推薦】一文了解金屬互連中阻擋層

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Salicide自對準硅化物工藝的定義和制造流程

高精度高可靠的Cr-Ni-Au電極NTC芯片

化學氣相淀積工藝的核心特性和系統分類

極細同軸線束在MIPI/USB3/HDMI高速互連中的應用與挑戰

TSV制造技術里的通孔刻蝕與絕緣層

為什么LED芯片正電極要插入二氧化硅電流阻擋層,而負極沒有?

CMOS第一層互聯的結構與作用

互連層RC延遲的降低方法

詳解原子層沉積薄膜制備技術

半導體芯片中的互連層次

一文了解金屬互連中阻擋層

一文了解金屬互連中阻擋層

評論