原創:Xoitec 異質集成XOI技術

來源:上海微系統所,集成電路材料實驗室,異質集成XOI課題組

1工作簡介

超寬禁帶氧化鎵是實現超高壓、大功率、低損耗器件的核心電子材料,滿足新能源汽車、光伏風電等功率模組應用需求。然而氧化鎵熱導率極低,限制了氧化鎵高功率器件的發展。近日,中國科學院上海微系統與信息技術研究所(以下簡稱為上海微系統所)異質集成XOI課題組與哈爾濱工業大學孫華銳教授課題組通過“萬能離子刀”剝離轉移技術制備了高質量的碳化硅基氧化鎵薄膜,并結合底部封裝技術實現了具有極低器件熱阻的氧化鎵MOSFETs。相關研究成果以“Extremely Low Thermal Resistance of β?Ga2O3 MOSFETs by Cointegrated Design of Substrate Engineering and Device Packaging”為題發表在Top期刊ACS Applied Materials & Interfaces上。論文共同第一作者分別為上海微系統所的博士生瞿振宇、趙天成與哈爾濱工業大學的博士生謝銀飛。論文通訊作者為上海微系統所的徐文慧助理研究員、歐欣研究員與哈爾濱工業大學的孫華銳教授。

2研究背景

氧化鎵作為第四代超寬禁帶半導體的代表,具有禁帶寬度寬,巴利加優值高,大尺寸晶圓可批量制備等特點,在制備高性能功率器件方面潛力無限[1]。然而,氧化鎵本身的熱導率十分低,僅相當于4H-SiC的約1/10,這使得基于氧化鎵的MOSFET在高功率下將產生嚴重的自熱效應。通過與高導熱襯底進行異質集成已被證實是解決氧化鎵散熱問題的有效手段[2]。在各種襯底集成方式中,離子束剝離技術不但可以大幅提升異質集成氧化鎵材料的散熱性能,還具有批量制備的潛力。然而,與碳化硅基氮化鎵HEMT相比[3],目前報道的碳化硅基氧化鎵MOSFET的器件熱阻仍然相對較高[4]。因此,有效的氧化鎵MOSFET熱管理策略仍然亟需開發。

上海微系統所異質集成XOI課題組與哈爾濱工業大學通過襯底集成與器件封裝的協同設計,成功實現器件熱阻低至4.45 K·mm/W的碳化硅基氧化鎵MOSFET制備,并通過三維拉曼圖譜與COMSOL仿真相結合實現對MOSFET器件內部溫度的三維可視化,為氧化鎵大功率器件熱管理研究提供了有效的技術方案。

3研究亮點

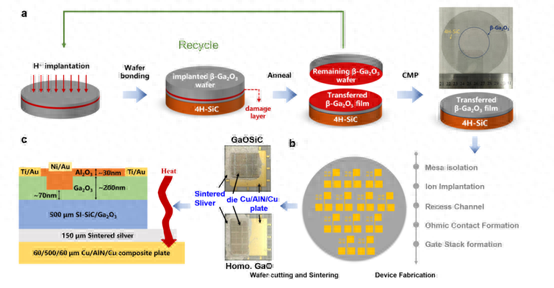

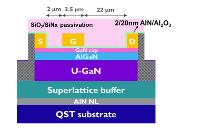

通過離子束剝離技術與底部封裝技術制備碳化硅基氧化鎵晶圓的流程如圖1(a)所示,先通過H離子注入使氧化鎵中形成缺陷層,再將注入后的氧化鎵晶圓與4H-SiC晶圓進行鍵合形成異質晶圓。在后續退火過程中氧化鎵晶圓會沿著缺陷層斷裂,從而得到異質集成的碳化硅基氧化鎵薄膜。對該薄膜進行拋光后按照圖1(b)的流程進行MOSFET的制備,所得器件標記為GaOSiC MOSFET。以同樣的流程在商業的同質外延氧化鎵片上進行MOSFET的制備,稱為Homo. GaO MOSFET。在完成MOSFET的制備后,通過用銀漿的燒結使裸片固定在Cu/AlN/Cu基板上,完成器件的底部封裝,其流程與最終的器件結構如圖1(c)所示。

圖1 (a)異質集成GaOSiC晶圓的制備流程;(b) Homo. GaO MOSFET和GaOSiC MOSFET的制備流程;(c)銀漿燒結過程與器件結構示意圖。

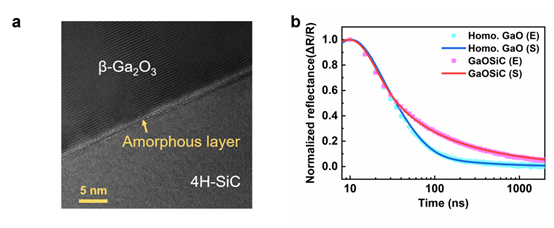

圖2(a)展示了通過離子束剝離制備得到的GaOSiC異質界面,通過對等離子激活程序進行優化,其界面非晶層密度得到很好的控制,僅為~1 nm。良好的界面使得界面處的熱輸運變得更加有效,圖2(b)展示了利用TTR表征的GaOSiC與Homo. GaO晶片的熱輸運性質,提取得到GaOSiC晶片中氧化鎵層熱導率為6.5 ± 0.6 W/m·K,相比于Homo. GaO晶片中的11.6 ± 0.2 W/m·K略有下降,這主要是由異質集成氧化鎵薄膜中聲子與界面散射所致。由于界面處極薄的非晶層厚度,Ga2O3/4H-SiC界面熱阻低至6.67 ± 2 m2·K/GW,是目前已報道的最低值。

圖2 (a)Ga2O3/4HSiC界面的HRTEM圖像;(b)GaOSiC與Homo. GaO晶片300 K時的歸一化瞬態熱反射曲線。

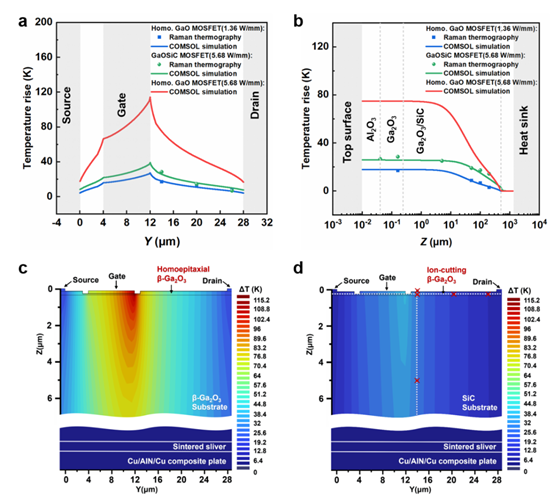

為了對氧化鎵功率器件進行有效熱管理,利用三維拉曼測試與COMSOL仿真相結合實現對GaO器件內部溫度可視化分析。通過更改激光聚焦位置與深度測得器件中不同位置的拉曼圖譜,并通過拉曼峰位置的偏移提取出該點的溫度,并對COMSOL仿真結果進行校準可實現工作狀態下器件中的3D溫度分布。圖3(a)和(b)分別展示了通過器件表面的橫向溫度分布與柵極靠漏極側邊緣的縱向溫升分布,在相同功率下,Homo. GaO MOSFET中的溫升顯著高于GaOSiC MOSFET,并且熱量集中在表面的柵極靠漏極側邊緣。圖3(c)和(d)則展示了同為5.68 W/mm的功率密度下COMSOL仿真所得的Homo. GaO MOSFET和GaOSiC MOSFET的溫升分布,可以明顯看出相較于Homo. GaO MOSFET,GaOSiC MOSFET中的溫度更低且分布更加均勻。

圖3 Homo. GaO MOSFET和GaOSiC MOSFET的(a)橫向(b)縱向溫升分布;仿真得到的功率為5.68 W/mm下(c)Homo. GaO MOSFFET和(d)GaOSiC MOSFET的三維溫升分布(交叉位置為拉曼測量位置)。

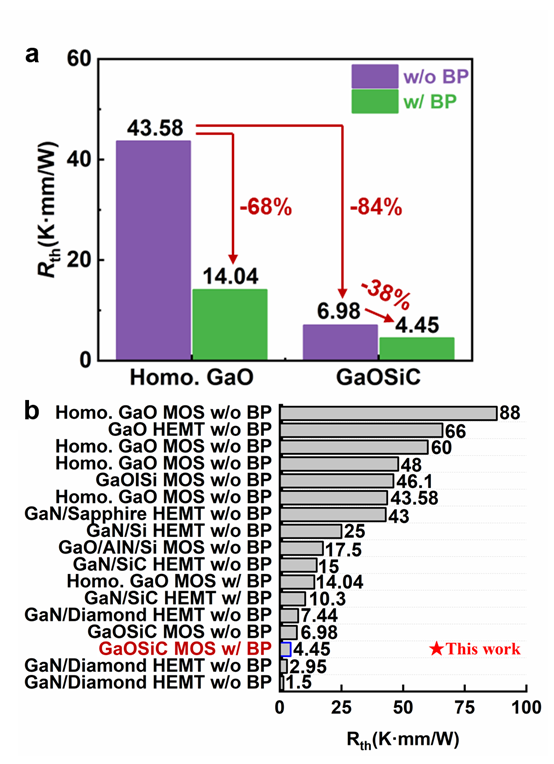

圖4(a)中對比了封裝前后的GaOSiC和Homo. GaO MOSFET的器件熱阻,將底部的Ga2O3襯底更換為高導熱的4H-SiC襯底后,其器件熱阻降低了84%,在結合底部封裝后,其熱阻更進一步降低到了封裝前Homo. GaO MOSFET的約1/10,僅為4.45 K mm/W。如圖4(b)所示,該結果與金剛石基GaN HEMT相當,為目前氧化鎵MOSFET的最低值,證實了襯底集成與器件封裝的協同設計對于提升器件散熱性能的有效性。

圖4 (a)封裝前后的Homo. GaO MOSFET和GaOSiC MOSFET熱阻對比;(b) 本工作的氧化鎵MOSFET與已報道的氧化鎵MOSFET和氮化鎵HEMT器件熱阻對比。

4總結與展望

本工作中,我們通過襯底集成和器件封裝的協同設計,成功地開發了一種用于氧化鎵器件的熱管理策略。通過工藝優化,實現了非晶層厚度僅為~1 nm的高質量GaOSiC異質界面,其界面熱阻僅為6.67 ± 2 m2·K/GW。利用三維拉曼測試與COMSOL仿真相結合實現對實際工作條件下氧化鎵器件內部溫度的可視化分析,發現Homo. GaO MOSFET中的溫度更高且集中,GaOSiC MOSFET的溫度更低且更均勻。結果表明,底部封裝的GaOSiC MOSFET的器件熱阻可顯著降低到未封裝的Homo. GaO MOSFET的約10%。該工作為大功率和射頻氧化鎵器件的熱管理提供創新的解決方案。

5原文傳遞

文章鏈接:

https://doi.org/10.1021/acsami.4c08074

6參考文獻

[1] Pearton, S. J.; Yang, J.; Cary, P. H.; Ren, F.; Kim, J.; Tadjer, M. J.; Mastro, M. A. A Review of Ga2O3 Materials, Processing, and Devices. Appl. Phys. Rev. 2018, 5, 011301.[2] Xu, W.; You, T.; Wang, Y.; Shen, Z.; Liu, K.; Zhang, L.; Sun, H.; Qian, R.; An, Z.; Mu, F.; Suga, T.; Han, G.; Ou, X.; Hao, Y.; Wang, X. Efficient Thermal Dissipation in Wafer-scale Heterogeneous Integration of Single-crystalline β-Ga2O3 Thin Film on SiC. Fundamental Res. 2021, 1, 691?696.[3] Pomeroy, J. W.; Bernardoni, M.; Dumka, D. C.; Fanning, D. M.; Kuball, M. Low Thermal Resistance GaN-on-diamond Transistors Characterized by Three-dimensional Raman Thermography Mapping. Appl. Phys. Lett. 2014, 104, 083513.[4] Song, Y.; Bhattacharyya, A.; Karim, A.; Shoemaker, D.; Huang, H. L.; Roy, S.; McGray, C.; Leach, J. H.; Hwang, J.; Krishnamoorthy, S.; Choi, S. Ultra-wide Band Gap Ga2O3-on-SiC MOSFETs. ACS Appl. Mater. Interfaces 2023, 15, 7137?7147.

【近期會議】

11月28-29日,“第二屆半導體先進封測產業技術創新大會”將再次與各位相見于廈門,秉承“延續去年,創新今年”的思想,仍將由云天半導體與廈門大學聯合主辦,雅時國際商訊承辦,邀您齊聚廈門·海滄融信華邑酒店共探行業發展!誠邀您報名參會:https://w.lwc.cn/s/n6FFne

聲明:本網站部分文章轉載自網絡,轉發僅為更大范圍傳播。 轉載文章版權歸原作者所有,如有異議,請聯系我們修改或刪除。聯系郵箱:viviz@actintl.com.hk, 電話:0755-25988573

審核編輯 黃宇

-

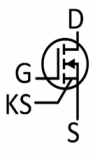

MOSFET

+關注

關注

151文章

9674瀏覽量

233544 -

封裝

+關注

關注

128文章

9249瀏覽量

148628 -

氧化鎵

+關注

關注

5文章

88瀏覽量

10876

發布評論請先 登錄

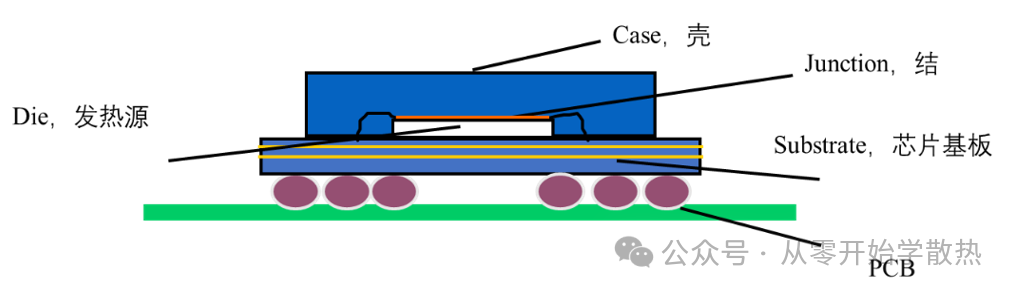

功率器件熱設計基礎(三)—— 結溫計算完整流程與工程實用方法

浮思特 | 在工程襯底上的GaN功率器件實現更高的電壓路徑

氧化鎵器件的研究現狀和應用前景

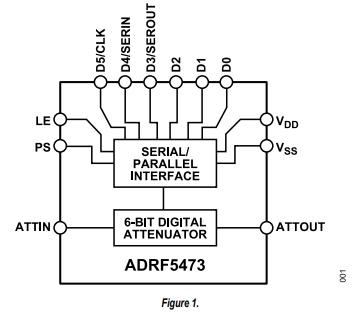

ADRF5473硅數字衰減器,0.5dB LSB,6位,100MHz至40GHz技術手冊

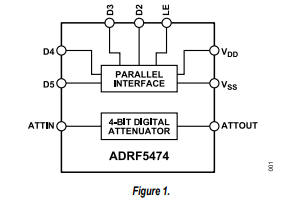

ADRF5474硅數字衰減器,2dB LSB,4位,10MHz至60GHz技術手冊

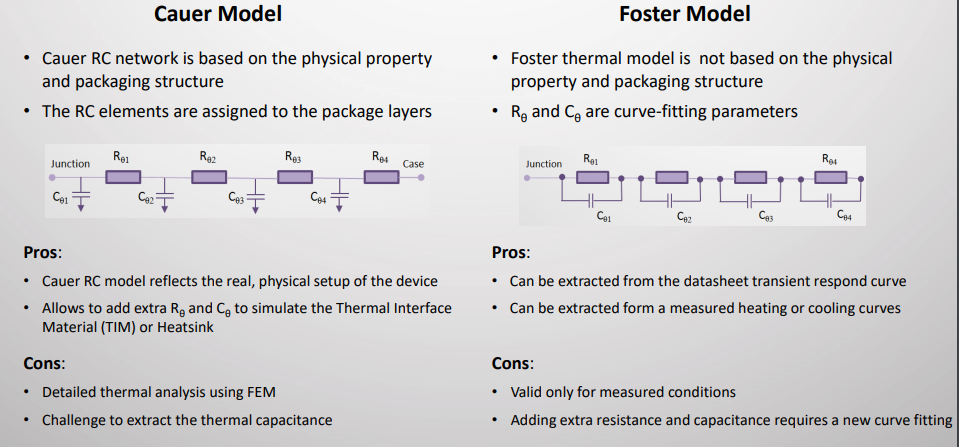

基于RC熱阻SPICE模型的GaNPX?和PDFN封裝的熱特性建模

ACS AMI:通過襯底集成和器件封裝協同設計實現具有極低器件熱阻的氧化鎵MOSFETs

ACS AMI:通過襯底集成和器件封裝協同設計實現具有極低器件熱阻的氧化鎵MOSFETs

評論