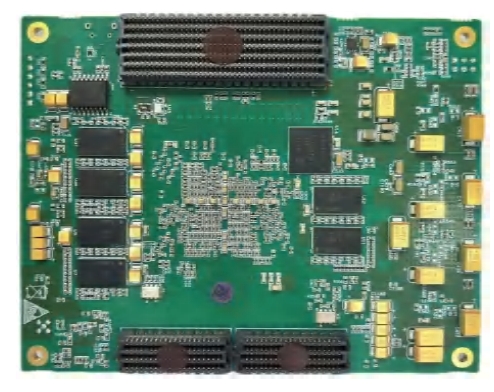

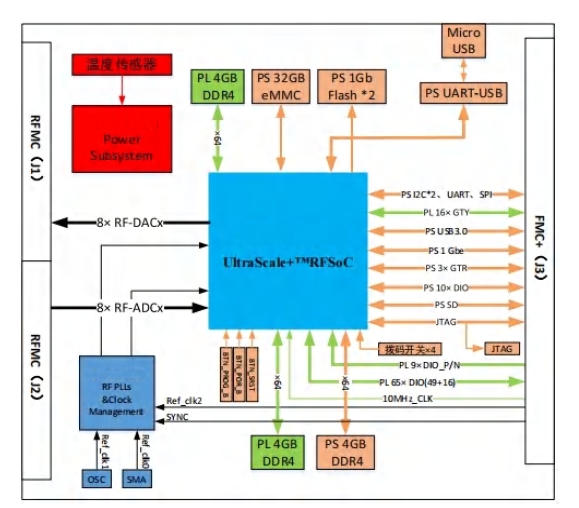

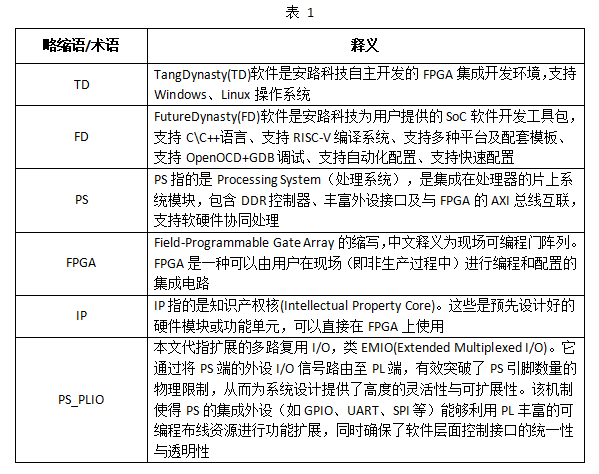

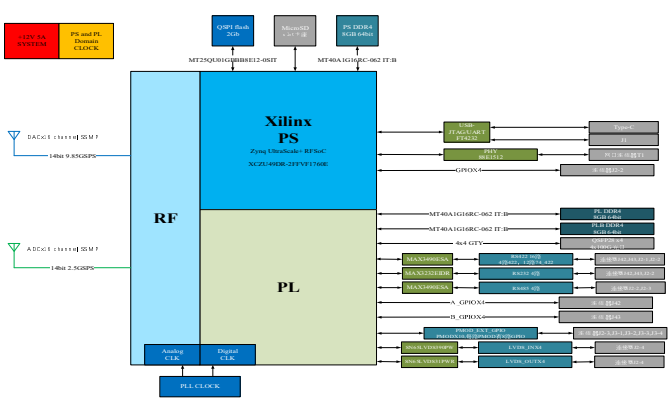

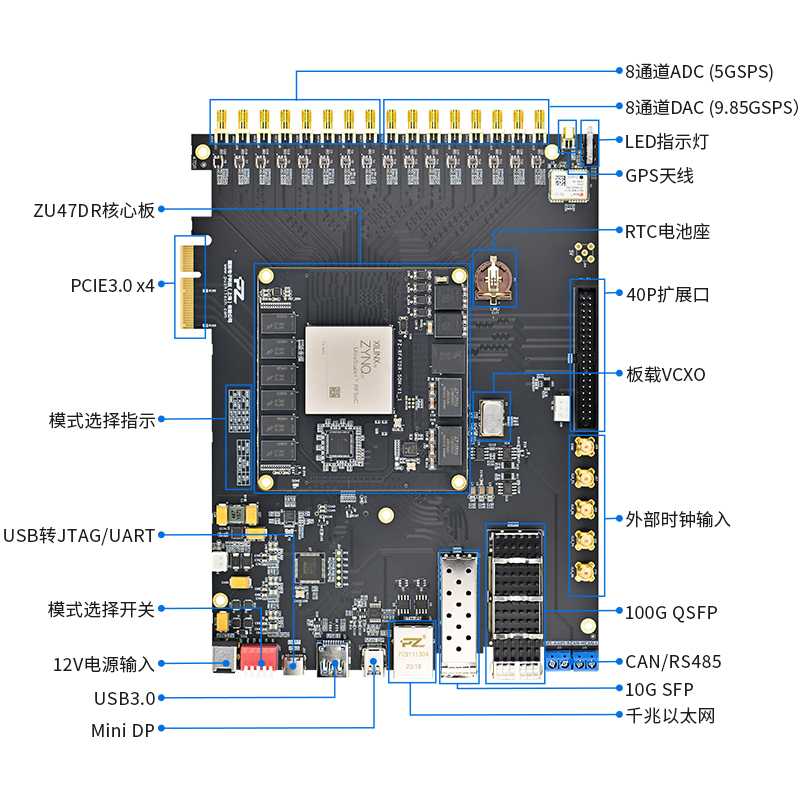

采用FDW復(fù)旦微電子FMZQ28DR- RFSoC處理器,兼容Gen1 ZU28/27、Gen3 ZU48/47DR RFSoC,擁有8個(gè)RF-ADC、8個(gè)RF-DAC通道。提供完整的應(yīng)用示例源代碼和性能分析工具, 主要用于小尺寸、低功耗、實(shí)時(shí)處理RF系統(tǒng)的快速集成與應(yīng)用部署,縮短產(chǎn)品開發(fā)周期。

主要技術(shù)指標(biāo):

? 核心處理器:Gen3 ZU48(47)DR- 2FSVG1517I RFSoC

? 8xADCs, 14-bit up to 5GSPS;

? 8x SD-FEC硬核(47無(wú)此硬核)8

? x DACs, 14-bit up to 9.85GSPS;

? RF Input Freq. Max:6GHz;

? Quad-core Arm Cortex-A53 MPCore with CoreSight;

? Dual-core Arm Cortex-R5F with CoreSight;

? PS I/O:支持UART,CAN2.0B,USB2.0,I2C,GigeE10/100/1000,SDIO,SPI 協(xié)議;

? 4x PS-GTR:支持PCIe Gen1/2、Serial ATA 3.1、DisplayPort 1.2a、USB 3.0 和 SGMII 協(xié)議;

? 16x PL-GTY:PCIe Gen4、100G Ethernet、150G Interlaken 等協(xié)議;

? 72x PL-GPIO:用戶自定義 IO;

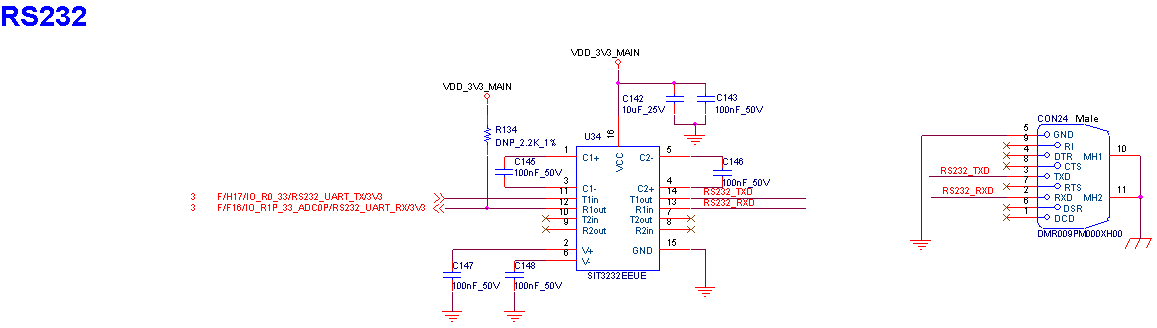

? 調(diào)試接口:JTAG、usb2UART、PMBus;

? 適配 Gen1 ZU28(27)DR RFSoC 芯片時(shí),變化參數(shù)如下:

? 8x ADCs, 12-bit up to 4.096GSPS

? 8x DACs, 14-bit up to 6.554GSPS

? RF Input Freq. Max:4GHz

? 8x SD-FEC 硬核(27無(wú)此硬核)

? 16x PL-GTY:支持PCIe Gen3、100G Ethernet、150G Interlaken 等協(xié)議

? 板載存儲(chǔ):

? 2 組 4GB 64bit DDR4 @ Programmable Logic

? 32GB eMMC Persistent Storage

? 4GB 64bit DDR4 @ Processor Subsystem

? 1Gb QSPI Boot Storage

? 獨(dú)立時(shí)鐘管理網(wǎng)絡(luò)

? 超低抖動(dòng)可編程時(shí)鐘網(wǎng)絡(luò):外部或板載參考 100MHz(可更換)可選;

? 支持板間時(shí)鐘同步;

? 33.33MHz@PS、200MHz@PL 獨(dú)立工作時(shí)鐘;

? 機(jī)械結(jié)構(gòu)與供電

? 12V 供電,過(guò)壓、過(guò)流、超溫監(jiān)測(cè)與管理;

? 機(jī)械尺寸:127.0mm * 101.6mm(老款),77.1mm*101.6mm(新款);

? 信號(hào)接口:2xRFMC,F(xiàn)MC+

? 配套明細(xì)

? 參考例程:ADC/DAC 例程;PL 例程;PS 例程;OS 鏡像;時(shí)鐘管理例程;

? RF Analyzer(ADC 性能評(píng)估軟件);

? PCIE 規(guī)范標(biāo)準(zhǔn)測(cè)試用底板(選配)

應(yīng)用領(lǐng)域

? 相控陣?yán)走_(dá)

? 5G大規(guī)模MIMO

? 混合波束成形

? 衛(wèi)星通信

? 空間信號(hào)檢測(cè)與干擾

? 多通道射頻儀表

? 寬域頻譜監(jiān)測(cè)與射電天文

審核編輯 黃宇

-

處理器

+關(guān)注

關(guān)注

68文章

20250瀏覽量

252206 -

核心板

+關(guān)注

關(guān)注

6文章

1397瀏覽量

32001 -

RFSoC

+關(guān)注

關(guān)注

0文章

45瀏覽量

3193

發(fā)布評(píng)論請(qǐng)先 登錄

DR1 系列核心板 PS+PL 異構(gòu)多核實(shí)戰(zhàn)案例手冊(cè)(二)

DR1 系列核心板 PS+PL 異構(gòu)多核實(shí)戰(zhàn)案例手冊(cè)(一)

DR1 評(píng)估板 PL 端 FPGA 開發(fā)完全指南:基礎(chǔ)案例與 ADC 采集模塊詳解(一)

探索 RTKA210030DR0000BU 演示板:高效電源解決方案

VU13P+47DR PCIE接口光纖處理板

安路DR1M90評(píng)估板:從基礎(chǔ)外設(shè)到通信模塊測(cè)試指南

數(shù)字陣列板卡設(shè)計(jì)原理圖:889-基于RFSOC XCZU49DR的 16T16R的軟件無(wú)線電硬件

【VPX361】青翼凌云科技基于3U VPX總線架構(gòu)的XCZU47DR射頻收發(fā)子模塊

創(chuàng)龍科技DR1M90工業(yè)評(píng)估板的關(guān)鍵優(yōu)勢(shì)

璞致電子 UltraScale+ RFSoC 架構(gòu)下的軟件無(wú)線電旗艦開發(fā)平臺(tái)

PZSDR/璞致【PZ-ZU47DR-KFB】——RFSoC 架構(gòu)下的超寬帶軟件無(wú)線電開發(fā)平臺(tái)標(biāo)桿

XILINX XCZU67DR FPGA完整原理圖

NW2-05D05DR3 NW2-05D05DR3

NW1-24D15DR3 NW1-24D15DR3

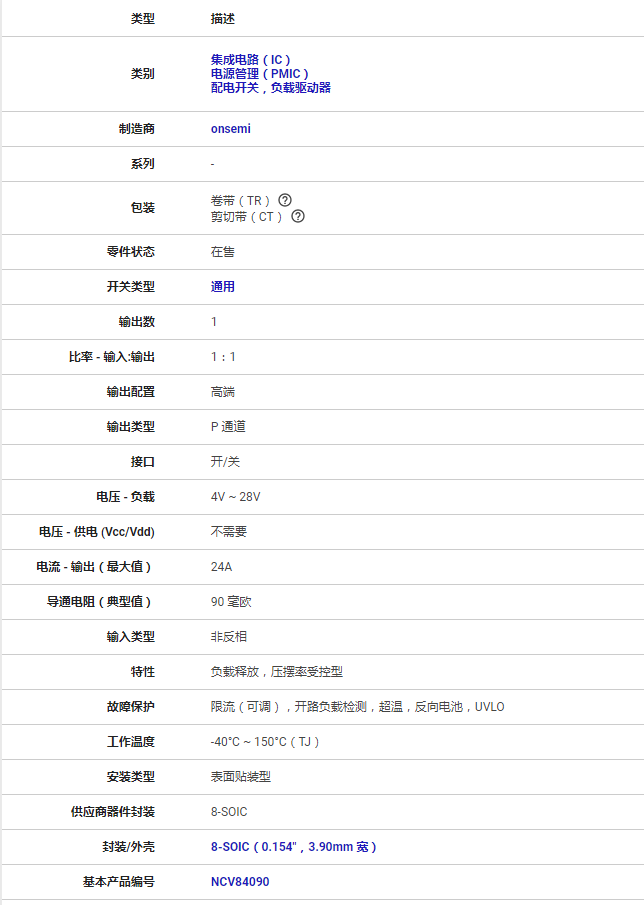

onsemi NCV84090DR2G為汽車和工業(yè)應(yīng)用設(shè)計(jì)的可靠負(fù)載開關(guān)驅(qū)動(dòng)器

國(guó)產(chǎn)RFSoC 47DR/28DR/27DR核心板

國(guó)產(chǎn)RFSoC 47DR/28DR/27DR核心板

評(píng)論