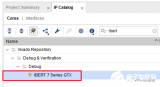

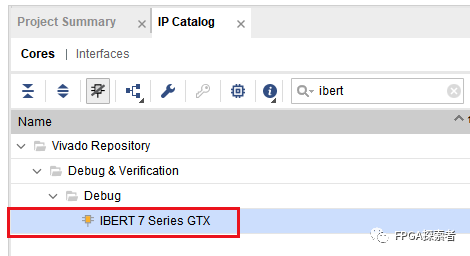

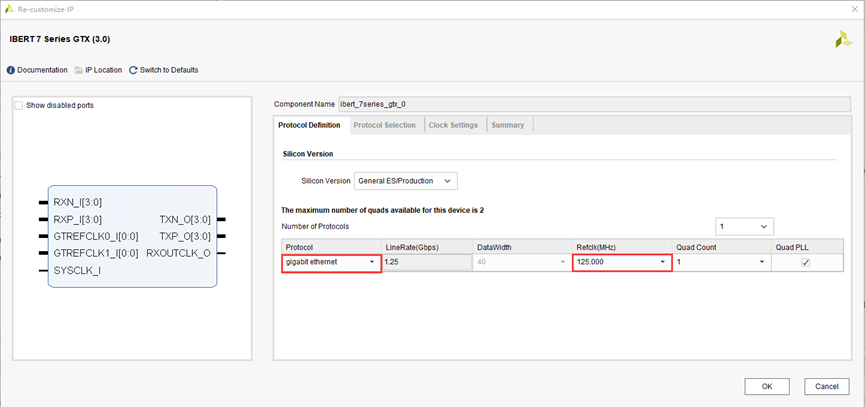

面向 UltraScale? 架構(gòu) GTY 收發(fā)器的可定制 LogiCORE? IP 集成式誤碼率測試器 (IBERT) 核用于評估和監(jiān)控 v 收發(fā)器。該核包括采用 FPGA 邏輯實現(xiàn)的模式生成器和檢查器,并能夠接入 GTY 收發(fā)器的端口和動態(tài)重配置端口屬性。還包括了通信邏輯,可通過 JTAG 在運行時間進(jìn)行設(shè)計訪問。此核可用作獨立或公開設(shè)計,基于客戶配置。

主要性能和優(yōu)勢:

為 Vivado? 串行 I/O 分析器功能與 IBERT 內(nèi)核之間提供了通信路徑。

提供 UltraScale 架構(gòu) GTY 收發(fā)器 (用戶可選數(shù)量)

可根據(jù)所需的線速、參考時鐘速率、和參考時鐘源來定制每個收發(fā)器

需要可源自引腳或某個使能 GTY 收發(fā)器的系統(tǒng)時鐘

特色技術(shù)文檔

Vivado 發(fā)布說明

IP 性能和資源利用率數(shù)據(jù)

工具和器件支持

器件系列支持:

Virtex UltraScale

設(shè)計工具支持:

Vivado Design Suite

相關(guān)產(chǎn)品

ChipScope 集成控制器 (ICON)

ChipScope PRO 虛擬輸入/輸出 (VIO)

ChipScope 集成邏輯分析器 (ILA)

面向 Virtex-7 GTX 的 ChipScope Pro IBERT

面向 Virtex-6 GTH 的 ChipScope Pro (IBERT)

面向 Virtex-5 FPGA GTX 收發(fā)器的 ChipScope Pro IBERT

面向 Spartan-6 GTP 收發(fā)器的 ChipScope Pro IBERT

Spartan-6 FPGA 嵌入式套件

Virtex-6 FPGA 嵌入式套件

-

IP

+關(guān)注

關(guān)注

5文章

1862瀏覽量

155812 -

誤碼率測試器

+關(guān)注

關(guān)注

0文章

2瀏覽量

5553

發(fā)布評論請先 登錄

IBERT GT收發(fā)器誤碼率測試實例

是德科技全新多通道比特誤碼率測試儀

誤碼率測試儀的技術(shù)原理和應(yīng)用場景

Keysight M8030A 長期回收 比特誤碼率測試儀

基于FPGA的誤碼率測試儀的設(shè)計與實現(xiàn)

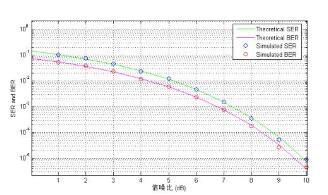

BER誤碼率 影響誤碼率的因素

誤碼率是指什么_誤碼率是怎么表示_怎么計算

信道編碼中的誤碼率曲線與編碼增益及編碼設(shè)計的誤碼率分析

關(guān)于ZC706評估板的IBERT誤碼率測試和眼圖掃描詳細(xì)分析

利用IBERT IP核實現(xiàn)GTX收發(fā)器硬件誤碼率測試實例

是德高性能比特誤碼率測試儀M8020A介紹

ZC706評估板IBERT誤碼率測試和眼圖掃描

誤碼率測試儀,讓工程師從容應(yīng)對高速數(shù)字信號設(shè)計

IP集成式誤碼率測試器(IBERT)的主要性能和優(yōu)勢介紹

IP集成式誤碼率測試器(IBERT)的主要性能和優(yōu)勢介紹

評論