電子發(fā)燒友網(wǎng)報(bào)道(文/黃晶晶)盡管當(dāng)前AI訓(xùn)練主要采用GPU+HBM的方案,不過一些新的技術(shù)仍然希望進(jìn)一步打破存儲數(shù)據(jù)傳輸帶來的瓶頸問題。最近,NEO半導(dǎo)體宣布開發(fā)其3D X-AI芯片技術(shù),旨在取代當(dāng)前高帶寬內(nèi)存(HBM)中的DRAM芯片,通過在3D DRAM中實(shí)現(xiàn)AI處理來解決數(shù)據(jù)總線問題。

通常來說,當(dāng)前的 AI芯片架構(gòu)將數(shù)據(jù)存儲在高帶寬內(nèi)存中,并通過數(shù)據(jù)總線將數(shù)據(jù)傳輸?shù)?GPU 以執(zhí)行 AI算法(數(shù)學(xué)計(jì)算)。這種架構(gòu)效率低下,數(shù)據(jù)總線會導(dǎo)致長時間延遲和高功耗。

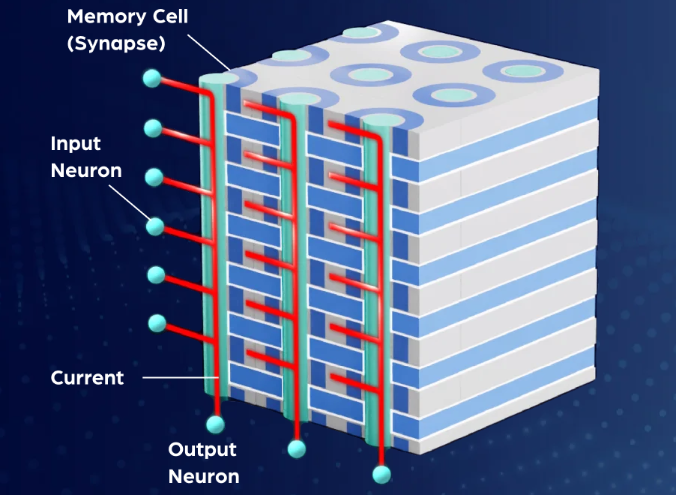

而3D X-AI使用存儲單元來模擬神經(jīng)網(wǎng)絡(luò)中的突觸。它支持在同一芯片中進(jìn)行數(shù)據(jù)存儲和人工智能操作。存儲在存儲單元中的數(shù)據(jù)直接用于生成神經(jīng)網(wǎng)絡(luò)的輸出,而不進(jìn)行任何數(shù)學(xué)計(jì)算,從而大大提高人工智能性能并顯著節(jié)省能源。

來源:NEO半導(dǎo)體官網(wǎng)

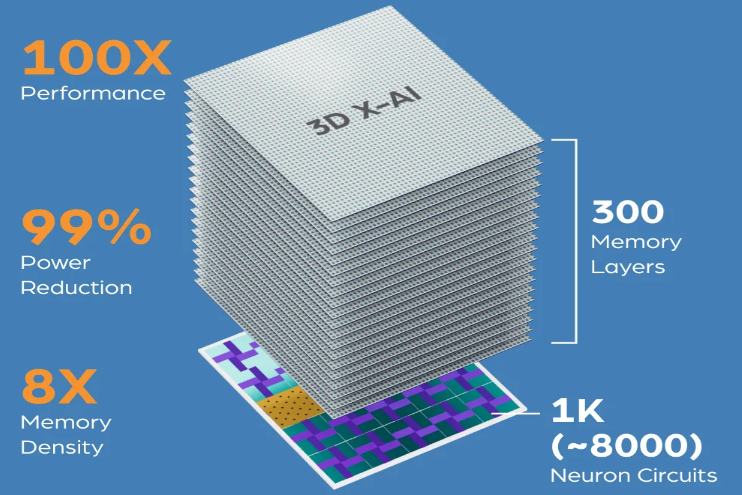

3D X-AI芯片是一種具有AI處理能力的3D DRAM在同一芯片中,它底部有一個神經(jīng)元電路層,頂部有300層存儲單元,容量為128 GB。這種創(chuàng)新的芯片可以將人工智能芯片的性能提高100倍,并將功耗降低99%。它具有8倍更高的密度,非常適合存儲大型語言模型(LLM),用于生成式人工智能應(yīng)用程序,如Chat GPT,Gemini和CoPilot。

來源:NEO半導(dǎo)體官網(wǎng)

NEO半導(dǎo)體介紹,采用NEO的3D X-AI技術(shù)的人工智能芯片可實(shí)現(xiàn),100X性能加速:包含8000個神經(jīng)元電路,可在3D內(nèi)存中執(zhí)行A1處理;99%功耗降低:將數(shù)據(jù)傳輸?shù)紾PU進(jìn)行計(jì)算的需求最小化,從而減少數(shù)據(jù)總線產(chǎn)生的功耗和熱量;8X內(nèi)存密度:包含300個內(nèi)存層,允許存儲更大的AI模型。據(jù)NEO估計(jì),每個芯片可支持高達(dá)10 TB/s的AI處理吞吐量。使用12個3D X- AI 芯片堆疊HBM封裝可實(shí)現(xiàn)120 TB/s處理吞吐量,性能提高100X。

這里的3D DRAM也是NEO半導(dǎo)體的研發(fā)方向之一。與水平放置存儲單元的傳統(tǒng)DRAM不同,3D DRAM垂直堆疊存儲單元大大增加單位面積的存儲容量并提高效率,成為下一代DRAM關(guān)鍵發(fā)展方向。

NEO表示,動態(tài)隨機(jī)存取存儲器(DRAM)用于支持處理器,使DRAM在電子設(shè)備中的使用更加普遍。然而,處理器速度的增長速度比多代內(nèi)存速度更快,由此產(chǎn)生的“性能差距”逐年擴(kuò)大。像云數(shù)據(jù)中心這樣的功耗敏感環(huán)境越來越依賴更高功率的處理器來滿足性能要求,但這會減少可用于內(nèi)存的功率。

采用X-DRAM架構(gòu)可以降低功耗,降低延遲,并增加吞吐量,以克服使用傳統(tǒng)DRAM時遇到的這些和其他挑戰(zhàn)。這為商業(yè)系統(tǒng)(例如服務(wù)器)提供了更高的性能,為移動設(shè)備(例如智能手機(jī))提供了更長的電池壽命,為邊緣計(jì)算設(shè)備(例如路由器)提供了更多的功能,并為物聯(lián)網(wǎng)對象(例如網(wǎng)關(guān))提供了新的部署選項(xiàng)。

3D X-DRAM的單元陣列結(jié)構(gòu)類似于3D NAND Flash,采用了FBC(無電容器浮體單元)技術(shù),它可以通過添加層掩模形成垂直結(jié)構(gòu),從而實(shí)現(xiàn)高良率、低成本和顯著的密度提升。NEO表示, 3D X-DRAM 技術(shù)可以生產(chǎn)230層的128Gbit DRAM 芯片,是當(dāng)前 DRAM 密度的八倍。近年來,SK海力士、三星電子、美光等存儲廠商都在進(jìn)行3D DRAM技術(shù)的研發(fā),以期滿足于AI浪潮下對高性能、大容量內(nèi)存的需求。

-

DRAM

+關(guān)注

關(guān)注

41文章

2392瀏覽量

189134 -

AI芯片

+關(guān)注

關(guān)注

17文章

2126瀏覽量

36771 -

3D DRAM

+關(guān)注

關(guān)注

1文章

3瀏覽量

4599

發(fā)布評論請先 登錄

鎧俠公布3D DRAM 技術(shù)

Socionext推出3D芯片堆疊與5.5D封裝技術(shù)

【「AI芯片:科技探索與AGI愿景」閱讀體驗(yàn)】+AI芯片到AGI芯片

【「AI芯片:科技探索與AGI愿景」閱讀體驗(yàn)】+AI的科學(xué)應(yīng)用

【「AI芯片:科技探索與AGI愿景」閱讀體驗(yàn)】+化學(xué)或生物方法實(shí)現(xiàn)AI

【「AI芯片:科技探索與AGI愿景」閱讀體驗(yàn)】+半導(dǎo)體芯片產(chǎn)業(yè)的前沿技術(shù)

【「AI芯片:科技探索與AGI愿景」閱讀體驗(yàn)】+AI的未來:提升算力還是智力

【「AI芯片:科技探索與AGI愿景」閱讀體驗(yàn)】+第二章 實(shí)現(xiàn)深度學(xué)習(xí)AI芯片的創(chuàng)新方法與架構(gòu)

【「AI芯片:科技探索與AGI愿景」閱讀體驗(yàn)】+AI芯片的需求和挑戰(zhàn)

【「AI芯片:科技探索與AGI愿景」閱讀體驗(yàn)】+可期之變:從AI硬件到AI濕件

【「AI芯片:科技探索與AGI愿景」閱讀體驗(yàn)】+內(nèi)容總覽

AI 芯片浪潮下,職場晉升新契機(jī)?

2025深圳3D打印增材制造展,臺灣高技即將亮相深圳增材展

3D DRAM內(nèi)嵌AI芯片,AI計(jì)算性能暴增

3D DRAM內(nèi)嵌AI芯片,AI計(jì)算性能暴增

評論