昨日,據報道日月光半導體公布了VIPack先進封裝平臺的重要進展——微間距芯粒互連技術。這一技術旨在滿足AI應用對Chiplet集成不斷增長的需求,相比傳統實現更大創新性及微縮價值。

這項技術采用新型金屬疊層于微凸塊之上,達成20μm(2*10-5米)芯片與晶圓之間的極致間距,較從前方案減少了一半。此舉大幅度增強了硅-硅互連能力,對其它開發過程大有裨益。

隨著Chiplet設計趨勢不斷演進,半導體互連帶寬呈爆炸式增加,使以往難以想象的IP模塊分割成為可能。

該項微間距互連技術使3D整合及更高I/O密度的存儲器耦合0成為可能。這一技術的推廣拓寬了Chiplet的應用領域,包括AI、移動處理器以及MCU等關鍵產品。

日月光集團研發處長李長祺總結道:“硅與硅互連已經經歷了焊錫凸塊向微凸塊的升級。隨著人工智,能時代的來臨,對更高級別的互連技術的需求也愈發迫切。借助新的微間距互連技術,我們正致力突破chiplet整合壁壘,并將持續挑戰技術極限以滿足市場需求。”

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

半導體

+關注

關注

339文章

30737瀏覽量

264158 -

日月光

+關注

關注

0文章

158瀏覽量

20156 -

先進封裝

+關注

關注

2文章

533瀏覽量

1027

發布評論請先 登錄

相關推薦

熱點推薦

北極芯微榮獲2025年深圳市高新技術企業認定

深圳北極芯微電子有限公司(北極芯微)近日正式通過深圳市2025年國家高新技術企業認定,獲頒"高新技術企業"資質。

Chiplet核心挑戰破解之道:瑞沃微先進封裝技術新思路

由深圳瑞沃微半導體科技有限公司發布隨著半導體工藝逐漸逼近物理極限,單純依靠芯片制程微縮已難以持續滿足人工智能、高性能計算等領域對算力密度與能效的日益苛刻需求。在這一背景下,Chiplet(芯粒)

強強合作 西門子與日月光合作開發 VIPack 先進封裝平臺工作流程

(FOCoS-Bridge),以及基于硅通孔(TSV)的 2.5D/3D IC 技術。 日月光 VIPack 由六大核心封裝技術支柱構成,基于全面集成的協同設計生

借助Arm芯粒技術構建計算未來

在我們近期與業界伙伴的多次交流中,明顯發現芯粒時代的大幕已徐徐拉開,行業已經不再抱存對芯粒的質疑態度,而是正在合作解決如何借助芯

臺積電日月光主導,3DIC先進封裝聯盟正式成立

與日月光攜手主導,旨在攻克先進封裝領域現存難題,推動產業邁向新高度。 據了解,3DIC AMA 的成員構成極為多元,廣泛涵蓋晶圓代工、封裝、設備與材料等多個關鍵領域的企業,首批加入的成

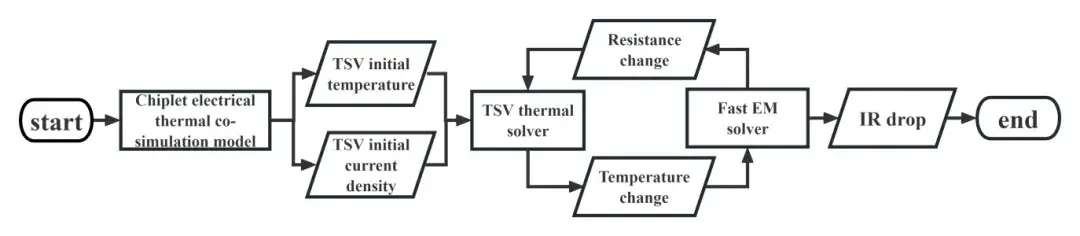

微電子所在芯粒集成電遷移EDA工具研究方向取得重要進展

隨著高性能人工智能算法的快速發展,芯粒(Chiplet)集成系統憑借其滿足海量數據傳輸需求的能力,已成為極具前景的技術方案。該技術能夠提供高速互連

華大九天推出芯粒(Chiplet)與2.5D/3D先進封裝版圖設計解決方案Empyrean Storm

隨著“后摩爾時代”的到來,芯粒(Chiplet)與 2.5D/3D 先進封裝技術正成為突破晶體管微縮瓶頸的關鍵路徑。通過異構集成將不同的芯片

日月光新專利展現柔性基板“織紋術”

電子發燒友網綜合報道 近日,日月光半導體于2025年6月9日獲得的增大電子元件與可撓性基板摩擦力的封裝結構專利(授權公告號CN222953077U),是其在柔性電子封裝領域的重要技術突

突破!華為先進封裝技術揭開神秘面紗

引發行業高度關注,為其在芯片領域的持續創新注入強大動力。 堆疊封裝,創新架構 華為公布的 “一種芯片堆疊封裝及終端設備” 專利顯示,其芯片堆疊封裝技術通過將多個芯片或

日月光最新推出FOCoS-Bridge TSV技術

日月光半導體最新推出FOCoS-Bridge TSV技術,利用硅通孔提供更短供電路徑,實現更高 I/O 密度與更好散熱性能,滿足AI/HPC對高帶寬與高效能的需求。

日月光精彩亮相SEMICON SEA 2025

在這個充滿“前所未有“挑戰的多極化世界里,為期三天的SEMICON SEA于5月20-22日在新加坡濱海灣金沙會展中心成功召開,日月光精彩亮相。展廳現場人頭攢動,與會者所散發的能量有力彰顯了半導體行業不屈不撓的精神。

日月光推出先進封裝平臺新技術:微間距芯粒互連技術

日月光推出先進封裝平臺新技術:微間距芯粒互連技術

評論