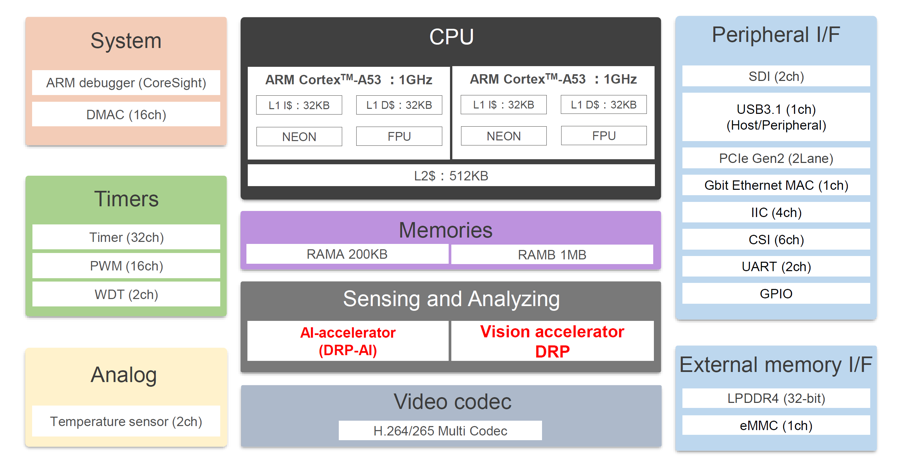

瑞薩最新發(fā)布的動(dòng)態(tài)可重構(gòu)人工智能處理器(DRP-AI)加速器,在業(yè)界引起了廣泛關(guān)注。這款加速器擁有卓越的10 TOPS/W高功率效率,相比傳統(tǒng)技術(shù),效率提升了驚人的10倍。其獨(dú)特之處在于,它能在低功耗的傳統(tǒng)嵌入式處理器(MPU)上運(yùn)行復(fù)雜的圖像AI模型,不再需要依賴高功耗的GPU。

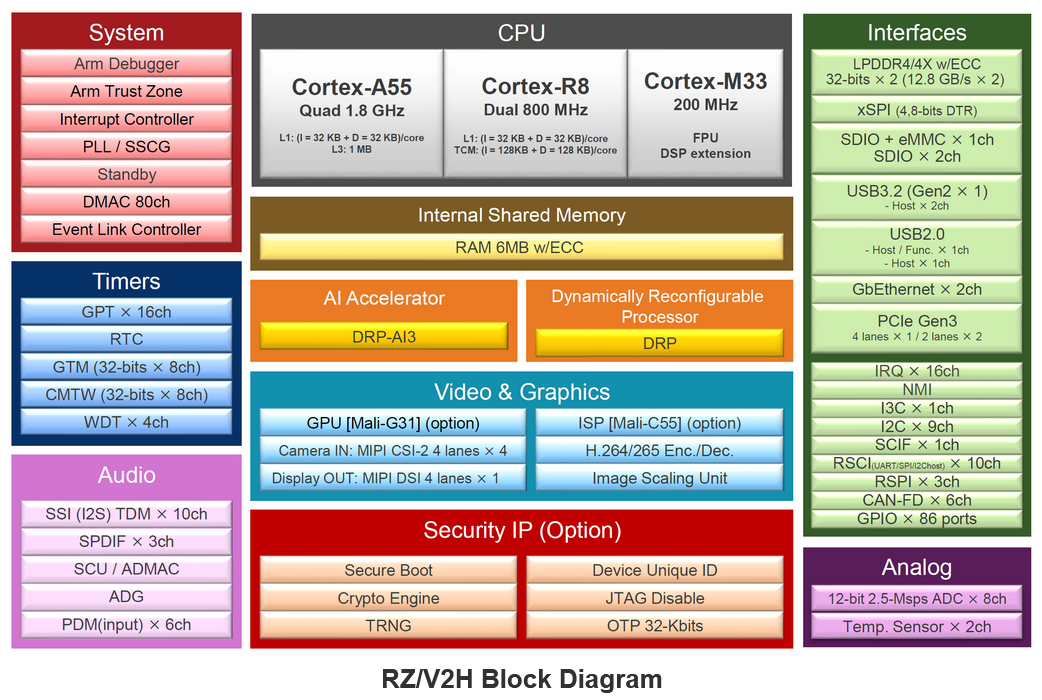

不僅如此,瑞薩還推出了高端RZ/V2H MPU,它集成了多項(xiàng)先進(jìn)技術(shù)。這款MPU配備了圖像處理加速器,使用動(dòng)態(tài)可重構(gòu)處理器(DRP),同時(shí)擁有運(yùn)行頻率高達(dá)1.8GHz的四核Linux處理器Arm Cortex-A55、雙核800MHz Arm Cortex-R8高速實(shí)時(shí)處理器,以及I/O處理Arm Cortex-M33子內(nèi)核,形成了強(qiáng)大的異構(gòu)多處理器配置。這一創(chuàng)新設(shè)計(jì)將為用戶帶來更高效、更靈活的解決方案,滿足多樣化的市場需求。

-

處理器

+關(guān)注

關(guān)注

68文章

20250瀏覽量

252192 -

瑞薩

+關(guān)注

關(guān)注

37文章

22481瀏覽量

90851 -

人工智能

+關(guān)注

關(guān)注

1817文章

50094瀏覽量

265263

發(fā)布評(píng)論請先 登錄

華為在MWC 2026正式發(fā)布下一代WAN目標(biāo)網(wǎng)架構(gòu)

奇異摩爾參編人工智能加速器互聯(lián)芯粒技術(shù)要求團(tuán)體標(biāo)準(zhǔn)發(fā)布

Ceva在恩智浦的軟件定義車輛處理器上實(shí)現(xiàn) 實(shí)時(shí)人工智能加速

d-Matrix與Andes晶心科技合作打造下一代AI推理加速器

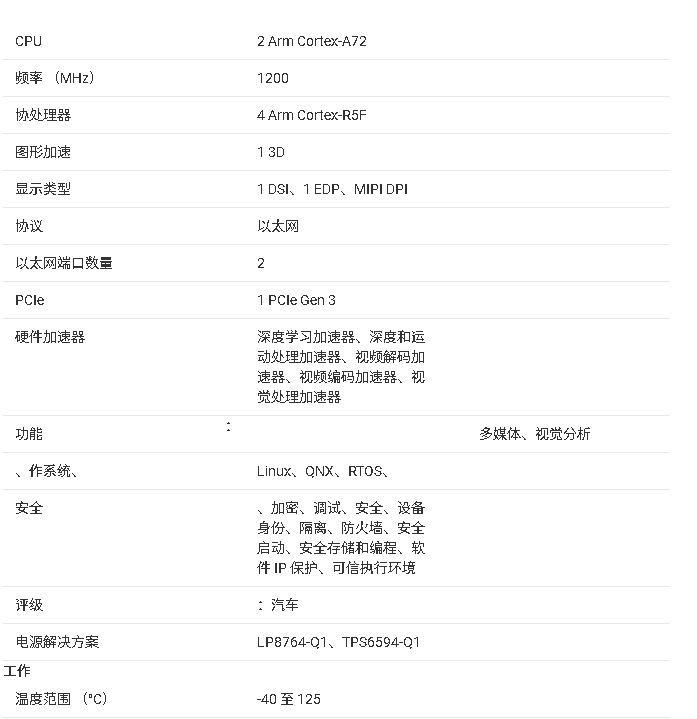

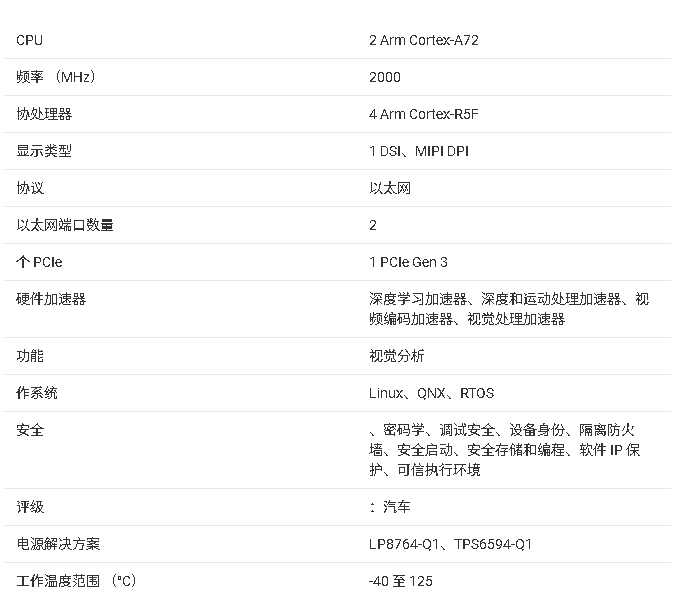

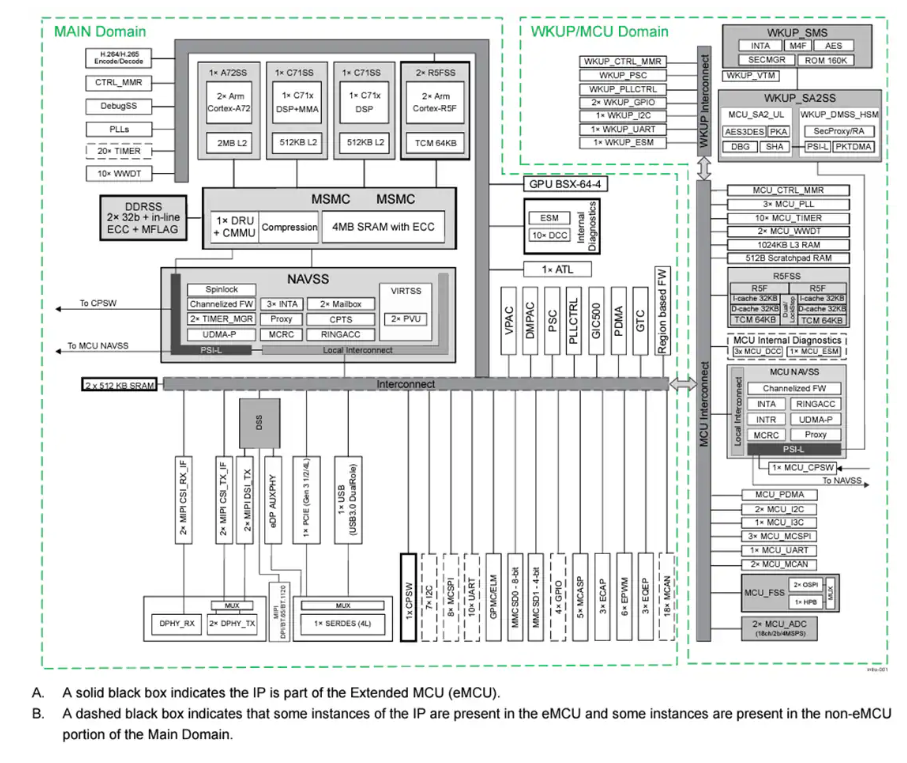

TDA4VL-Q1處理器技術(shù)文檔總結(jié)

TDA4AL-Q1處理器的技術(shù)文檔摘要

瑞薩電子RZ/V系列微處理器助力邊緣AI開發(fā)

Flex Power Modules將與瑞薩電子合作推出下一代電源管理解決方案

德州儀器TDA4VE/TDA4AL/TDA4VL Jacinto?處理器技術(shù)解析

關(guān)于人工智能處理器的11個(gè)誤解

Ampere如何引領(lǐng)并塑造下一代人工智能計(jì)算系統(tǒng)

支持實(shí)時(shí)物體識(shí)別的視覺人工智能微處理器RZ/V2MA數(shù)據(jù)手冊

AI MPU# 瑞薩RZ/V2H 四核視覺 ,采用 DRP-AI3 加速器和高性能實(shí)時(shí)處理器

Banana Pi 與瑞薩電子攜手共同推動(dòng)開源創(chuàng)新:BPI-AI2N

瑞薩推出集成DRP-AI加速器的RZ/V2N,擴(kuò)展中端AI處理器陣容,助力未來智能工廠與智慧城市發(fā)展

瑞薩發(fā)布下一代動(dòng)態(tài)可重構(gòu)人工智能處理器加速器

瑞薩發(fā)布下一代動(dòng)態(tài)可重構(gòu)人工智能處理器加速器

評(píng)論