TDA4VE TDA4AL TDA4VL 處理器系列基于進化的 Jacinto? 7 架構,面向智能視覺相機應用,并建立在 TI 十多年來在視覺處理器市場領導地位積累的廣泛市場知識之上。TDA4AL 以行業領先的功率/性能比為傳統和深度學習算法提供高性能計算,并具有高水平的系統集成度,可為高級視覺相機應用實現可擴展性和降低成本。關鍵核心包括具有標量和矢量內核的下一代 DSP、專用深度學習和傳統算法加速器、用于通用計算的最新 Arm 和 GPU 處理器、集成的下一代成像子系統 (ISP)、視頻編解碼器和隔離的 MCU 島。所有這些都受到汽車級安全和安保硬件加速器的保護。

*附件:tda4al-q1.pdf

關鍵性能內核概述:“C7x”下一代 DSP 將 TI 行業領先的 DSP 和 EVE 內核組合到一個更高性能的內核中,并增加了浮點矢量計算功能,從而實現了傳統代碼的向后兼容性,同時簡化了軟件編程。新型“MMA”深度學習加速器在125°C的典型汽車最壞情況結溫下運行時,可在業界最低的功耗范圍內實現高達8 TOPS的性能。 專用的 Vision 硬件加速器提供視覺預處理,而不會影響系統性能。

通用計算核心和集成概述:Arm? Cortex-A72? 的獨立雙核集群配置有助于多作系統應用,而對軟件管理程序的需求極低。多達四個 Arm? Cortex-R5F? 子系統支持低級、時序關鍵的處理任務,使 Arm? Cortex-A72? 內核不受應用的阻礙。TI 的第 7 代 ISP 以現有的世界級 ISP 為基礎,具有處理更廣泛傳感器套件的靈活性、對更高位深度的支持以及針對分析應用的功能。集成的診斷和安全功能支持高達 ASIL-D 級別的作,而集成的安全功能可保護數據免受現代攻擊。CSI2.0 端口支持多傳感器輸入。為了進一步集成,TDA4VE、TDA4AL、TDA4VL 系列還包括一個 MCU 島,無需外部系統微控制器。

特性

處理器內核:

- 兩個 C7x 浮點,矢量 DSP,高達 1.0GHz,160GFLOPS,512GOPS

- 深度學習矩陣乘法加速器 (MMA),在 1.0GHz 時高達 8TOPS (8b)

- 具有圖像信號處理器 (ISP) 和多個視覺輔助加速器的視覺處理加速器 (VPAC)

- 深度和運動處理加速器 (DMPAC)

- 雙 64 位 Arm Cortex-A72 微處理器子系統,頻率高達 2GHz

- 多達六個 Arm Cortex-R5F MCU,頻率高達 1.0GHz

- 16K I-Cache、16K D-Cache、64K L2 TCM

- 隔離式 MCU 子系統中的兩個 Arm Cortex-R5F MCU

- 通用計算分區中的四個 (TDA4VE) 或兩個 (TDA4AL/TDA4VL) Arm Cortex-R5F MCU

- GPU IMG BXS-4-64,256kB 緩存,高達 800MHz,50GFLOPS,4GTexels/s(TDA4VE 和 TDA4VL)

- 定制設計的互連結構,支持接近最大處理授權

內存子系統:

- 高達 4MB 的片上 L3 RAM,具有 ECC 和一致性

- ECC 錯誤保護

- 共享相干緩存

- 支持內部 DMA 引擎

- 多達兩個帶 ECC 的外部存儲器接口 (EMIF) 模塊

- 支持 LPDDR4 內存類型

- 支持高達 4266MT/s 的速度

- 兩個 (TDA4VE) 或一個 (TDA4AL/TDA4VL) 32 位數據總線,具有內聯 ECC,每個 EMIF 高達 17GB/s

- 通用內存控制器 (GPMC)

- 主域中的一個 (TDA4AL/TDA4VL) 或兩個 (TDA4VE) 片上 SRAM,受 ECC 保護

功能安全:

- 符合功能安全標準(在特定部件號上)

- 專為功能安全應用而開發

- 提供文檔,以幫助 ISO 26262 功能安全系統設計,最高可達 ASIL-D/SIL-3 目標

- 系統能力高達 ASIL-D/SIL-3 靶向

- 硬件完整性高達 ASIL-D/SIL-3,適用于 MCU 域

- 硬件完整性高達 ASIL-B/SIL-2,針對主域

- 硬件完整性高達 ASIL-D/SIL-3,適用于主域的擴展 MCU (EMCU) 部分

- 安全相關認證

- 計劃通過 ISO 26262

設備安全性(在特定部件號上):

高速串行接口:

- 一個 PCI-Express (PCIe) Gen3 控制器

- 每個控制器最多四個通道

- 具有自動協商功能的 Gen1 (2.5GT/s)、Gen2 (5.0GT/s) 和 Gen3 (8.0GT/s)作

- 一個 USB 3.0 雙角色設備 (DRD) 子系統

- 增強型 SuperSpeed Gen1 端口

- 支持Type-C切換

- 可獨立配置為 USB 主機、USB 外設或 USB DRD

- 兩個 CSI2.0 4L 攝像頭串行接口 RX (CSI-RX) 和兩個帶 DFY 的 CSI2.0 4L TX (CSI-TX)

- 符合 MIPI CSI 1.3 + MIPI-DPHY 1.2 標準

- CSI-RX 支持 1、2、3 或 4 個數據通道模式,每通道高達 2.5Gbps

- CSI-TX 支持 1、2 或 4 個數據通道模式,每通道高達 2.5Gbps

汽車接口:

- 20 個模塊化控制器局域網 (MCAN) 模塊,完全支持 CAN-FD

顯示子系統:

- 一個 (TDA4AL/TDA4VL) 或兩個 (TDA4VE) DSI 4L TX(高達 2.5K)

- 一個 eDP 4L (TDA4VE/TDA4VL)

- 一個 DPI

音頻接口:

- 五個多通道音頻串行端口 (MCASP) 模塊

視頻加速:

- TDA4VE:H.264/H.265 編碼/解碼(高達 480MP/s)

- TDA4AL:僅 H.264/H.265 編碼(高達 480MP/s)

- TDA4VL:H.264/H.265 編碼/解碼(高達 240MP/s)

以太網:

- 兩個 RMII/RGMII 接口

閃存接口:

- 嵌入式多媒體卡接口 (eMMC? 5.1)

- 一個安全數字 3.0/安全數字輸入輸出 3.0 接口 (SD3.0/SDIO3.0)

- 兩個同時閃存接口配置為

- 一個 OSPI 或 HyperBus? 或 QSPI,以及

- 一個 QSPI

片上系統 (SoC) 架構:

- 16納米FinFET技術

- 23mm x 23mm,0.8mm間距,770引腳FCBGA (ALZ)

- 符合功能安全標準,支持高達 ASIL-D / SIL-3 目標

- 靈活的映射以支持不同的用例

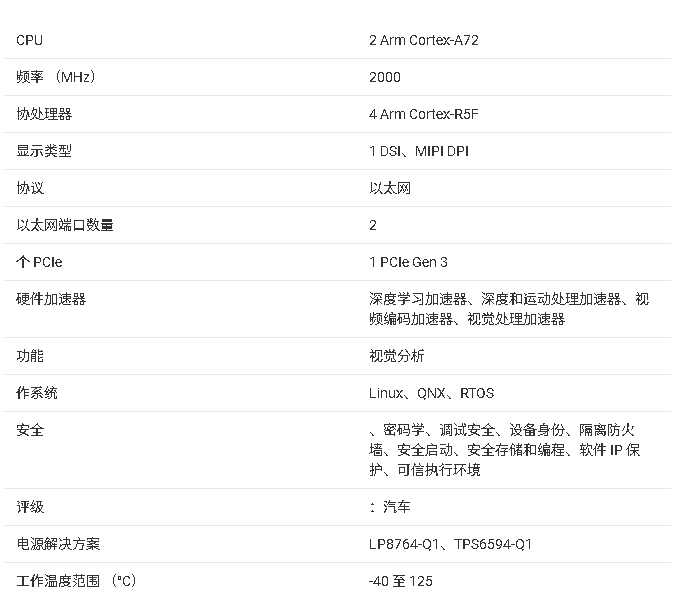

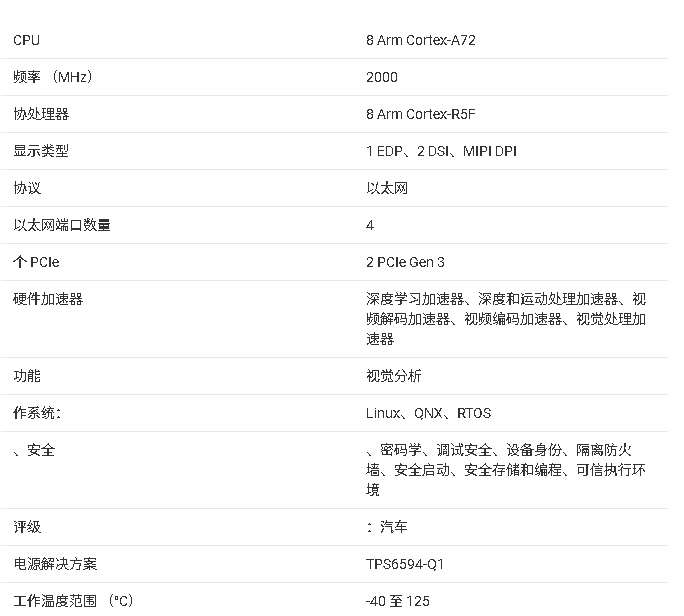

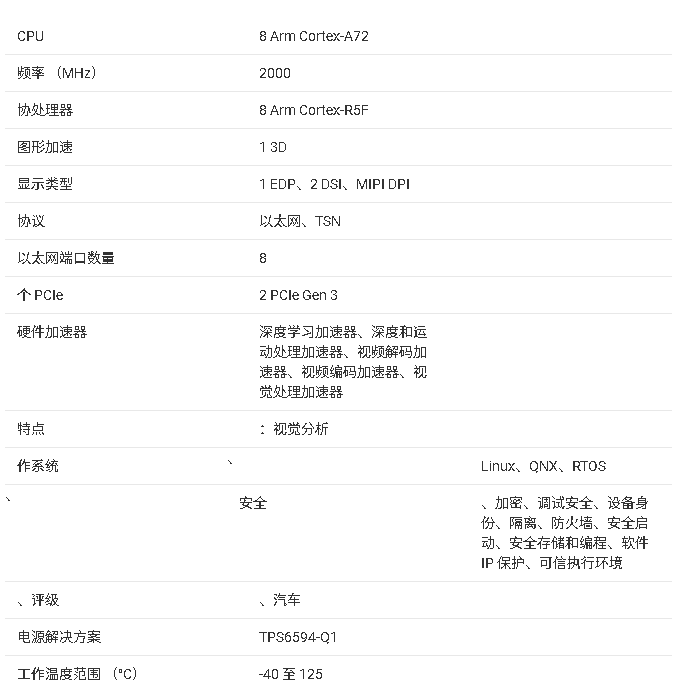

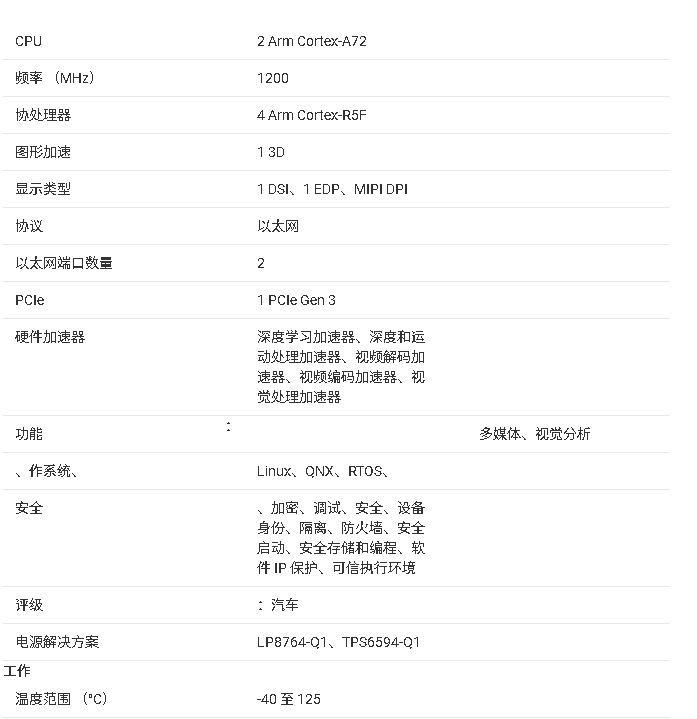

參數

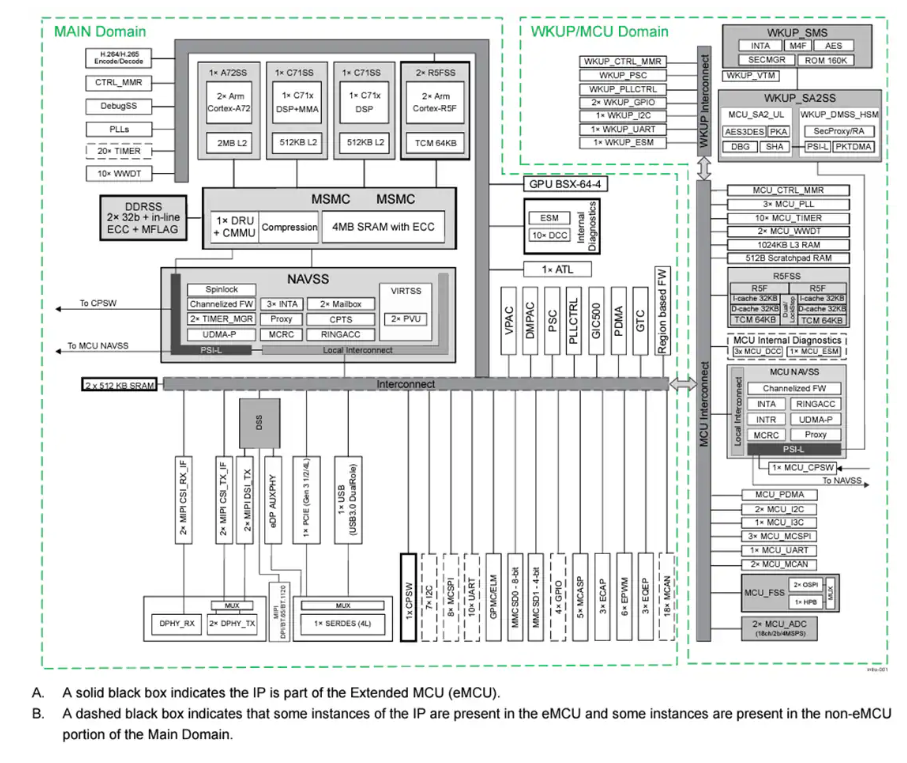

方框圖

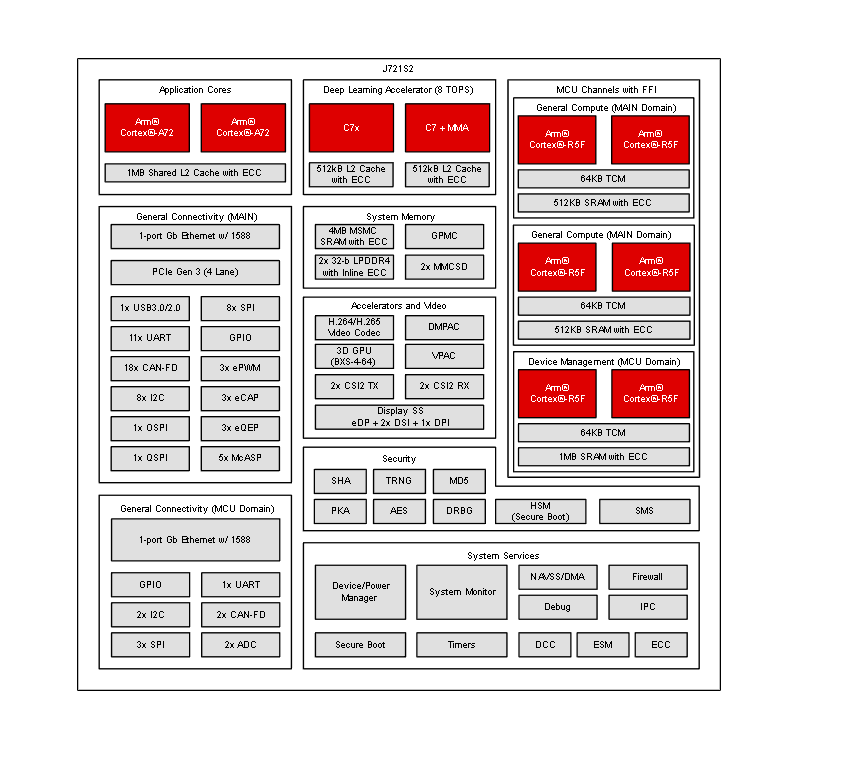

?1. 核心架構?

- ?處理器核心?:

- 雙核Arm Cortex-A72(最高2GHz)

- 6個Cortex-R5F MCU(最高1GHz)

- C7x浮點/矢量DSP(1GHz,160GFLOPS)

- 深度學習加速器MMA(8TOPS@8b)

- ?圖形處理?:IMG BXS-4-64 GPU(800MHz,50GFLOPS)

- ?視頻編解碼?:

- TDA4VE:H.264/H.265編解碼(480MP/s)

- TDA4AL:僅編碼(480MP/s)

- TDA4VL:編解碼(240MP/s)

?2. 內存子系統?

- 片上L3 RAM:4MB(帶ECC)

- 外部內存接口:支持LPDDR4(最高4266MT/s)

- 存儲控制器:GPMC、eMMC 5.1、SD 3.0/SDIO 3.0

?3. 功能安全?

- 符合ISO 26262標準(ASIL-D/SIL-3目標)

- 硬件完整性:MCU域支持ASIL-D,主域支持ASIL-B

?4. 安全特性?

- 安全啟動與運行時支持

- 可編程根密鑰(RSA-4K/ECC-512)

- 硬件加密加速器(AES/SHA/RNG等)

?5. 高速接口?

- PCIe Gen3(4通道)

- USB 3.0 DRD

- 雙千兆以太網(RGMII/RMII)

- MIPI CSI-2 RX/TX(4通道,2.5Gbps/通道)

?6. 封裝與工藝?

- 16nm FinFET技術

- 23×23mm FCBGA封裝(770引腳)

?7. 目標應用?

文檔還包含詳細的引腳配置、電氣特性、時序參數及安全認證信息,適用于汽車和工業級應用場景。

-

處理器

+關注

關注

68文章

20300瀏覽量

253740 -

gpu

+關注

關注

28文章

5232瀏覽量

135887 -

視頻編解碼器

+關注

關注

0文章

25瀏覽量

11933 -

深度學習

+關注

關注

73文章

5601瀏覽量

124537

發布評論請先 登錄

RK3399處理器與AR9201處理器有哪些不同之處呢

Jacinto7處理器攝像頭接入和ISP的處理能力

AMD Athlon 4處理器

恩智浦獲得ARM Cortex-M4處理器授權

蘋果a6處理器怎么樣_a6處理器參數

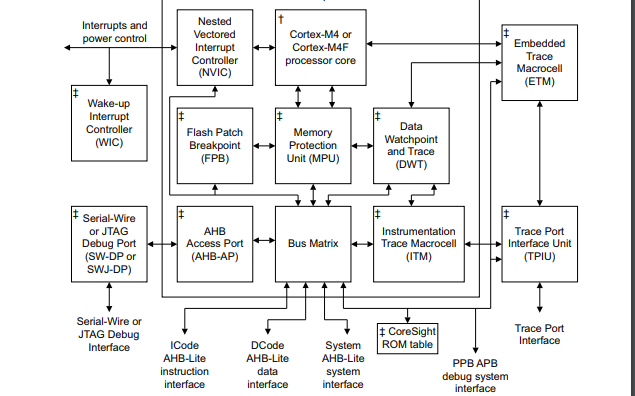

Cortex-M4處理器的技術參考手冊免費下載

麒麟9000處理器和高通驍龍875處理器相比如何?

TDA4VE/TDA4AL/TDA4VL SoC處理器

TDA4VE TDA4AL TDA4VL Jacinto?處理器數據表

適用于ADAS和自動駕駛汽車的TDA4VH-Q1、TDA4AH-Q1、TDA4VP-Q1、TDA4AP-Q1 Jacinto? 處理器數據表

德州儀器TDA4VE/TDA4AL/TDA4VL Jacinto?處理器技術解析

TDA4AL-Q1處理器的技術文檔摘要

TDA4AL-Q1處理器的技術文檔摘要

評論