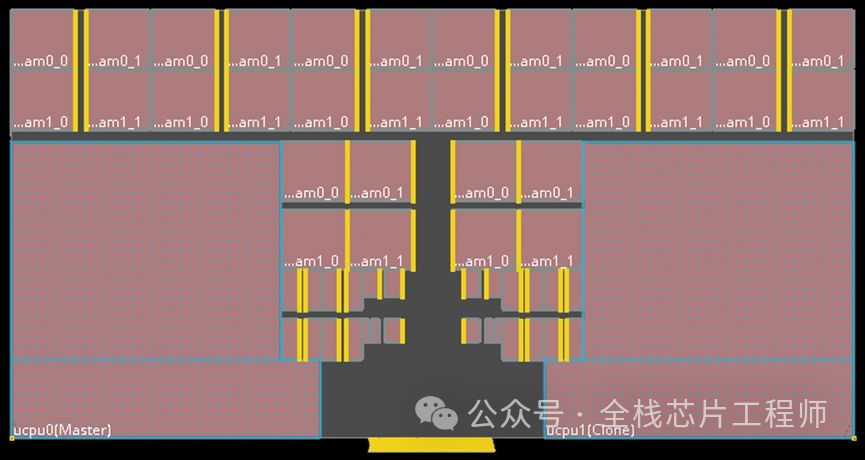

下面Cortex-A72培訓營VIP學員問:單核CPU PR做完后,怎么輸出數據到TOP去做多核的hierarchy集成?

答:單核CPU做好后,需要輸出SDC、DEF、LEF、GDS、Netlist、LIB等庫文件,然后做TOP的hierarchy設計。

比如抽取lib命令如下:

do_extract_model -view $VIEW ./$DESIGN.$VIEW.lib

其他命令請參考服務器腳本!

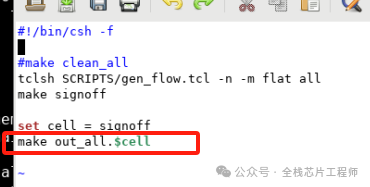

Cortex-A72培訓營VIP學員問:我想讓invs出lib,但是release的時候。view全被remove了。不清楚怎么回事?

答:analysis_view是空的原因是-noTiming造成的,如下圖:

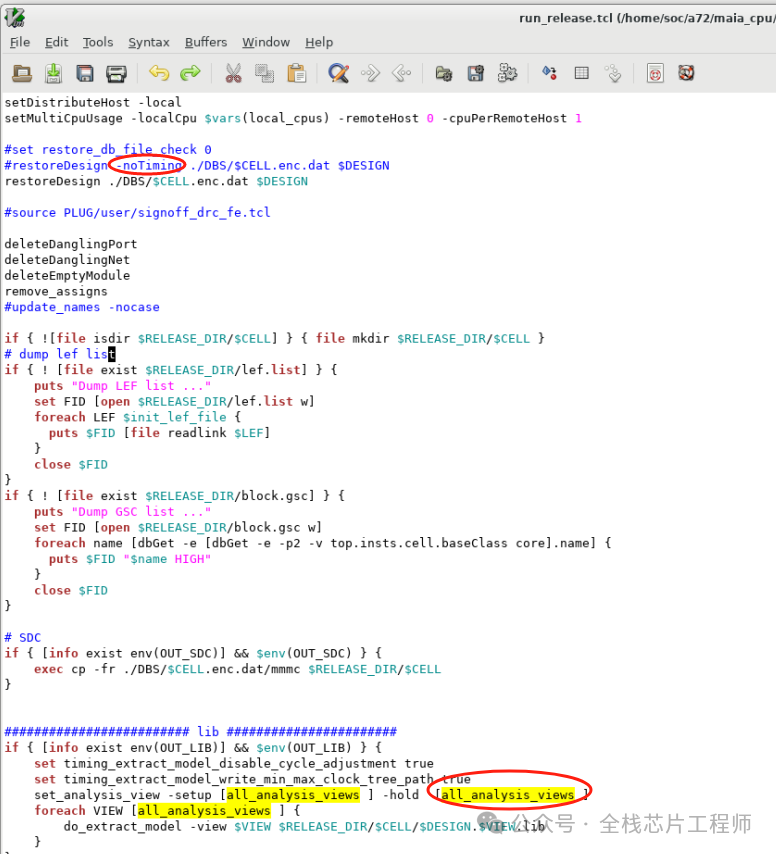

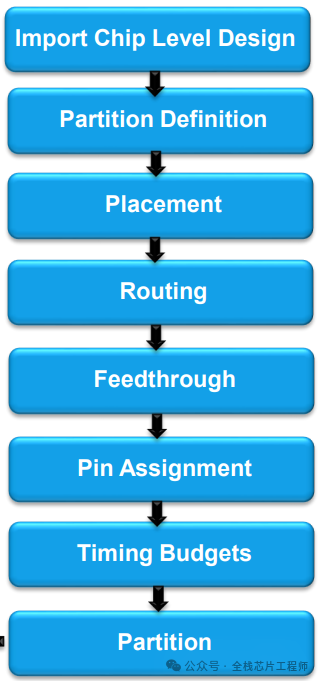

Cortex-A72培訓營VIP學員問:partition時,pin在哪個步驟assign的?

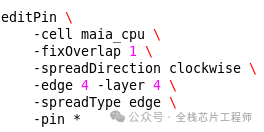

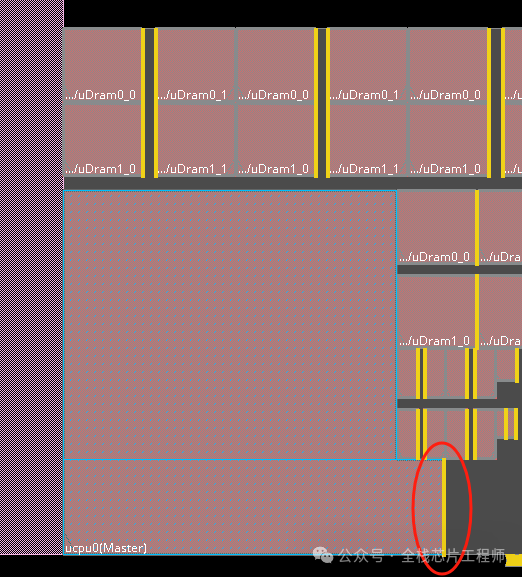

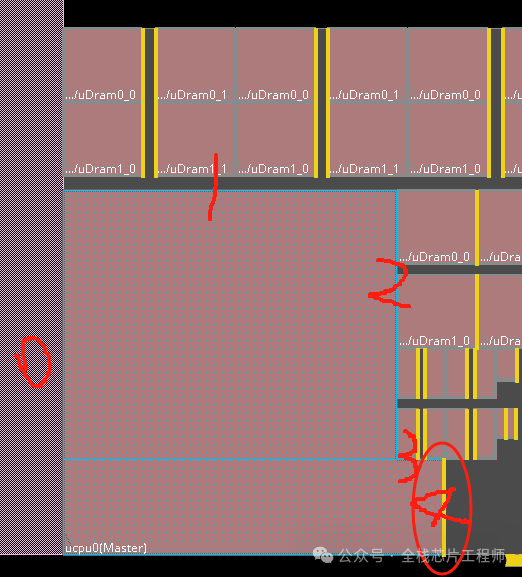

答:partition時候加如下腳本即可editPin:

比如:

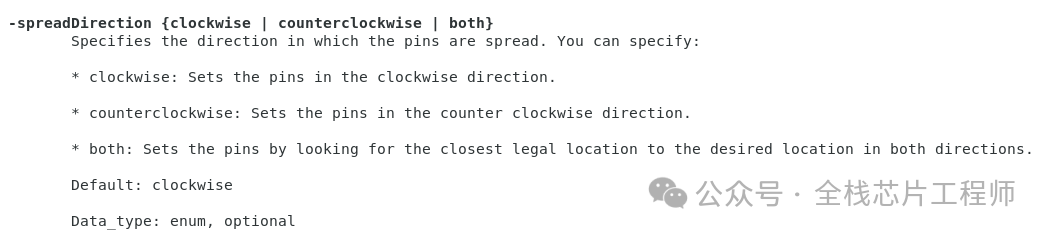

clockwise是pin的順序

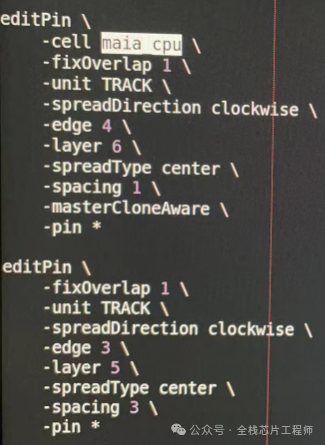

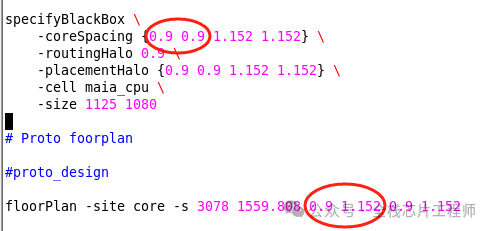

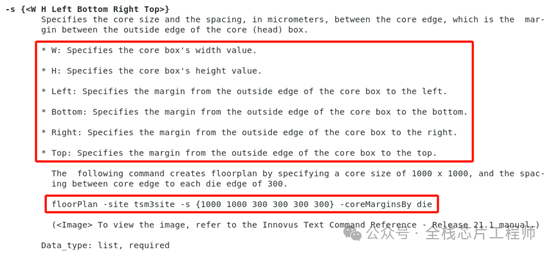

Cortex-A72培訓營VIP學員問:下面坐標寫錯了?

答:floorplan時的格式如下圖,左下右上,但是specifyBlackBox的-coreSpacing順序是左右上下!

Cortex-A72培訓營VIP學員問:0.9 1.152是基于什么考慮來確定的數值啊?

答:1.152 是上下兩個site的高度,0.9應該也是左右site的寬度倍數 或者met pitch倍數。

“12nm工藝,2.5GHz頻率,Cortex-A72處理器中后端實戰培訓”

01 —Cortex-A72處理器—數字后端實戰

本項目是真實項目實戰培訓,低功耗UPF設計,后端參數如下:

工藝:12nm

頻率:2.5GHz

資源:2000_0000instances

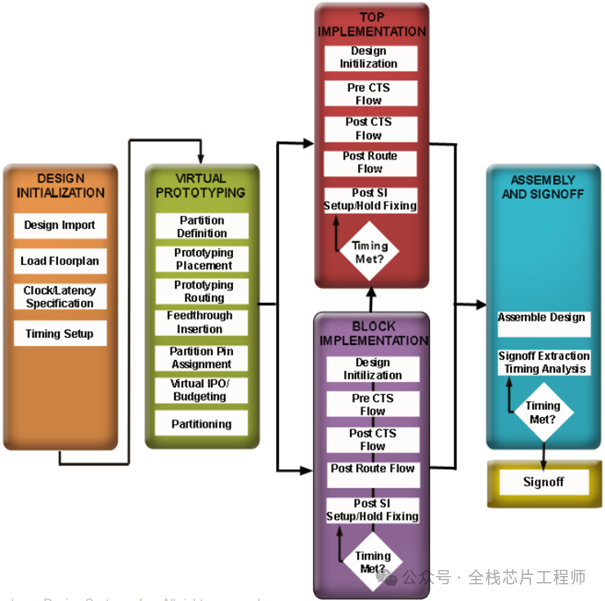

Flow:PartitionFlow

Partition步驟:

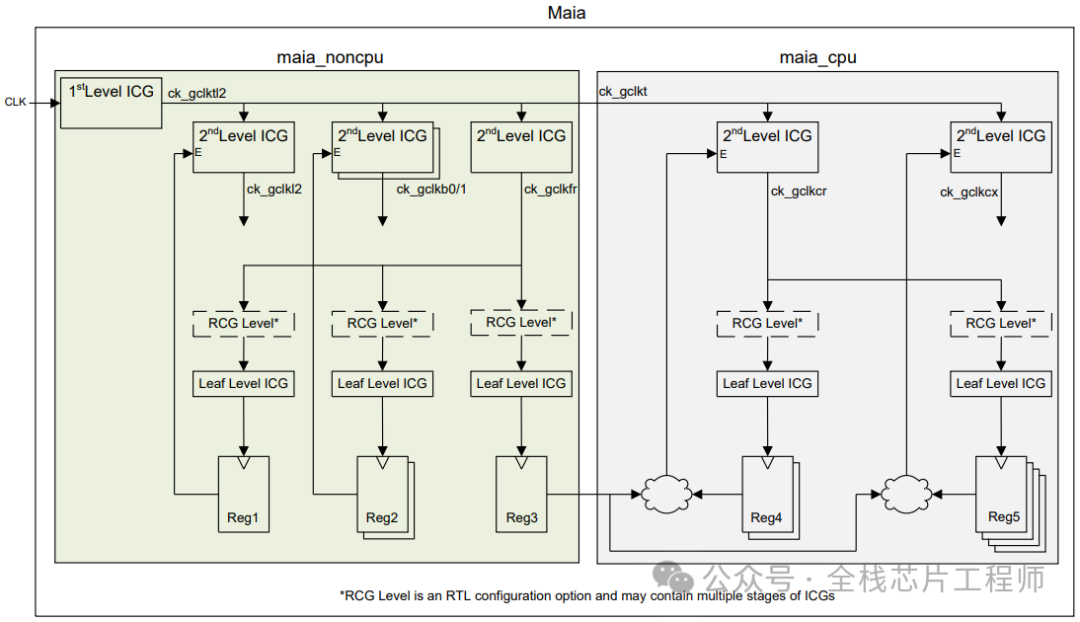

時鐘結構分析:

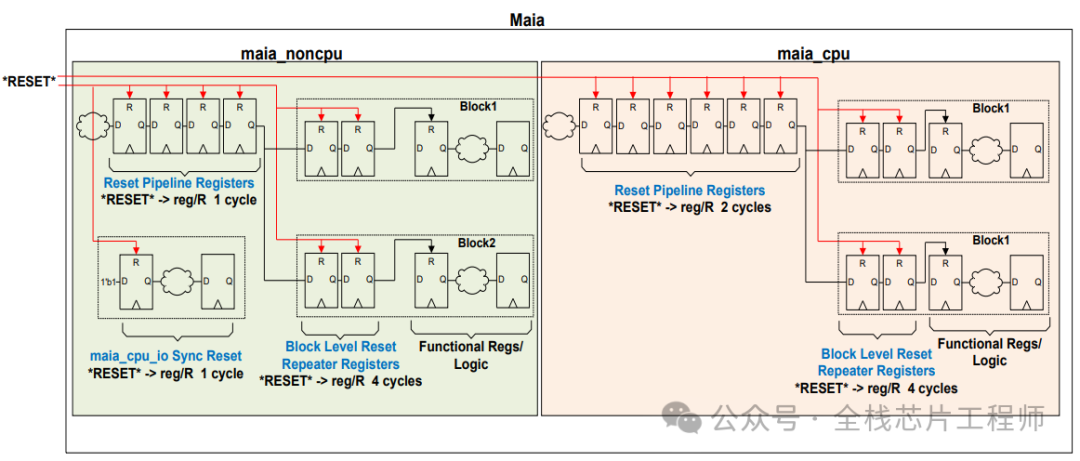

復位結構分析:

我們來對比下A72與A7的資源。A72Gate數目是A7的13倍!如果都采用28nm制程,A72的面積應該是1180790um^2,實際A72采用12nm制程面積是486100um^2,1180790/486100=2.4,符合摩爾定律。

Cortex-A7單核:

Gates=240291Cells=118421

Cortex-A72單核:

Gates=3125649Cells=1207766

28nmCortex-A7單核:

Area=90830.1um^2

12nmCortex-A72單核:

Area=486100.9um^2

審核編輯:湯梓紅

-

cpu

+關注

關注

68文章

11277瀏覽量

224951 -

命令

+關注

關注

5文章

755瀏覽量

23747 -

腳本

+關注

關注

1文章

409瀏覽量

29192

原文標題:12nm工藝,2.5GHz頻率,Cortex-A72實戰

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

ARM最新Cortex-A72架構劍指PC,英特爾麻煩了?

ARM Cortex-A72性能狂飆:要超越Intel的節奏?

ARM Cortex-A72 MPCore處理器加密擴展技術參考手冊

將GICv2中斷控制器與ARM Cortex-A5x和Cortex-A72處理器集成

ARM Cortex?-A72 MPCore處理器技術參考手冊

Cortex-A72 MPCore軟件開發人員勘誤表

聯發科MT8173芯片詳解:兩個Cortex-A53核心和兩個Cortex-A72

Versal ACAP,APU - 當有逐出傳輸事務處于暫掛狀態時,外部數據嗅探可能導致數據損壞

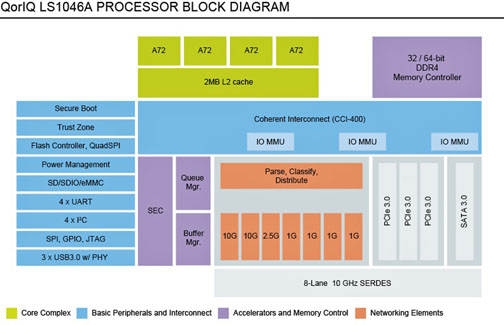

基于四核Cortex-A72的CPU QorIQ LS1046A 64 位處理器

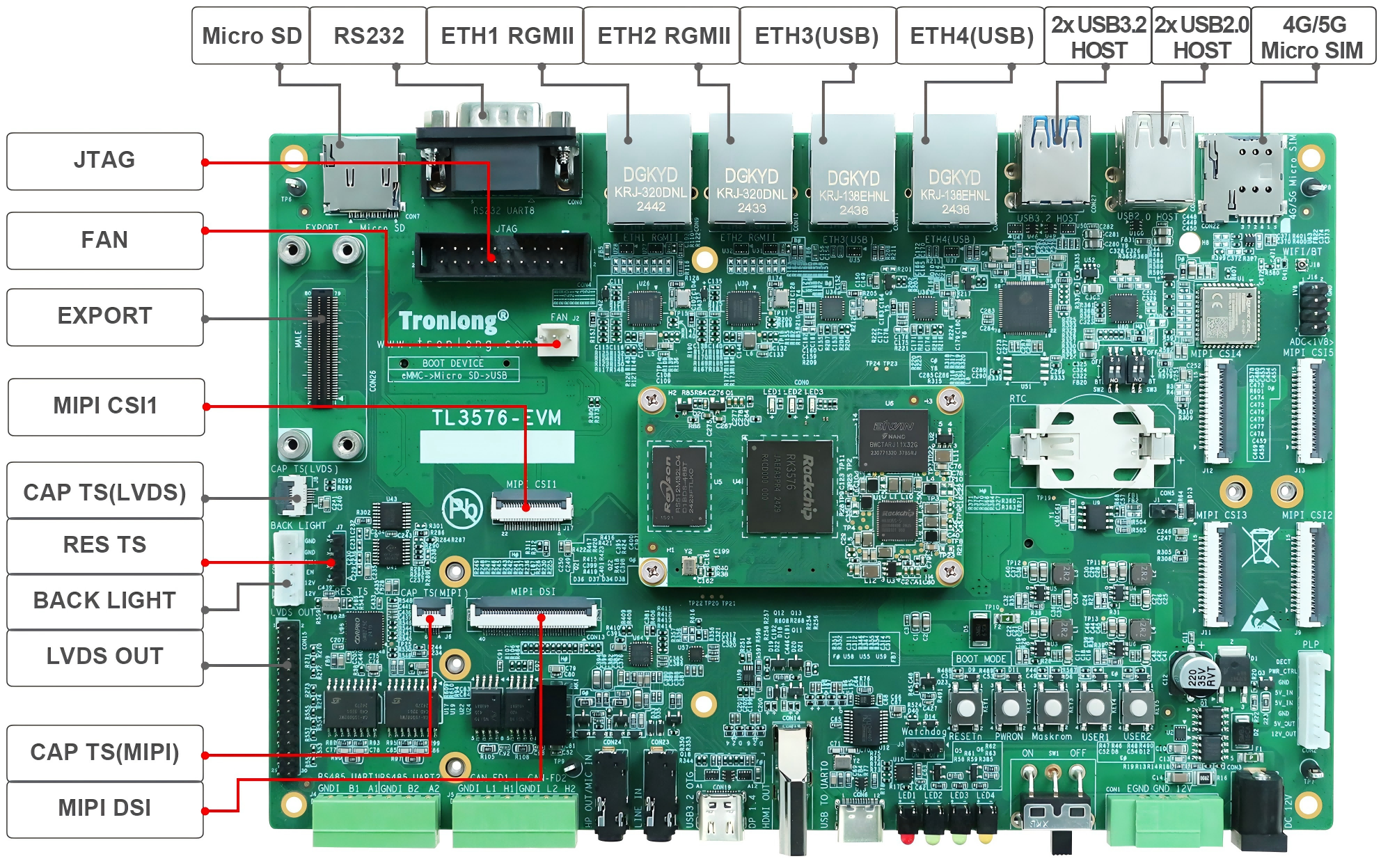

Cortex-A72核心板 | RK3399六核

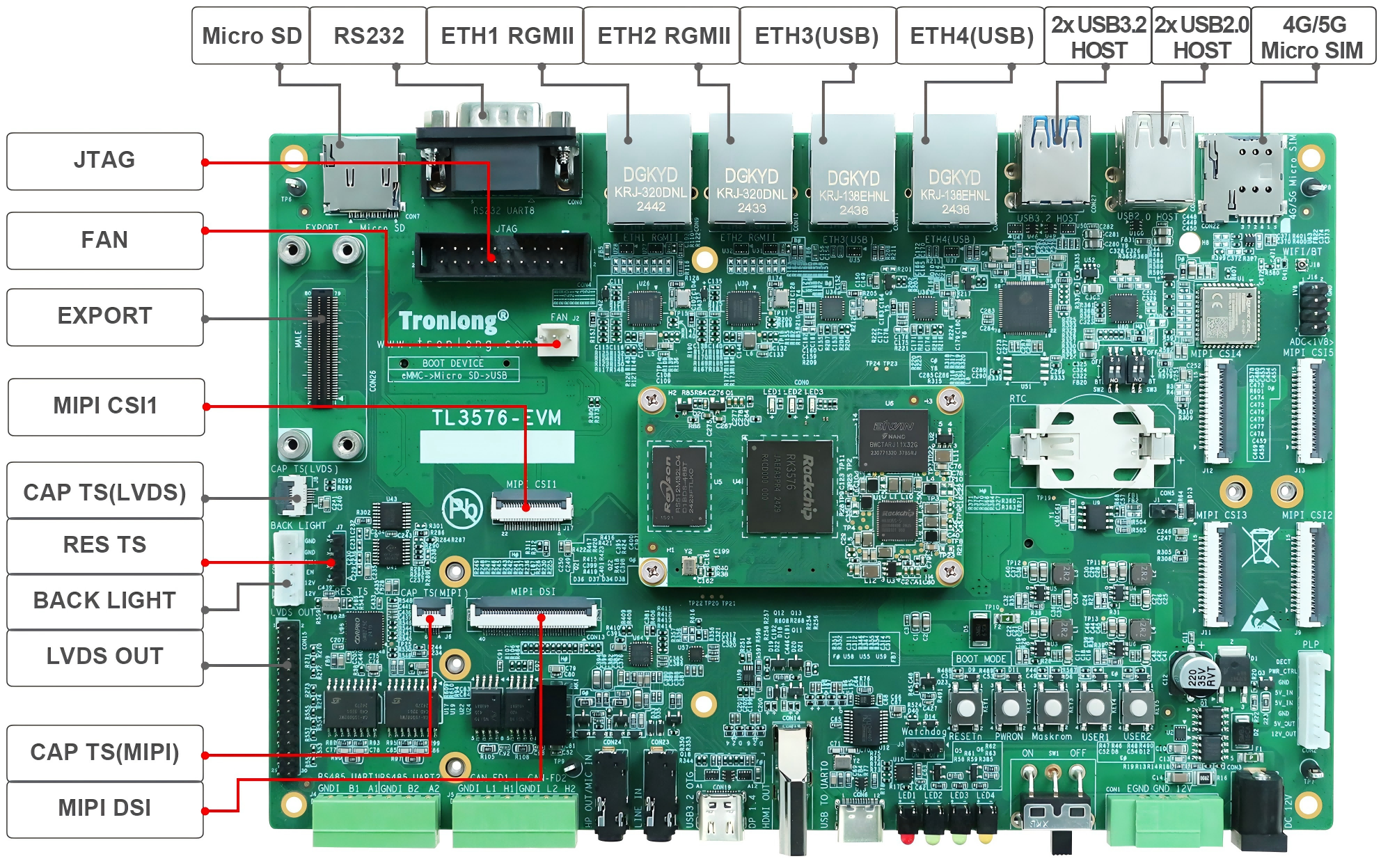

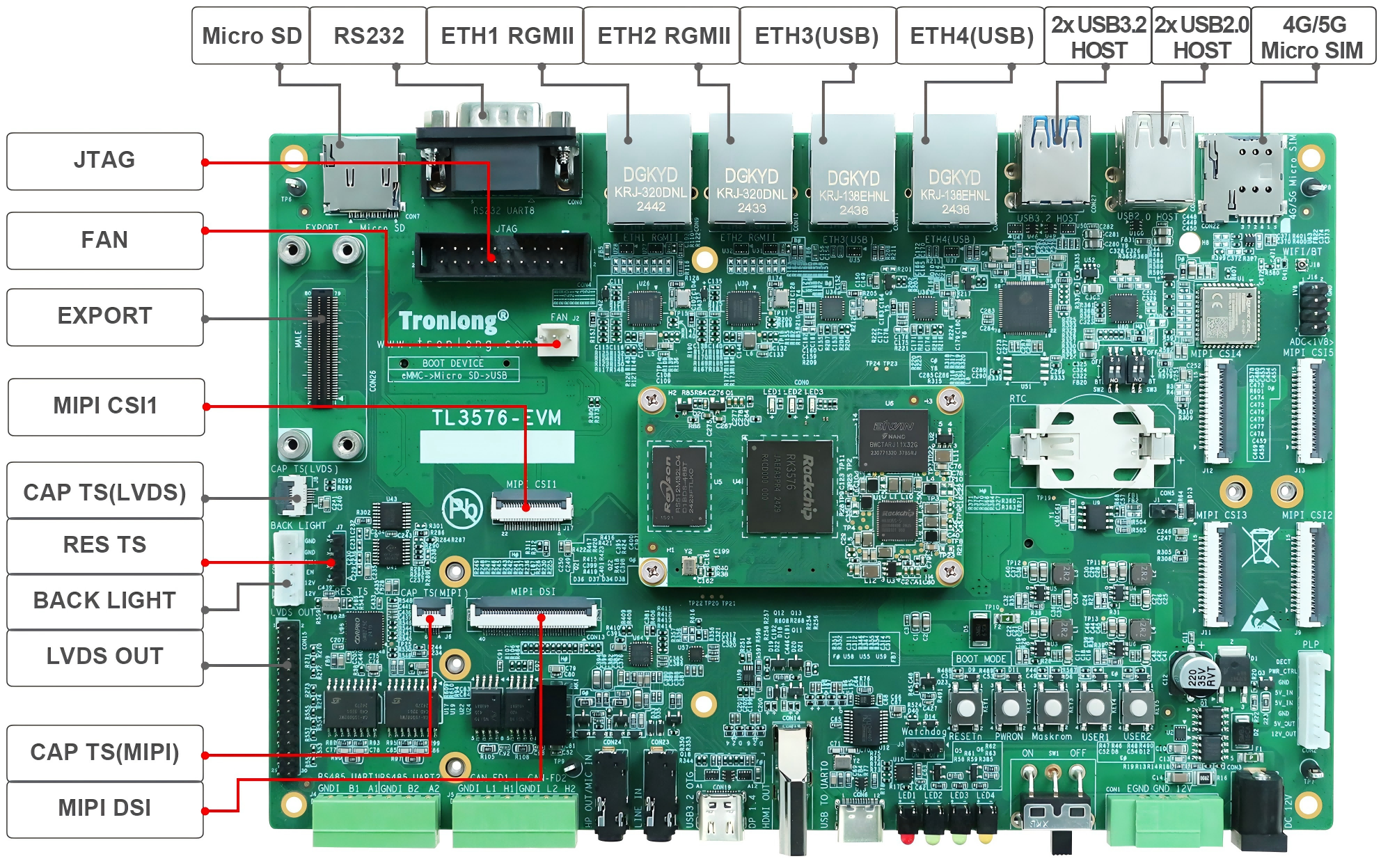

全國產!瑞芯微 RK3576 ARM 八核 2.2GHz 工業開發板—LVGL應用開發案例

全國產!瑞芯微 RK3576 ARM 八核 2.2GHz 工業開發板—Linux系統使用手冊

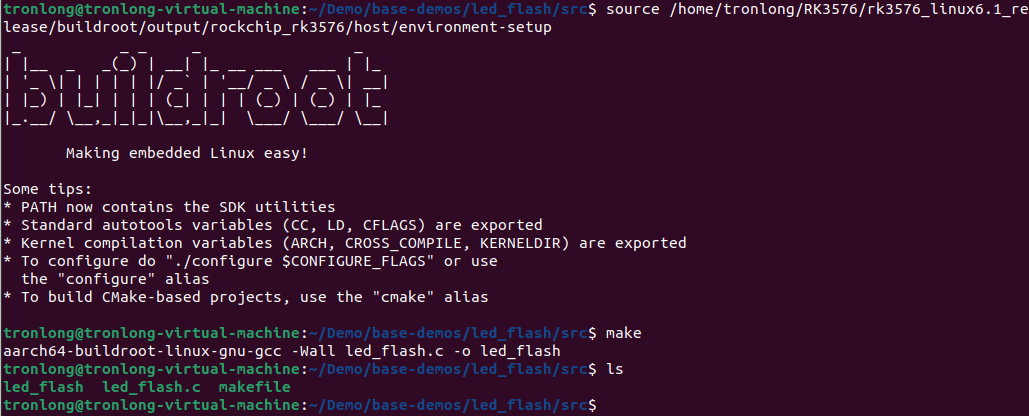

全國產!瑞芯微 RK3576 ARM 八核 2.2GHz 工業開發板—Linux開發環境搭建

全國產!瑞芯微 RK3576 ARM 八核 2.2GHz 工業開發板—Linux應用開發手冊

Cortex-A72應用實戰

Cortex-A72應用實戰

評論