異構集成主要指將多個不同工藝節點單獨制造的芯片封裝到一個封裝內部,以增強功能性和提高性能。異構計算是指將CPU、GPU、FPGA、DSP等不同架構的運算單元整合到一起進行并行計算。

1)異 構集 成

異構集成(Heterogeneous Integration)

異構集成通常和單片集成電路(monolithic)相對應,我們常見的芯片都是單片集成電路,它們屬于同構集成(homogeneous Integration),意味著在同一種材料上制作出所有元件。這曾經是杰克?基爾比(Jack Kilby)的偉大夢想,并最終成為現實,進而推動了信息技術的巨大進步,對人類文明的進步也產生重大影響。

異構集成和同構集成二者并不相互排斥,所有異構集成的單元都是同構集成。

異構集成(Heterogeneous Integration)準確來講,全稱為異構異質集成,異構集成可看作是其漢語的簡稱,這里,我們將其分為異構(HeteroStructure)集成和異質(HeteroMaterial)集成兩大類。

HeteroStructureIntegration

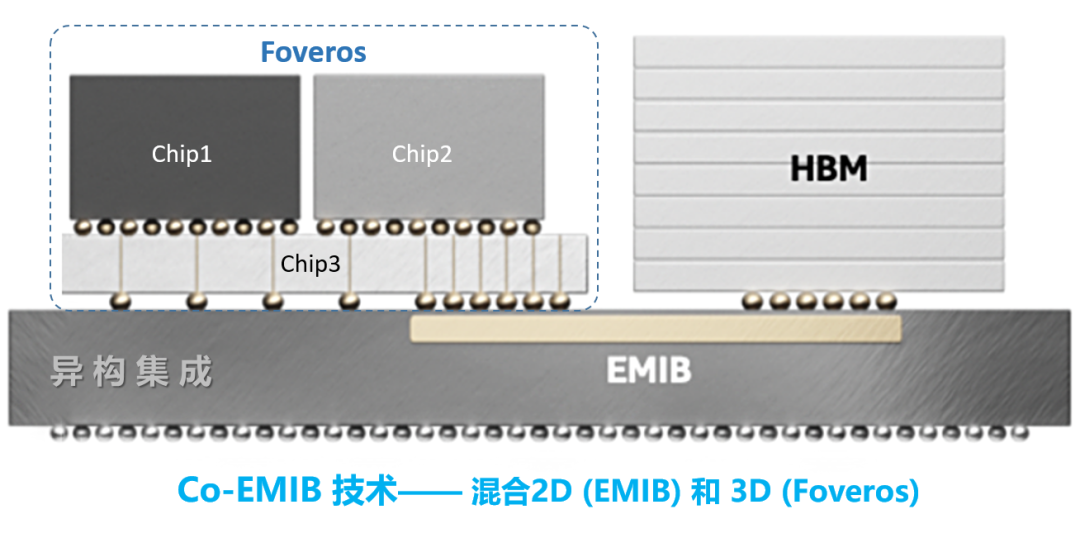

HeteroStructure Integration(異構集成)主要指將多個不同工藝節點單獨制造的芯片封裝到一個封裝內部,以增強功能性和提高性能,可以對采用不同工藝、不同功能、不同制造商制造的組件進行封裝。例如將不同廠商的10nm、28nm、45nm的小芯片通過異構集成技術封裝在一起。

這里主要以硅材質的芯片為主,工程師可以像搭積木一樣,在芯片庫里將不同工藝節點的Chiplet小芯片通過異構集成技術組裝在一起。

HeteroMaterial Integration

HeteroMaterial Integration(異質集成)是指將不同材料的半導體器件集成到一個封裝內,可產生尺寸小、經濟性好、靈活性高、系統性能更佳的產品。

如將Si、GaN、SiC、InP生產加工的芯片通過異質集成技術封裝到一起,形成不同材料的半導體在同一款封裝內協同工作的場景。

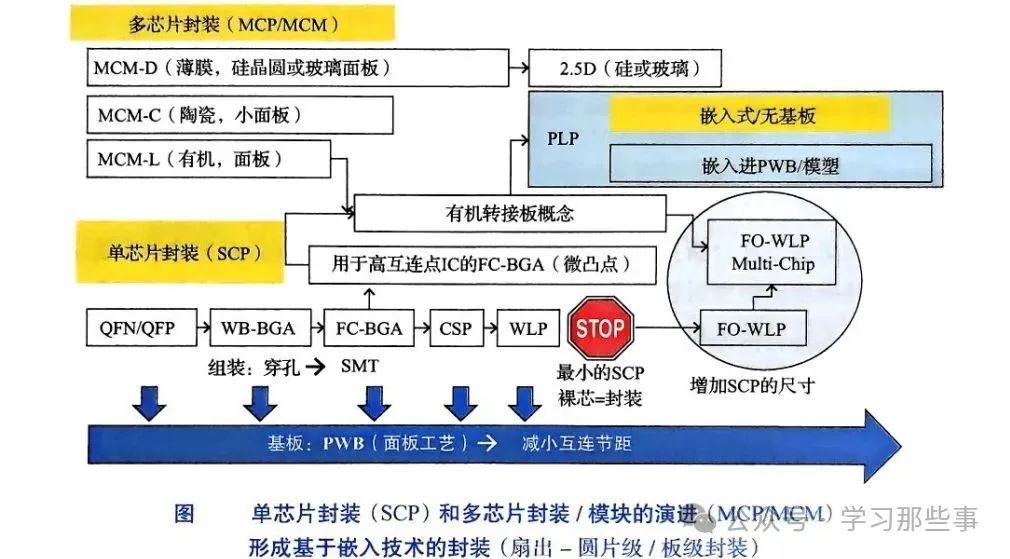

過去,出于功耗、性能、成本等因素的考慮,集成首先在單片上實施,例如SoC。近些年,由于摩爾定律日益趨緩,單片集成的發展受到了一些影響。得益于先進封裝與芯片堆疊技術的創新,設計人員可以將系統集成至單個封裝內形成SiP,這就推進了異構異質集成的發展。

下圖所示 Intel 的Co-EMIB技術就屬于典型的異構集成技術。

今天,Heterogeneous Integration 異構異質集成主要是指封裝層面(Package Level)的集成,其概念出現的歷史并不長,是在近十年間隨著先進封裝技術的興起而日益受到業界的重視,并逐漸發展為電子系統集成中最受關注的環節。

2)異 構計 算

異構計算(Heterogeneous Computing)

異構計算是指將CPU、GPU、FPGA、DSP等不同架構的運算單元整合到一起進行并行計算。

例如,CPU擅長管理和調度,比如讀取數據,管理文件,人機交互等;GPU管理弱,運算強,更適合整塊數據進行流處理的算法;FPGA實時性高,能管理能運算,但是開發周期長,復雜算法開發難度大;DSP適合特定算法的計算等。

當人工智能等海量計算訴求到來之后,GPU、FPGA、DSP去配合CPU進行計算的使命就自然而然的產生了,這就是異構計算。

異構計算技術從上世紀80年代中期產生,由于能有效獲取高計算能力、可擴展性好、資源利用率高、發展潛力大,已成為并行計算領域中的研究熱點。

近年來,人工智能持續爆發,對算力提出了更高的要求。異構計算作為大計算時代的解決方案,打破傳統通用計算的限制,融合不同指令集和體系架構的計算單元,完美支持大計算場景。

異構計算的實現架構通常是CPU+ GPU/FPGA/DSP,主要由CPU完成不可加速部分的計算以及整個系統的控制調度,由GPU/FPGA/DSP完成特定的任務和加速。

異構計算是一種特殊形式的并行和分布式計算,區別于CPU計算的通用架構,整合多種計算架構如CPU、GPU、FPGA、DSP、ASIC等,可簡單理解為:專人干專事,人多力量大。

3)算 力 算力(Computing Power)

算力,顧名思義就是計算能力。 算力原本是比特幣處理能力的度量單位,即為CPU計算哈希函數輸出的速度。現在已經成為一個描述計算能力的通用名詞。

算力存在于各種硬件設備中,沒有算力就沒有軟硬件的正常應用。高配置的電腦算力更高,可以運行復雜大型的軟件,低配置的電腦算力不夠,適合運行一般的辦公軟件。 算力受處理器的運行速度、存儲、網絡等因素的影響,而算力的核心在芯片。

算力為大數據和人工智能的發展提供基礎保障,算力是人工智能發展的動力和引擎。

算力、大數據、人工智能,三者已經有機結合成了一個智能化的整體。目前,算力的發展迫在眉睫,否則會束縛人工智能的發展。

4)異構集成、異構計算、算力的關系

The relationship between them

關于異構集成、異構計算、算力三者之間的關系,我想了想,畫了下面一張圖,大致可以來描述三者之間的關系。

異構集成主要在封裝層面,通過先進封裝技術將不同工藝節點、不同材質的芯片集成在一起,異構計算通過整合不同架構的運算單元來進行并行計算,二者的目的都是為了提升算力。

異構計算充分利用各種計算資源的并行和分布計算技術,能夠將不同制程和架構、不同指令集、不同功能的硬件進行組合,已經成為解決算力瓶頸的重要方式。

而要實現異構計算,異構集成和先進封裝技術在其中扮演了關鍵的角色。異構集成與先進封裝技術的進步使在單個封裝內構建復雜系統成為了可能,能夠快速達到異構計算系統內的芯片所需要的功耗、體積、性能的要求,是目前技術能夠實現的最佳解決方案。

異構集成和異構計算追求的目標是使計算任務的執行具有最短時間,也就是擁有最強的算力。

5)異 構 時 代

異構時代(Heterogeneous Era)

異構技術逐漸成為主流的時代,被業界稱為異構時代,這里的異構既包括異構計算也包括異構集成。

異構計算概念興起于上世紀80年代,其熱起來也是近十年間的事情,異構集成概念出現的時間不到十年,是隨著先進封裝技術的興起而逐漸為業界所認可。

異構計算和異構集成兩者的目的都為了提升算力。當今這個時代,異構逐漸成為一個熱門詞匯,因此被稱為異構時代。

異構集成、異構計算都因為時代而生,這個時代,就是異構時代。

總 結

這篇文章主要搞清楚了以下幾個問題:

1)異構集成全稱為異構異質集成,主要是指封裝層面的集成,其概念是在近十年間隨著先進封裝技術的興起而日益受到業界的重視。

2)異構計算是指將CPU、GPU、FPGA、DSP等不同架構的運算單元整合到一起進行并行計算,以提高算力。

3)算力就是計算、數據處理的能力。

4)異構集成、異構計算其主要目的都是為了提升系統的算力。

5)異構集成、異構計算都因為時代而生,這個時代,就是異構時代。

審核編輯:劉清

-

SiC

+關注

關注

32文章

3721瀏覽量

69397 -

芯片封裝

+關注

關注

13文章

614瀏覽量

32263 -

GaN

+關注

關注

21文章

2366瀏覽量

82304 -

異構計算

+關注

關注

2文章

112瀏覽量

17182 -

異構集成

+關注

關注

0文章

42瀏覽量

2292

原文標題:異構集成 與 異構計算

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

多Chiplet異構集成的先進互連技術

西門子Innovator3D IC異構集成平臺解決方案

全方位解析:什么是異構開發板?為什么選GM-3568JHF?

Chiplet與異構集成的先進基板技術

【TEC100TAI-KIT】青翼凌云科技基于JFMQL100TAI的全國產化智能異構計算平臺

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 異構架構下的智能邊緣計算標桿

基于板級封裝的異構集成詳解

異構計算解決方案(兼容不同硬件架構)

如何釋放異構計算的潛能?Imagination與Baya Systems的系統架構實踐啟示

能效提升3倍!異構計算架構讓AI跑得更快更省電

全志科技多核異構SoC助力行業智能化創新

RAKsmart智能算力架構:異構計算+低時延網絡驅動企業AI訓練范式升級

AI時代,封裝材料如何助力實現更優的異構集成?

最新議程出爐! | 2025異質異構集成封裝產業大會(HIPC 2025)

什么是異構集成?什么是異構計算?異構集成、異構計算的關系?

什么是異構集成?什么是異構計算?異構集成、異構計算的關系?

評論