華為技術(shù)有限公司最近增加了多項(xiàng)專利信息,其中之一是“半導(dǎo)體結(jié)構(gòu)及制造方法、三維存儲(chǔ)器、電子設(shè)備”,官方號(hào)碼為cn116940110a。

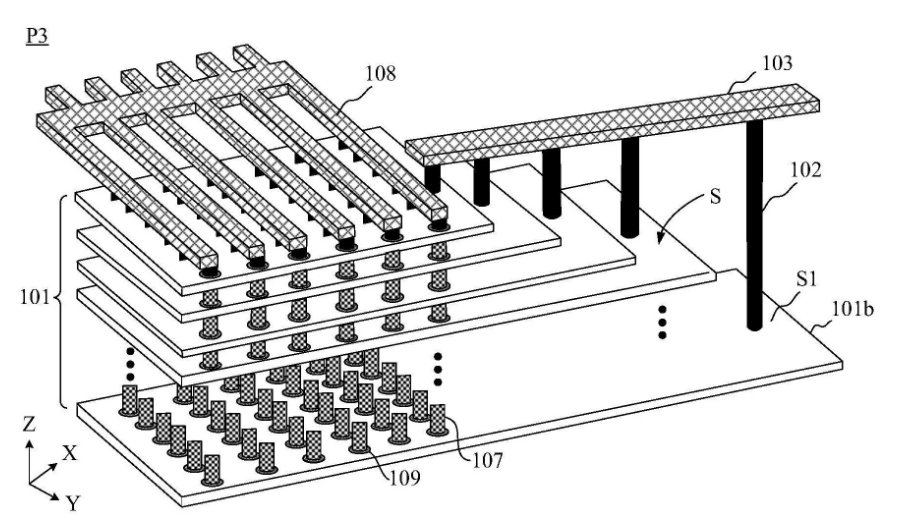

根據(jù)專利摘要,該申請(qǐng)涉及提高三維存儲(chǔ)器存儲(chǔ)密度的半導(dǎo)體芯片技術(shù)領(lǐng)域。這個(gè)半導(dǎo)體結(jié)構(gòu)的外部層沉積層、電容器、第一次接觸柱子及首家信號(hào)線組成,外圍堆疊層包括層疊設(shè)置的多個(gè)膜層對(duì),膜層對(duì)第一個(gè)防止介質(zhì)層和柵極層,包括各雙膜形成多個(gè)臺(tái)階。電容器包括第一電極和第二電極。第一個(gè)接觸柱位于第一個(gè)目標(biāo)階的上端,一邊與形成第一個(gè)目標(biāo)階的膜層的柵極層電連在一起,第一個(gè)目標(biāo)階是多個(gè)階中的臨界段。第一根信號(hào)線連接到第一根接觸柱的另一端,第一根信號(hào)線被安排在柵極層傳送第一電壓信號(hào),柵極層被安排成第一電極。上述半導(dǎo)體結(jié)構(gòu)應(yīng)用于三維存儲(chǔ)器,實(shí)現(xiàn)數(shù)據(jù)的讀寫操作。

華為表示,隨著內(nèi)存單元特征大小接近下限,平面技術(shù)和制造技術(shù)具有挑戰(zhàn)性,成本提高,從而使2d內(nèi)存的內(nèi)存密度接近上限。為了克服2d存儲(chǔ)器的局限性,業(yè)界開發(fā)了三維結(jié)構(gòu)的存儲(chǔ)器,為了提高存儲(chǔ)器密度,將膜層堆疊起來,縮小了零件的尺寸。

上述三維存儲(chǔ)器還包括周圍電路,周圍電路和存儲(chǔ)單位設(shè)置在三維存儲(chǔ)器的不同區(qū)域。外部電路中金屬-氧化物-金屬(metal - oxide - metal,減少mom)電容器,因此,包括mom電容器的區(qū)域面積,減少儲(chǔ)存裝置的區(qū)域面積增加三維記憶裝置的存儲(chǔ)密度提高的方法在銀領(lǐng)域正在成為亟待解決的問題。

-

電容器

+關(guān)注

關(guān)注

64文章

6958瀏覽量

107753 -

存儲(chǔ)器

+關(guān)注

關(guān)注

39文章

7739瀏覽量

171676 -

半導(dǎo)體芯片

+關(guān)注

關(guān)注

61文章

943瀏覽量

72635

發(fā)布評(píng)論請(qǐng)先 登錄

【案例5.1】存儲(chǔ)器選型的考慮要點(diǎn)

VTI低功耗SRAM存儲(chǔ)器VTI508HB08

什么是DRAM存儲(chǔ)芯片

紫光國(guó)芯:以三維堆疊存儲(chǔ)技術(shù)突破,筑牢算力時(shí)代“數(shù)據(jù)基石”

存儲(chǔ)漲價(jià)持續(xù)到 2027??jī)?yōu)可測(cè)揭秘存儲(chǔ)芯片的“品質(zhì)密碼”

雙口SRAM靜態(tài)隨機(jī)存儲(chǔ)器存儲(chǔ)原理

存儲(chǔ)芯片(煥發(fā)生機(jī))

意法半導(dǎo)體Page EEPROM打破數(shù)據(jù)存儲(chǔ)的玻璃天花板

芯源的片上存儲(chǔ)器介紹

簡(jiǎn)單認(rèn)識(shí)高帶寬存儲(chǔ)器

半導(dǎo)體存儲(chǔ)芯片核心解析

VirtualLab:光學(xué)系統(tǒng)的三維可視化

半導(dǎo)體存儲(chǔ)器測(cè)試圖形技術(shù)解析

華為公開半導(dǎo)體芯片專利:可提高三維存儲(chǔ)器的存儲(chǔ)密度

華為公開半導(dǎo)體芯片專利:可提高三維存儲(chǔ)器的存儲(chǔ)密度

評(píng)論