紅外探測器可將不可見的紅外輻射轉換為可測量的電信號。作為中波紅外探測的主流,銻化銦紅外探測器具有穩定的器件性能以及高可靠性,占據了大量的市場份額。作為探測器的核心,混成芯片的性能直接決定了紅外探測器的性能水平,這對器件制備工藝提出了很高的要求。銻化銦混成芯片封裝之前,需要通過背減薄工藝實現其量子效率最大化。

據麥姆斯咨詢報道,中國電子科技集團有限公司第十一研究所的科研團隊在《紅外》期刊上發表了以“大面陣銻化銦探測器芯片背減薄工藝技術開發”為主題的文章。該文章第一作者為李海燕高級工程師,主要從事銻化銦、超晶格紅外探測器方面的研究。

本文從背減薄工藝原理入手,針對大尺寸銻化銦紅外探測器混成芯片的特點,開發了單點金剛石車削與磨拋相結合的復合背減薄工藝。結果表明,減薄后的器件表面質量滿足工藝要求,雙晶衍射測試達標,封裝后成像質量良好。

背減薄工藝原理

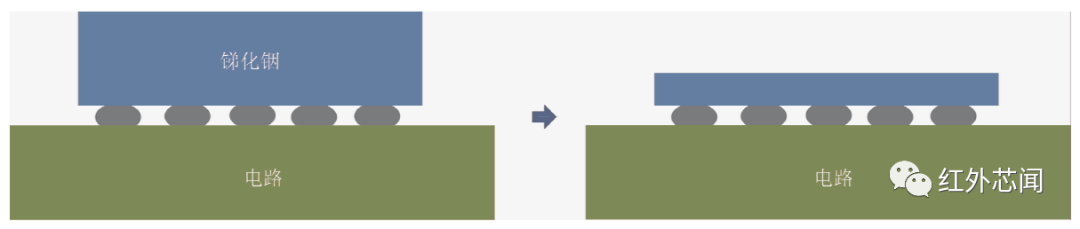

在混成芯片制備過程中,將光敏芯片與讀出電路芯片倒裝互連,采用背光照方式采集光信號。光照射光敏芯片,在其內部被轉換為電信號,然后通過讀出電路的讀出、轉換、放大、去噪等功能實現電信號處理與引出。為了實現量子效率的最大化,提高探測率,減小表面復合速率,使銻化銦體結構中產生的光生電荷得到最大效率的應用,其剩余厚度必須小于少子擴散長度,即30~35 μm。在工藝制備過程中,混成芯片采用背減薄工藝將銻化銦材料厚度從幾百微米減小到十幾微米,如圖1所示。背減薄質量指標(如粗糙度、劃痕、平整度、剩余厚度等)直接影響器件電學性能(如探測率和光響應均勻性),工藝設計直接決定了生產的產能能力、成品率和成本。考慮到銻化銦材料為脆性半導體材料,混成芯片自身存在應力形變,背減薄工藝開發難度極大(大尺寸銻化銦混成芯片尤甚)。

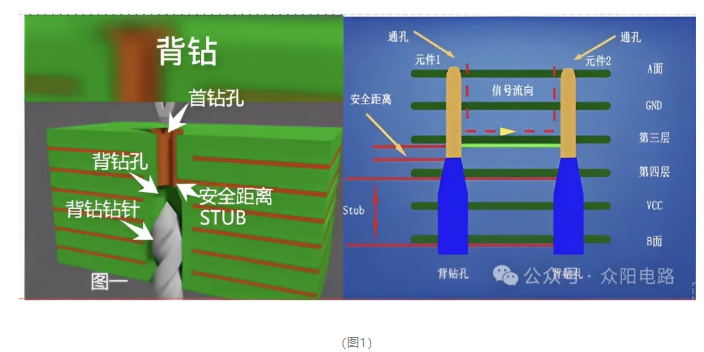

圖1 背減薄工藝示意圖

背減薄工藝選取

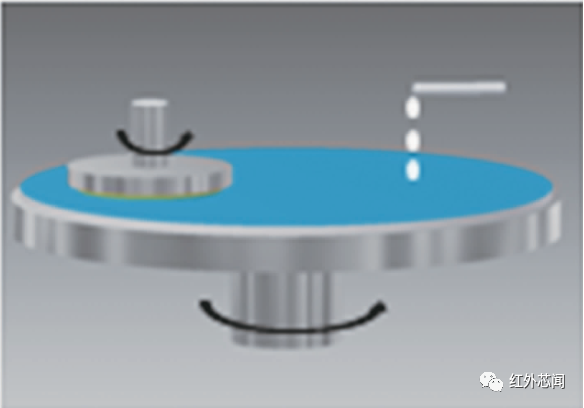

銻化銦背減薄工藝的技術水平主要從兩個方面來考察:一個是表面質量,主要涉及表面平整度、表面粗糙度、表面損傷和表面外觀質量(橘皮、劃痕、霧面)等;另一個是成品率,主要涉及裂紋、裂片、崩邊崩角等形貌問題。表面粗糙度不理想,表面損傷大,形成凹坑、橘皮形貌、相變、位錯等表面損傷時,會造成表面懸掛鍵密度和陷阱密度大。這將吸附雜質離子,形成陷阱中心以及高表面態密度,可能會增大暗電流,導致器件性能下降。目前,主流減薄工藝基于旋轉磨削原理實現器件減薄(見圖2):將混成芯片倒壓在磨拋盤上;在磨拋盤上加入磨拋液,施加一定的壓力,在磨拋盤、芯片、磨拋料的自轉及公轉效果下,通過材料與磨拋盤、磨拋液產生物理、化學反應,實現材料由粗磨到精拋的加工工藝過程;在此過程中,不斷實現材料減薄,同時不斷去除前一道磨拋的工藝損傷,逐步實現材料表面拋光;最終,通過化學拋光去除精拋損傷層,進一步提高表面質量。該方法作為銻化銦混成芯片背減薄工藝,已經極為成熟,操作簡單,被長期應用于芯片減薄工藝中。隨著超精密加工技術的進步,磨拋工藝可以實現納米級的加工質量。

圖2 磨拋工藝示意圖

旋轉磨削加工有很多優點,其不足在于加工過程中存在大量、長時間的砂輪磨粒機械作用。這不可避免地會在器件表面形成微裂紋等損傷,不僅易引入新的應力,而且易造成裂片。銻化銦材料硬度較低,在磨拋過程中壓力控制不當時極易出現裂紋、裂片情況。該問題在大尺寸混成芯片制備過程中尤為明顯,極大降低了器件成品率。

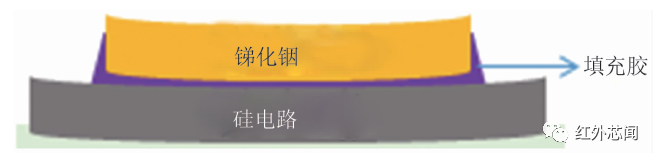

大尺寸銻化銦混成芯片由于自身存在應力,粘接在玻璃板上時會呈現四角翹曲、中心凹陷的形貌狀態,如圖3所示。在工藝開發中發現,若在混成芯片因自身應力而存在較大翹曲面型的情況下強行將其壓平磨拋,容易造成芯片裂片,因此需要開發新的工藝技術方案進行器件減薄。

圖3 混成芯片翹曲形態示意圖

本文討論1280×1024元(25 μm)大尺寸銻化銦混成芯片的背減薄工藝。芯片尺寸約為32 mm×26 mm。在大尺寸探測器上實現背減薄需要非常強的工藝控制能力:一方面要嚴格控制工藝損傷,避免在背減薄工藝中裂片,避免因減薄損傷而增加表面態、增大器件漏電流、降低器件性能;另一方面要實現低粗糙度光滑表面的制備。本文采用單點金剛石車削工藝配合磨拋工藝進行大尺寸銻化銦混成芯片的背減薄。

背減薄工藝過程

單點金剛石車削工藝通過機床控制單點金剛石刀具對材料進行車削。該技術已較為成熟,可實現微米級精度控制和微米級粗糙度加工。

器件表面的加工質量與刀具進給量、金剛石刀頭半徑、刀具磨損、機床的穩定性等多種因素相關。因此,無法通過調節刀具進給量等工藝參數無限制地優化表面質量。實際加工的材料表面的粗糙度要遠大于理論值。考慮到傳統的磨拋工藝已經非常成熟,在損傷及表面粗糙度的控制方面十分穩定,因此在本項目研發中,用單點車削工藝實現高成品率地去除銻化銦材料的大部分厚度,且對損傷控制、表面粗糙度方面的要求降低。通過傳統磨拋工藝進一步減薄和去除單點車削損傷,然后利用更進一步的精拋工藝實現器件對粗糙度的要求,最終實現銻化銦芯片的完全減薄。

車削工藝的操作如圖4所示。首先,將混成芯片粘接在玻璃基板上。測算減薄厚度后將芯片連同玻璃基板放置在車削機床上并加以固定。設置車削參數后進行車削。在車削機床上設置多級車削參數,使車削過程由粗加工向精細加工逐級進行。減薄初期,車削工藝設置以快速減薄厚度為主要目標。隨著芯片厚度下降,犧牲減薄速度以逐級降低切削損傷與切削粗糙度。圖5所示為車削之后的材料表面。可以看出,采用金剛石單點車削工藝進行器件減薄時,加工后的器件表面完整度良好,表面光亮。與傳統的磨拋減薄工藝相比,該工藝在減薄過程中減少了外來應力帶來的器件裂片風險,極大提高了成品率。

圖4 車削設備加工示意圖

圖5 減薄后器件表面的形貌圖

由于單點車削屬于大進給粗拋工藝,器件表面會形成一層損傷層。損傷層的存在會嚴重影響器件性能。因此,單點車削步驟完成后,需進行第二步芯片精拋,通過旋轉磨削工藝去除第一階段研磨造成的損傷。單點車削完成后,由于銻化銦厚度大幅減薄,應力及翹曲情況改善。此時將混成芯片倒扣在磨拋設備上,繼續減薄。裂片風險相比于原始混成芯片極大降低。本文采用的機械化學拋光法(CMP)具有簡單方便、成本低的優點。該方法大致分為三個步驟:首先進行粗磨,將材料進行較大厚度量的去除,同時去除單點車削損傷;其次進行粗拋,去除粗磨帶來的損傷并進一步減小銻化銦厚度;最后是精拋,主要去除粗拋損傷,同時進一步降低表面粗糙度。

結果與分析

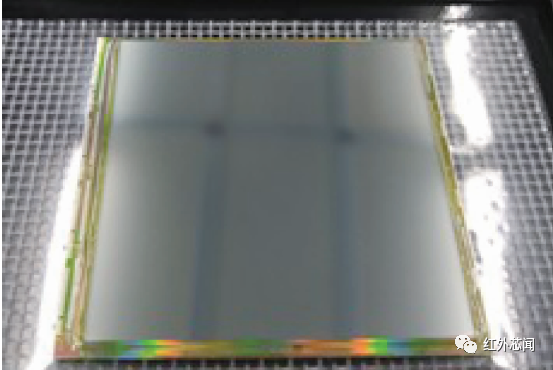

如圖5和圖6所示,減薄后的混成芯片表面光亮完整。通過顯微觀察沒有發現劃道、損傷、沾污等情況。采用雙晶衍射方法測試材料損傷。半峰寬值約為8.20~11.90 arcsec,基本達到測試極限,表明背減薄工藝后銻化銦晶片表面晶格的完整性很好。

圖6 器件局部效果圖

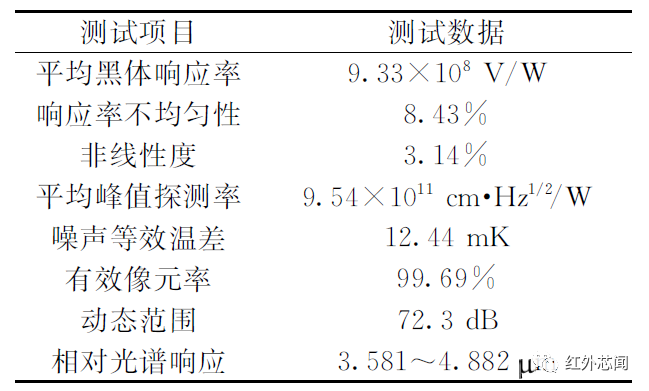

該工藝應用于1280×1024元(25 μm)大尺寸銻化銦混成芯片。芯片減薄增透后,將其封裝于微杜瓦結構中進行測試(結果見表1)。圖7為探測器組件的成像效果圖。可以看出,該組件具有良好性能。

表1 探測器組件的光電性能參數

圖7 探測器組件的成像效果圖

結束語

與傳統磨拋工藝相比,本文采用單點金剛石車削工藝實現混成芯片大部分厚度的減薄,然后通過磨拋工藝去除單點車削帶來的材料表面損傷。采用單點金剛石車削工藝的優勢在于減薄過程中減小了對混成芯片縱向上的壓力,同時隨著芯片厚度的不斷降低,不斷釋放芯片應力,大大減小了裂片率;采用傳統成熟的磨拋工藝去除損傷,在較低工藝難度下即可獲得滿足產品性能要求的混成芯片。該工藝技術尤其適用于大尺寸混成芯片的高質量減薄,對芯片的原始平整度要求低,有利于獲得高均勻性、高質量的混成芯片。

審核編輯:劉清

-

轉換器

+關注

關注

27文章

9419瀏覽量

156393 -

紅外探測器

+關注

關注

5文章

319瀏覽量

19034 -

CMP

+關注

關注

7文章

160瀏覽量

27763 -

電信號

+關注

關注

1文章

845瀏覽量

21844

原文標題:大面陣銻化銦探測器芯片背減薄工藝技術開發

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體“晶圓背部減薄(Back Grinding)”工藝技術的詳解;

半導體晶圓(Wafer)減薄&劃片工藝技術課件分享;

PCB工藝路線詳解:加成法 vs 減成法,一文讀懂核心差異與未來趨勢

PCB為啥現在行業越來越流行“淺背鉆”了?

n型背接觸BC電池:通過SiNx/SiON疊層優化減反射與表面鈍化性能

毫米之間定成敗:PCB背鉆深度設計與生產如何精準把控

研磨盤在哪些工藝中常用

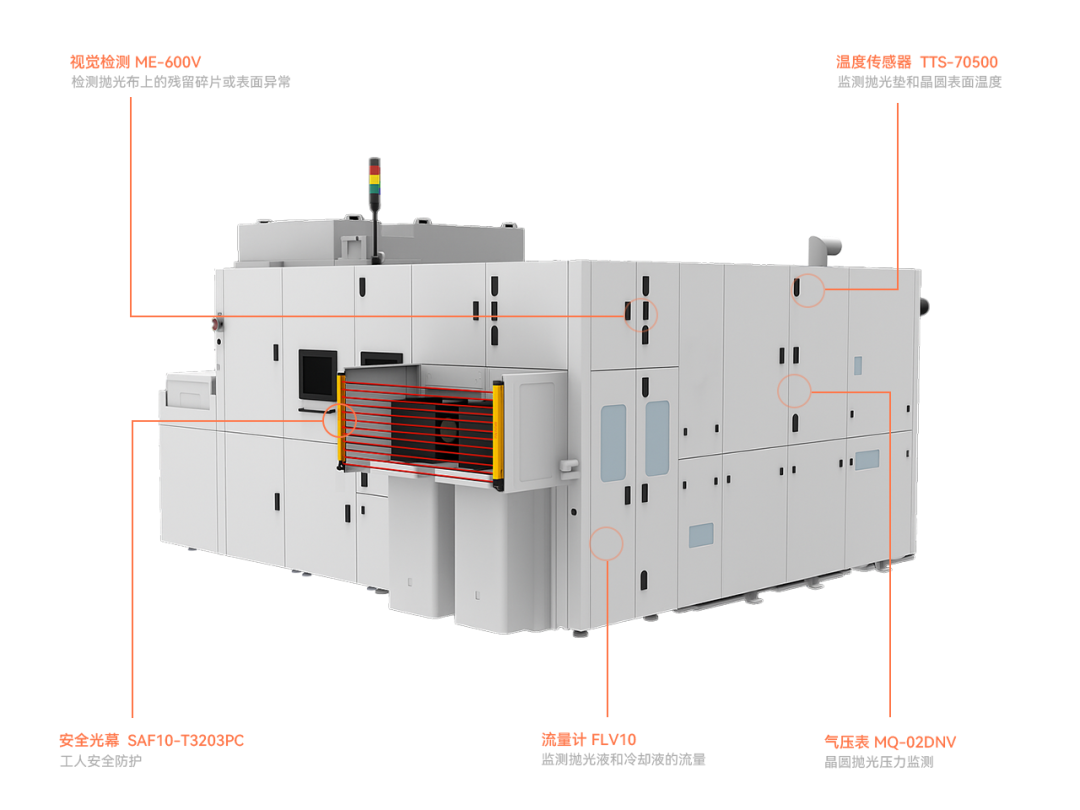

精密傳感技術驅動半導體未來:明治傳感器在CMP/量測/減薄機的應用

眾陽電路背鉆工藝技術簡介

晶圓減薄工藝分為哪幾步

簡單認識晶圓減薄技術

半導體封裝工藝流程的主要步驟

信號完整性的守護者:背鉆技術

背減薄工藝的原理是什么?背減薄工藝過程介紹

背減薄工藝的原理是什么?背減薄工藝過程介紹

評論