UHD-SDI RX Subsystem IP 核與 UHD-SDI TX Subsystem IP 核在編寫設計時具有多個設計示例可用,但所有這些設計示例均為直通設計的變體。如需了解有關這些設計的信息,請參閱(PG289)和(PG290)。

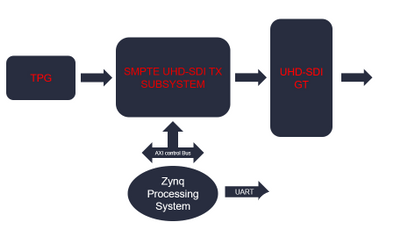

本篇博文將側重于概述如何以 ZCU106 開發板為目標,創建和運行僅限 TX 的設計。

注:此設計按現狀提供,不含任何保證。它是在正常發布/測試流程外構建的,僅用于提供指示信息。

SR 門戶不支持本設計。如果您對本設計有疑問,請在賽靈思視頻論壇板塊上發帖。

本設計演示了如何在 ZCU106 Rev 1.0 開發板上使用 Vivado 2019.2 工具集來構建和運行 SDI TX 系統。

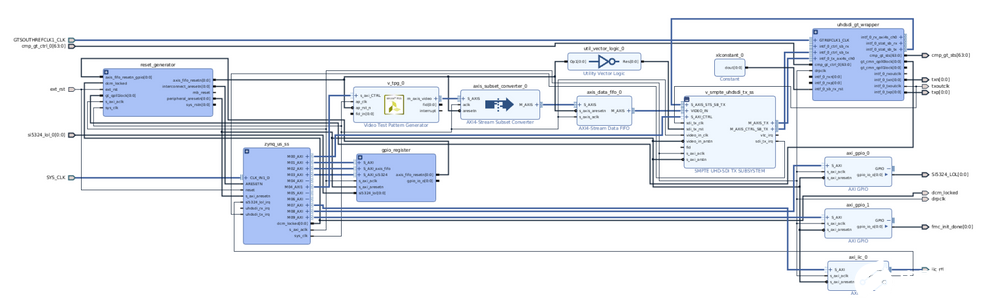

本設計是基于產品指南中發布的直通設計創建的,隨后經過更新以適用于僅限 TX 的設計。其目的是為了演示如何在僅限 TX 模式下快速實現 UHD-SDI TX 子系統和 UHD-SDI GT。

它包括下列組成部分:

復位功能

Zynq 子系統例化,用于控制 IP。

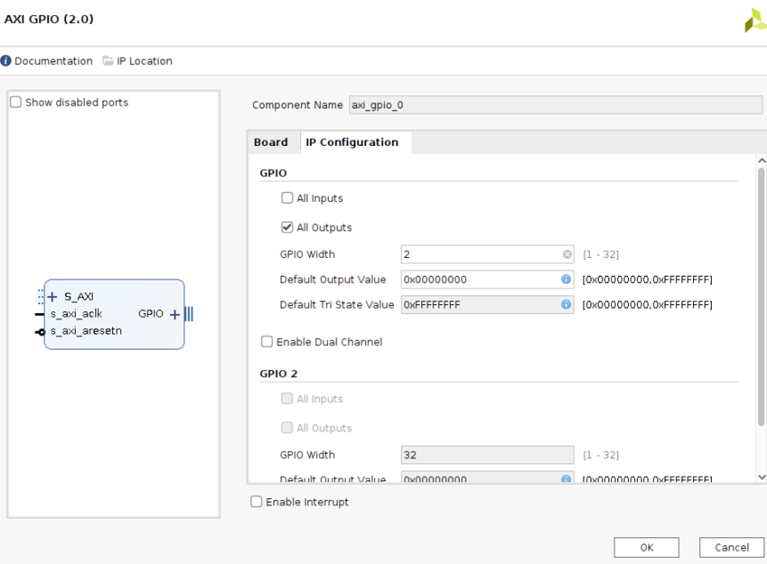

GPIO 用于監控狀態(來自原直通設計且保留不變)

TPG 用于創建視頻數據

子集轉換器,用于將 TPG 從 8 BPC 轉換為 10 BPC

FIFO(來自原直通設計)

UHD-SDI TX 子系統

UHD-SDI GT

已使用 Onmitek4K Ultra 對其進行了功能測試。

使用提供的腳本創建比特流

1. 在命令行或 Vivado 終端內,運行來自以下目錄的 Tcl 腳本:

Vivado-sourcev_smpte_uhdsdi_rx_ss_0_ex.tcl

2. 等待腳本完成,然后運行 Vivado 生成比特流。

此操作能以腳本模式完成,也可以打開 Vivado GUI 并遵循典型的綜合、實現、比特流生成流程來完成。

3. 生成比特流后,導出 XSA 文件。

如何基于 XSA 來創建 ELF 文件:

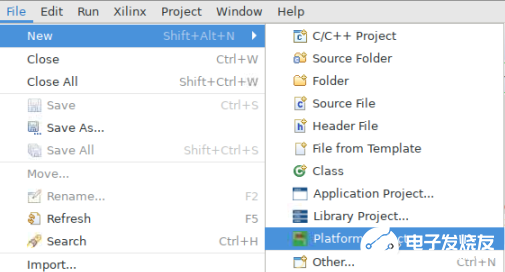

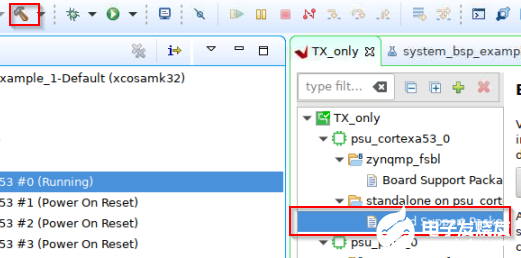

1. 打開 Vitis GUI。

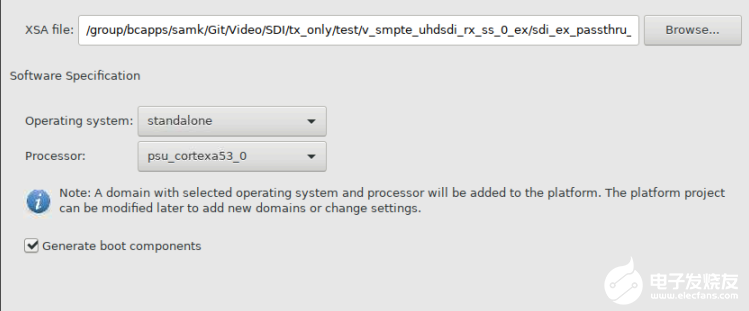

2. 創建新的平臺工程并指向從 Vivado 工程導出的 XSA。

3. 使用構建工具來構建 BSP。

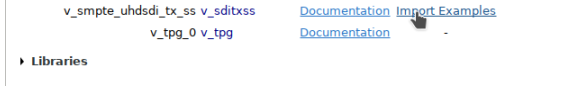

4. 構建好 BSP 后,選擇“Drivers”(驅動程序)中的“Import Examples”(導入示例)。

5. 導入 xsdi_example

6. 將 /src 文件 xsdb_* 替換為 /SW 內的文件。

這些文件已經過編輯,適用于僅限 TX 的硬件設計。

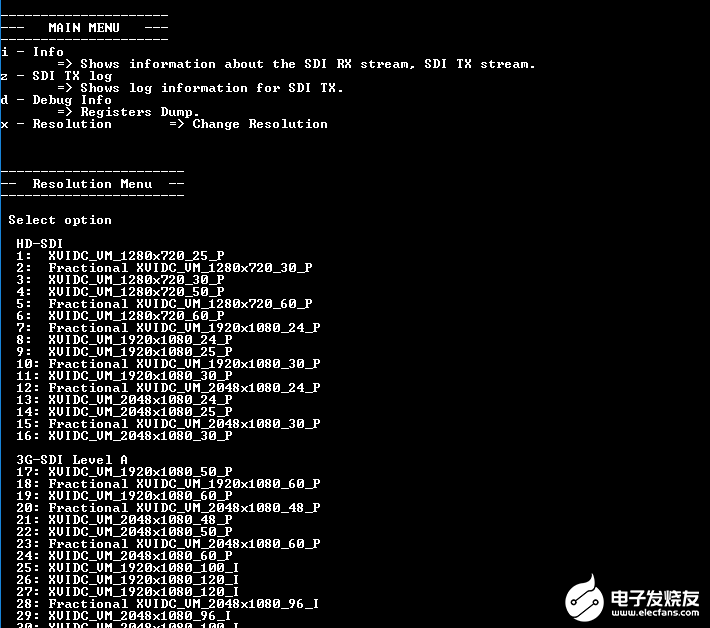

7. 構建并測試。下圖顯示了 UART 控制臺。

注:如需了解有關構建和測試的更多信息,請參閱(PG289)和(PG290)內記述的默認設計示例。

審核編輯:湯梓紅

-

開發板

+關注

關注

26文章

6340瀏覽量

119390 -

腳本

+關注

關注

1文章

410瀏覽量

29240 -

UHD

+關注

關注

7文章

54瀏覽量

75392 -

ZCU106

+關注

關注

0文章

28瀏覽量

1083

發布評論請先 登錄

NVMe高速傳輸之擺脫XDMA設計45:上板資源占用率分析

ZCU102,ZCU104和ZCU106有什么區別?

ZCU106 評估套件產品描述

ZCU106開發板的用戶指南免費下載

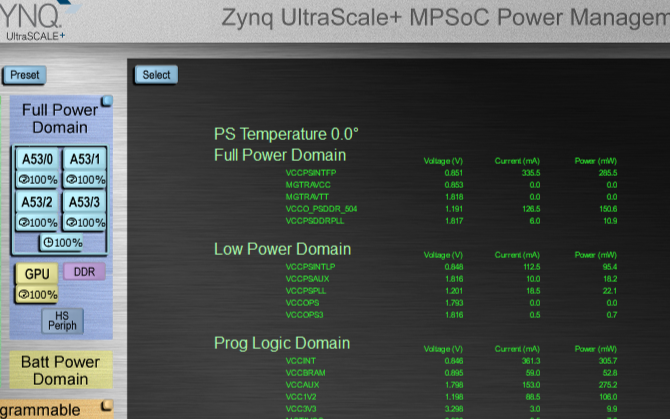

基于ZCU106單板的功耗優化

Xilinx提供在ZCU106單板上可以驗證的超低延時編解碼方案

在ZCU106單板上驗證Xilinx超低延時編解碼方案

如何在zcu106之間運行1588?

在MPSoC ZCU106單板的HDMI-Tx上基于eglfs_kms的運行QT應用程序

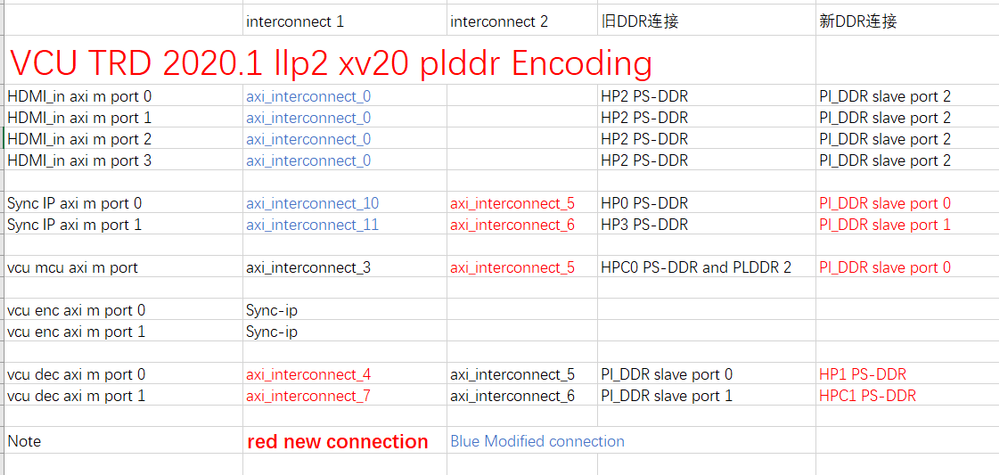

ZCU106在PLDDR實現超低延時編碼

ZCU106的超低延時gstreamer編解碼命令

使用ZCU102開發板運行xdpdma例程

Multi-Scaler IP的Linux示例以及Debug(上)

在ZCU106開發板上的僅限TX的設計內實現UHD-SDITX子系統

在ZCU106開發板上的僅限TX的設計內實現UHD-SDITX子系統

評論