Xilinx提供超低延時編解碼方案,在ZCU106單板上可以驗證。文檔MPSoC VCU TRD 2020.2 Low Latency XV20 提供了詳細命令。

缺省情況下,編碼使用的是PS DDR。如果PS DDR已經(jīng)被其它應(yīng)用占用,也可以讓編碼使用的PL DDR。在VCU TRD 2020.2的例子zcu106_llp2_xv20基礎(chǔ)上,做如下更改,可以實現(xiàn)使用PL DDR編碼。

01硬件連接

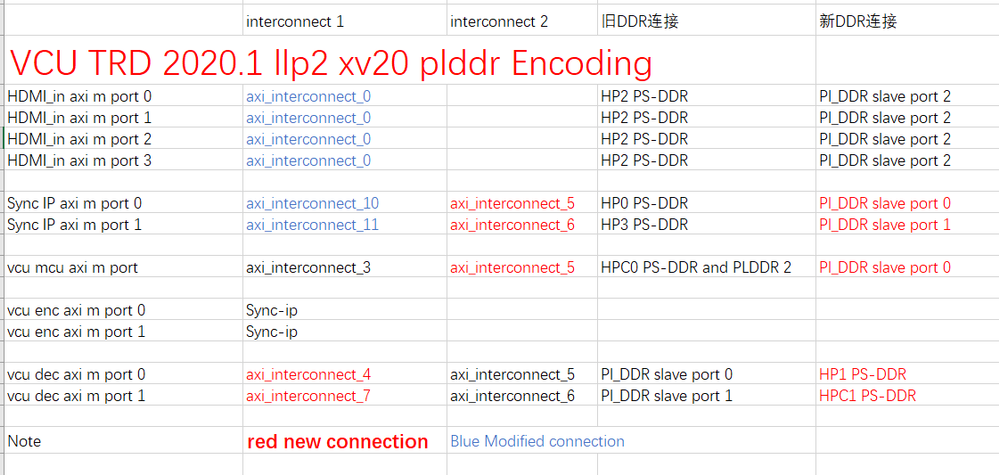

和編碼訪問的DDR相關(guān)的硬件連接有下列AXI Master端口。

1. HDMI_in axi_m port 0

2. HDMI_in axi_m port 1

3. HDMI_in axi_m port 2

4. HDMI_in axi_m port 3

5. Sync IP axi_m port 0

6. Sync IP axi_m port 1

7. vcu mcu axi_m port

8. vcu enc axi_m port 0

9. vcu enc axi_m port 1

其中vcu enc axi_m port 0和vcu enc axi_m port 1連接到了Sync IP;vcu mcu axi_m port已經(jīng)連接到了PS DDR和PL DDR。

對于剩下的axi_m port,都要連接到PL DDR。

下面是經(jīng)過驗證的修改。實際驗證表明,它支持PL DDR編碼。其中,藍色的連接,是做了修改的;紅色的連接,是新增的。

修改連接后,要檢查各個AXI Master的地址分配。

02軟件設(shè)置

在devicetree中,要保留內(nèi)存,并分配給VCU編碼模塊、HDMI輸入模塊使用。

/ {

reserved-memory {

#address-cells = 《0x2》;

#size-cells = 《0x2》;

ranges;

plmem_multimedia: pl_dma_mem_region {

compatible = “shared-dma-pool”;

no-map;

reg = 《0x48 0x0 0x0 0x70000000》;

};

};

};

&encoder {

memory-region = 《&plmem_multimedia》;

};

&amba_pl {

vcap_hdmi {

compatible = “xlnx,video”;

dma-names = “port0”;

dmas = 《&hdmi_input_v_frmbuf_wr_0 0》;

memory-region = 《&plmem_multimedia》;

vcap_hdmi_ports: ports {

#address-cells = 《1》;

#size-cells = 《0》;

vcap_hdmi_port: port@0 {

direction = “input”;

reg = 《0》;

vcap_hdmi_in: endpoint {

remote-endpoint = 《&vpss_scaler_out》;

};

};

};

};

};

&vcap_hdmi2 {

memory-region = 《&plmem_multimedia》;

};

&vcap_hdmi3 {

memory-region = 《&plmem_multimedia》;

};

&vcap_hdmi4 {

memory-region = 《&plmem_multimedia》;

};

原文標題:【工程師分享】ZCU106在PLDDR實現(xiàn)超低延時編碼

文章出處:【微信公眾號:FPGA開發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

Xilinx

+關(guān)注

關(guān)注

73文章

2200瀏覽量

131120

原文標題:【工程師分享】ZCU106在PLDDR實現(xiàn)超低延時編碼

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

TLV320AIC3254:超低壓立體聲音頻編解碼器的技術(shù)剖析與應(yīng)用指南

TLV320AIC3204 超低功耗立體聲音頻編解碼器:應(yīng)用與設(shè)計指南

TLV320AIC3253:超低功耗立體聲音頻編解碼器的卓越之選

TLV320AIC3206:超低功耗立體聲音頻編解碼器的卓越之選

TLV320AIC3256:超低功耗立體聲音頻編解碼器的卓越之選

TLV320AIC3212超低功耗立體聲音頻編解碼器:設(shè)計與應(yīng)用全解析

TLV320DAC3203:超低功耗立體聲音頻編解碼器的全方位解析

NVMe高速傳輸之擺脫XDMA設(shè)計45:上板資源占用率分析

NVMe高速傳輸之擺脫XDMA設(shè)計44:工程設(shè)計考量?

音視頻編解碼封裝解封裝部件介紹

NVMe高速傳輸之擺脫XDMA設(shè)計43:如何上板驗證?

視耀T1 MINI-4路4K編解碼器丨端到端超低延時賦能4K超清視界

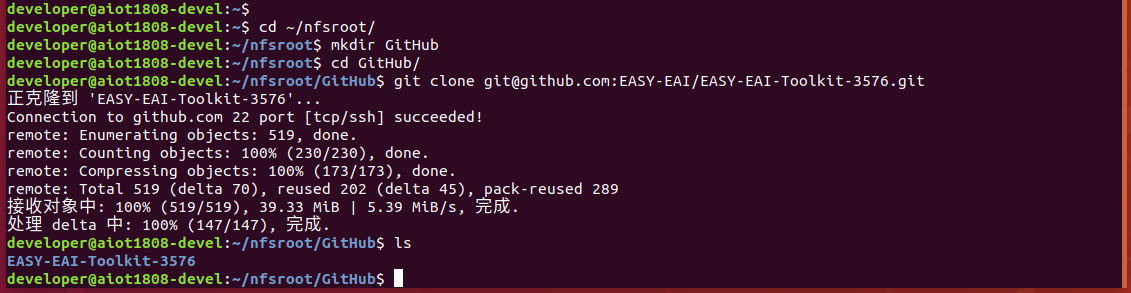

基于RK3576的BASE64編解碼

在ZCU106單板上驗證Xilinx超低延時編解碼方案

在ZCU106單板上驗證Xilinx超低延時編解碼方案

評論