與設計的其余部分相比,時序部分經(jīng)常被忽視

時鐘和振蕩器運行您的組件并確保一切都在系統(tǒng)地運行。盡管時序部件很常見且很重要,但與設計的其余部分相比,它們常常被忽視。在設計時鐘樹時,在選擇最佳時序解決方案時要考慮幾個因素。我們將根據(jù)您的應用程序的形式和功能,了解選擇時鐘的五個常見注意事項。

1. 是同步設計還是自由運行設計?

自由運行的應用程序需要獨立的時鐘,沒有任何特殊的鎖相或同步要求。示例包括標準處理器、內(nèi)存控制器、片上系統(tǒng) (SoC) 和外圍組件(例如 USB、PCI Express 開關)。

同步系統(tǒng)需要跨所有相關系統(tǒng)的連續(xù)通信和網(wǎng)絡級同步。在這些應用中,基于低帶寬鎖相環(huán) (PLL) 的時鐘提供抖動濾波以確保維持網(wǎng)絡級同步。例如,將所有序列化-反序列化 (SerDes) 參考時鐘與高精度網(wǎng)絡參考時鐘(例如 Stratum 3 或 GPS)同步可確保所有系統(tǒng)節(jié)點之間的同步。同步時鐘樹的示例包括光傳輸網(wǎng)絡 (OTN)、同步光網(wǎng)絡和同步數(shù)字體系 (SONET/SDH)、移動回程、同步以太網(wǎng)和高清串行數(shù)字接口 (HD SDI) 視頻傳輸。

考慮事項:您將使用的時鐘類型取決于時序架構是自由運行還是同步。如果架構是自由運行的,則應使用時鐘發(fā)生器。相反,同步設計需要抖動衰減時鐘。盡管同步系統(tǒng)不需要具有相同的頻率,但它們需要具有相同的相位。

2. 你需要什么時鐘頻率?

當需要多個參考頻率時,時鐘發(fā)生器和時鐘緩沖器很有用,并且目標 IC 都在同一塊電路板上,或者位于同一 IC 或現(xiàn)場可編程門陣列 (FPGA) 中。

時鐘發(fā)生器面臨的挑戰(zhàn)是系統(tǒng)布局。將晶體放置在其目標 IC 附近既簡單又便宜。另一方面,盡管能夠降低成本,但將時鐘信號從時鐘發(fā)生器路由到其目標 IC 可能具有挑戰(zhàn)性。實施仔細的設計和其他技術可以確保集中式時鐘源提供相同的性能。通常,如果需要四個或更多時鐘,設計人員可以通過使用時鐘發(fā)生器來節(jié)省資金。

考慮事項:在考慮時鐘發(fā)生器時,一定要選擇能夠輸出與您的設計兼容的頻率的發(fā)生器。Silicon Labs 的時鐘發(fā)生器可以使用其ClockBuilder Pro 軟件進行編程,以滿足特定的頻率、輸出和格式要求。客戶可以定制工廠編程的時鐘發(fā)生器樣品,通常需要兩周的交貨時間。

3.每個頻率需要多少個?

時鐘緩沖器分配輸入/參考時鐘的多個副本或簡單派生。

參考時鐘可以來自時鐘發(fā)生器、XO 或系統(tǒng)時鐘。時鐘緩沖器將其輸入時鐘從兩個輸出擴展到 10 個以上。它們可以包括 I 2 C、SPI 或引腳控制功能,例如信號電平和格式轉換、電壓電平轉換、多路復用和輸入分頻。這些功能通過消除組件、分壓器和信號電平轉換電路來節(jié)省空間和成本。

考慮事項:參考 Silicon Lab 的時序產(chǎn)品選擇器指南,選擇與您設計的輸出數(shù)量(或更多)、輸出格式和抖動要求相匹配的緩沖器。

4. 每個時鐘需要什么樣的抖動性能?

抖動性能在各種條件下各不相同,包括:

設備配置

操作頻率

信號格式

輸入時鐘轉換率和抖動

電源和電源噪聲

抖動定義為時域中與理想?yún)⒖紩r鐘的時間偏差,是時序組件的關鍵規(guī)格。如果不加以解決,過多的時鐘抖動會損害系統(tǒng)性能。對于 IC,抖動規(guī)格將作為時域測量給出,或者在高性能應用中更常見的是,作為 RMS 相位抖動中的頻域測量給出。

考慮事項:應估計總時鐘樹抖動,以確定在采用時鐘樹之前是否有足夠的系統(tǒng)級設計余量。如果抖動太高或指定不當,時鐘性能較差的組件可能會危及整個系統(tǒng)。重要的是要注意時鐘樹的抖動不僅僅是每個組件的 MAX 規(guī)格的總和;它是每個設備的 MAX RMS 抖動的平方和的根。

參考 Silicon Labs 的相位噪聲抖動計算器工具,輕松識別滿足抖動要求的時鐘和振蕩器。

5. 每個時鐘需要什么樣的信號格式級別?

時鐘和緩沖器有多種不同的格式,包括:

扇出:定義單個邏輯門的輸出可以饋送的最大數(shù)字輸入數(shù)的術語。大多數(shù)晶體管-晶體管邏輯 (TTL) 門最多可以為 10 個其他數(shù)字門或設備供電。因此,典型的 TTL 門的扇出值為 10。

低壓正發(fā)射極耦合邏輯 (LVPECL):正發(fā)射極耦合邏輯 (PECL) 的功率優(yōu)化版本使用 3.3V 正電源。

低壓差分信號 (LVDS):不僅是物理層規(guī)范,而且是通信標準和應用程序經(jīng)常添加的數(shù)據(jù)鏈路層。

電流模式邏輯 (CML):在標準電路板上以 312.5Mbit/s 和 3.125Gbit/s 之間的速度傳輸數(shù)據(jù)。

高速電流控制邏輯 (HCSL):具有兩個可在 0 和 14mA 之間切換的輸出引腳的差分邏輯。

低壓互補金屬氧化物半導體 (LVCMOS):LVCMOS的目標是縮小集成電路的器件幾何尺寸,從而降低工作電壓。

考慮事項:使用符合您的設計和相關要求的格式。上述每個時序部件都有許多不同的格式以支持各種設計類型。

Silicon Labs 時序解決方案

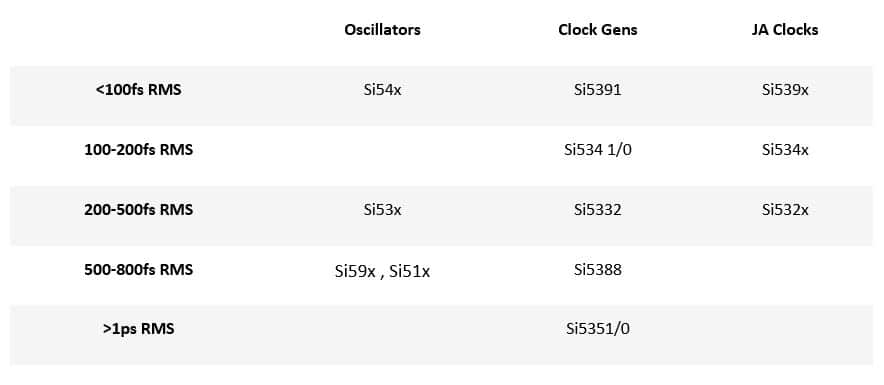

作為高性能時鐘和振蕩器的領導者,Silicon Labs 的計時解決方案提供業(yè)內(nèi)最廣泛的晶體振蕩器、時鐘發(fā)生器、時鐘緩沖器和抖動衰減器系列產(chǎn)品組合(圖 1)。此外,Silicon Labs 為時鐘提供最大的頻率靈活性以及業(yè)界最低的抖動。在購買時鐘之前,一定要問自己這里列出的五個問題,以幫助縮小支持您設計的最佳選擇范圍。

圖 1:Silicon Labs 計時解決方案組合結合了頻率靈活性和一流的抖動性能。(來源:對稱電子)

審核編輯hhy

-

時鐘樹

+關注

關注

0文章

58瀏覽量

11279

發(fā)布評論請先 登錄

AD9522-5:高性能時鐘發(fā)生器的設計與應用

高速時鐘設計利器:AD9520 - 5全方位剖析

AD9516 - 5 14 輸出時鐘發(fā)生器:高精度時鐘解決方案

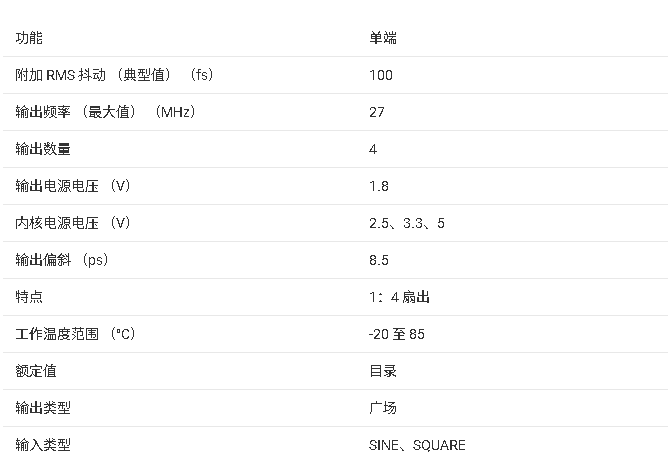

LMH2190:一款高性能四通道時鐘樹驅動器的深度剖析

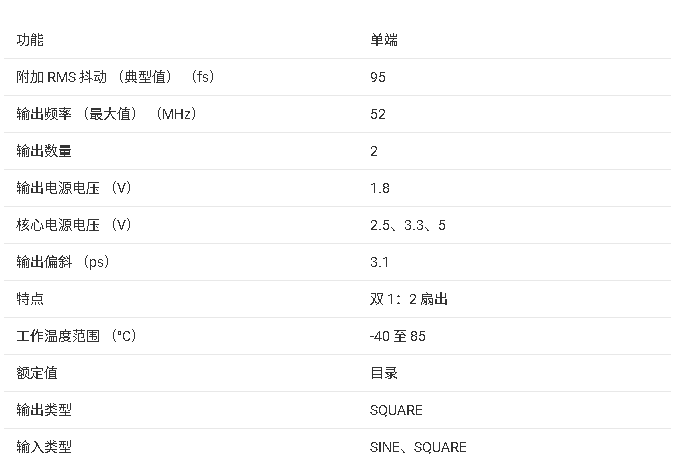

探索LMH2191:52 MHz時鐘樹驅動的卓越之選

時鐘緩沖器技術選型與設計要點

時鐘樹解析

E203工程源碼時鐘樹解析

時鐘設計優(yōu)化實戰(zhàn)

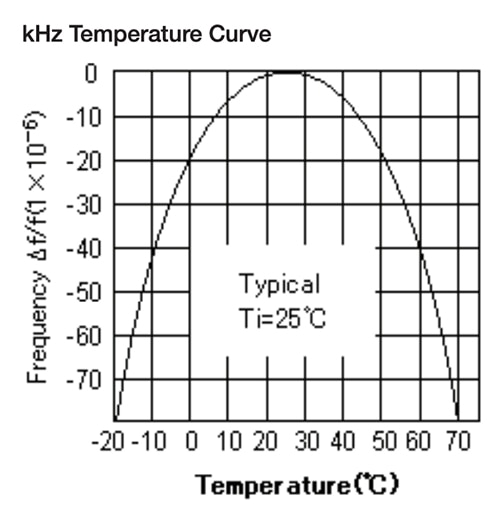

kHz 晶體選型設計師指南

?LMH2191 雙通道52MHz時鐘樹驅動器技術文檔總結

時鐘樹設計師的 5 個問題

時鐘樹設計師的 5 個問題

評論