探索LMH2191:52 MHz時鐘樹驅動的卓越之選

在電子設計領域,時鐘信號的穩定與精確對于設備的性能至關重要。今天,我們就來深入了解一款出色的時鐘樹驅動芯片——Texas Instruments的LMH2191,看看它如何為我們的設計帶來便利與優勢。

文件下載:lmh2191.pdf

一、LMH2191概述

LMH2191是一款雙通道時鐘樹驅動芯片,專為移動手機外設(如藍牙、無線局域網和數字視頻廣播 - H等)提供通用時鐘。它能有效解決扇出驅動能力有限或長走線等時鐘問題,保護主時鐘免受負載變化和頻率牽引影響,隔離噪聲模塊和串擾。其超低相位噪聲特性使其能夠驅動像無線局域網和藍牙這類對時鐘信號敏感的模塊。

二、芯片特性亮點

2.1 獨特的時鐘輸出設計

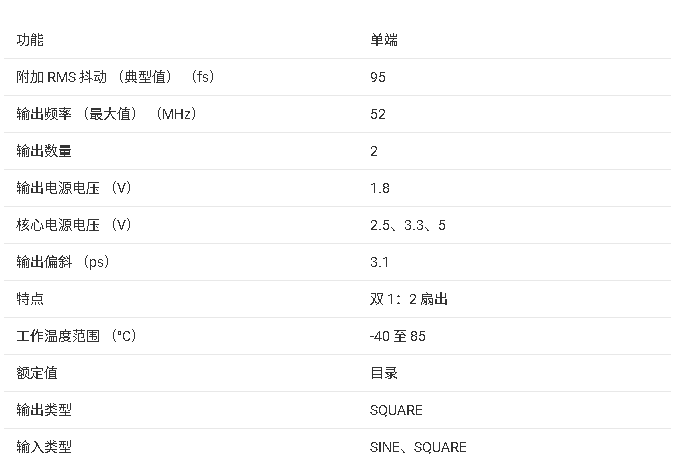

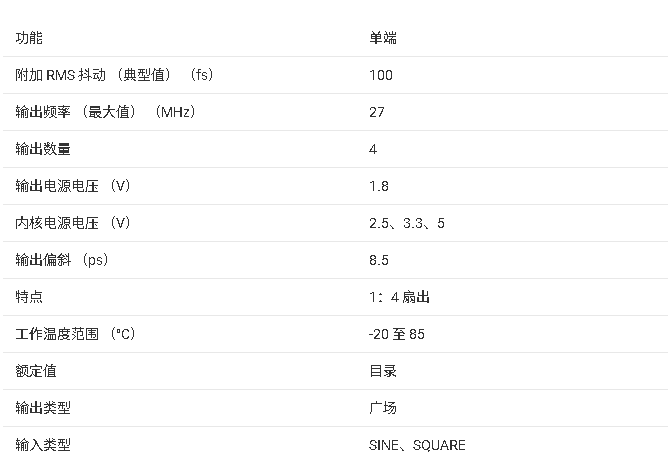

- 一路輸入兩路輸出:僅需一個輸入時鐘,就能產生兩個輸出時鐘,方便為多個外設提供時鐘信號。

- 1.8V方波時鐘輸出:輸出標準的1.8V方波時鐘,滿足大多數外設的時鐘需求。

- 反相時鐘輸出:CLK2輸出反相,有助于進一步降低電磁干擾(EMI)。

- 獨立時鐘請求:每個時鐘輸出都有獨立的時鐘請求引腳,允許外設自主控制時鐘的啟用,實現靈活的時鐘管理。

2.2 出色的隔離與低噪聲性能

- 高電源噪聲隔離:對電源噪聲有很高的隔離能力,確保時鐘輸入不受電源波動的影響。

- 高輸出間隔離:時鐘輸出之間的高隔離度,保證了各外設之間不會相互干擾。

- 集成低噪聲LDO:集成了1.8V低壓差穩壓器(LDO),輸出噪聲電壓低,能夠提供10 mA的負載電流,為TCXO或其他時鐘源供電。

2.3 其他特性優勢

- EMI濾波:具備EMI濾波功能,降低電磁干擾,提高系統的電磁兼容性。

- 超低待機電流:在待機模式下消耗的電流極低,有助于延長電池續航時間。

- 寬電源電壓范圍:VBAT范圍為2.5V至5.5V,適應多種電源供電場景。

- 小巧封裝:采用8 - 凸塊DSBGA封裝,尺寸僅為1.61 mm x 1.063 mm,適合便攜式應用。

三、電氣性能剖析

3.1 供電與工作條件

- 絕對最大額定值:供電電壓(VBAT - VSS)范圍為 - 0.3V至6V,不同端口的電壓、ESD耐受、輸出短路持續時間等都有明確的限制,使用時需嚴格遵守,防止芯片損壞。

- 工作額定值:供電電壓(VBAT - VSS)在2.5V至5.5V之間,輸入時鐘頻率范圍為10 MHz至52 MHz,輸入時鐘占空比為45%至55%,工作溫度范圍為 - 40°C至 + 85°C。

3.2 關鍵電氣參數

- 供電電流:在不同的輸入時鐘頻率和負載電容下,供電電流會有所變化。例如,當SCLK_IN = 19.2 MHz,兩個時鐘輸出都翻轉,負載電容為0pF時,供電電流典型值為1.65 mA;當負載電容為33.5pF時,供電電流典型值為4.45 mA。在關機模式下,輸入時鐘不活動或翻轉時,電流僅為0.1至1 μA。

- 時鐘輸出參數:包括傳播延遲、輸出間偏斜、上升時間、下降時間、輸出時鐘占空比和抖動等。例如,傳播延遲(低到高或高到低)在負載電容為33 pF時,典型值為6.1 ns,最大值為10.5 ns;輸出間偏斜典型值為1.5 ns,最大值為3.1 ns。

- LDO參數:輸出電壓在負載電流為1 mA時,典型值為1.8V,范圍為1.73V至1.88V;負載電流最大可達10 mA;壓差電壓在輸出電流為10 mA,輸出電壓為1.7V時,典型值為125 mV。

四、內部結構與工作原理

4.1 時鐘樹驅動

- 輸入部分:源時鐘輸入(SCLK_IN)通過內部連接的33pF耦合電容進行直流偏置,防止外部直流電壓影響內部偏置電路。由于耦合電容的存在,最小時鐘頻率為10 MHz。該電路能夠根據輸入信號的邊緣調整開關點,使輸出時鐘的占空比接近50%,滿足外設對占空比的要求。輸入阻抗由直流輸入電阻和交流輸入阻抗組成,交流輸入阻抗受輸入信號幅度影響。

- 輸出部分:每個輸出能夠驅動高達50 pF的容性負載,同時將電磁干擾降至最低。CLK2輸出反相進一步減少了EMI。

4.2 時鐘請求邏輯

每個時鐘輸出都有獨立的時鐘請求輸入,允許外設控制時鐘的啟用。時鐘請求信號連接到鎖存器的D輸入,同步控制時鐘輸出驅動器的開關,防止時鐘輸出出現毛刺。當兩個請求輸入都為低電平時,LDO輸出電壓將被禁用。

4.3 低壓差穩壓器(LDO)

LDO用于調節輸入電壓VBAT,為TCXO和內部時鐘路徑提供穩定的1.8V超低噪聲電源。它能夠抑制電源電壓紋波和噪聲,減少時鐘信號的相位噪聲。LDO在時鐘請求激活時上電,支持過熱檢測,過熱時會自動關閉。推薦的上電順序是在電源已上電的情況下將時鐘請求拉高,使LDO在需要輸出時鐘時才上電,降低功耗。

五、應用與布局建議

5.1 典型應用

LMH2191常用于為移動手機外設提供時鐘,如藍牙、無線局域網和數字視頻廣播 - H等。其高隔離度和低相位噪聲特性確保了各外設之間不會相互干擾,時鐘質量不受影響。

5.2 布局建議

- 布線:SCLK_IN輸入走線和CLK1、CLK2輸出走線應盡可能短,以減少時鐘輸出的額外容性負載。

- 去耦:在器件附近進行適當的去耦,推薦使用低ESR的表面貼裝陶瓷電容(MLCC),如CBAT為1 μF,COUT為2.2 μF。

六、總結

LMH2191以其豐富的特性、出色的電氣性能和小巧的封裝,成為移動設備和便攜式設備時鐘設計的理想選擇。它不僅能夠解決時鐘驅動和隔離問題,還能有效降低功耗和電磁干擾。在實際應用中,我們需要根據具體需求合理選擇工作條件和參數,同時注意布局布線,以充分發揮其性能優勢。大家在使用LMH2191的過程中,有沒有遇到過什么有趣的問題或者獨特的應用場景呢?歡迎在評論區分享交流。

-

移動設備

+關注

關注

0文章

528瀏覽量

55942

發布評論請先 登錄

探索LMH2191:52 MHz時鐘樹驅動的卓越之選

探索LMH2191:52 MHz時鐘樹驅動的卓越之選

評論