高速時鐘設計利器:AD9520 - 5 全方位剖析

在高速電子系統(tǒng)設計中,時鐘信號的精準與穩(wěn)定是系統(tǒng)性能的基石。為大家深入介紹一款高性能時鐘發(fā)生器——AD9520 - 5,它在提供低抖動、低相位噪聲的多輸出時鐘信號方面表現(xiàn)卓越,適用于眾多對時鐘精度要求極高的應用場景。

文件下載:AD9520-5.pdf

芯片特性:精益求精,滿足多樣需求

- 低相噪 PLL:集成的低相位噪聲鎖相環(huán)(PLL)能搭配高達 2.4 GHz 的外部 3.3 V/5 V VCO/VCXO,可選擇 3 種參考輸入方式,接受 16.62 MHz 至 33.3 MHz 晶體作為參考輸入,還具備可選的參考時鐘倍頻器和參考監(jiān)測能力。在自動和手動參考保持與切換模式下,能實現(xiàn)無毛刺切換和自動恢復。同時提供數(shù)字或模擬鎖定檢測,支持可選的零延遲操作。

- 豐富輸出配置:擁有 12 個 1.6 GHz LVPECL 輸出,分為 4 組,每組 3 個輸出共享一個帶相位延遲的 1 至 32 分頻器,附加輸出抖動低至 225 fs rms,通道間偏移小于 16 ps。每個 LVPECL 輸出還能在頻率不超過 250 MHz 時配置為 2 個 CMOS 輸出,且支持所有輸出在上電時自動同步和手動同步。

- 靈活的控制接口:配備與 SPI 和 (I^2C) 兼容的串行控制端口,方便與各種微控制器和微處理器接口,同時采用 64 引腳 LFCSP 封裝,內(nèi)置非易失性 EEPROM 可存儲配置設置,便于系統(tǒng)上電和復位時快速恢復預設狀態(tài)。

工作原理:精準調(diào)控,穩(wěn)定輸出

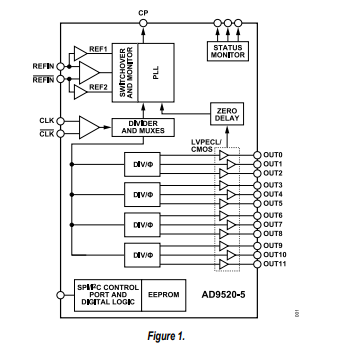

AD9520 - 5 的工作原理圍繞其核心的鎖相環(huán)和時鐘分配機制展開。

- 鎖相環(huán)(PLL):PLL 利用外部 VCO 或 VCXO 構(gòu)建完整的鎖相回路,通過外部環(huán)路濾波器確定環(huán)路帶寬和穩(wěn)定性。配置時需對 R 分頻器、N 分頻器、PFD 極性和電荷泵電流等參數(shù)進行編程設置,這些設置共同決定了 PLL 環(huán)路帶寬。

- 相位頻率檢測器(PFD):接收 R 分頻器和 N 分頻器的輸入,輸出與它們的相位和頻率差成正比的信號。可編程的反沖脈沖寬度設置可確保 PFD 無死區(qū),減少相位噪聲和參考雜散。

- 電荷泵(CP):由 PFD 控制,根據(jù) PFD 輸入的相位和頻率關(guān)系,對積分節(jié)點進行充電或放電,將積分和濾波后的電流轉(zhuǎn)換為電壓,驅(qū)動外部 VCO 的調(diào)諧節(jié)點,實現(xiàn) VCO 頻率的調(diào)整。

- 參考輸入:提供靈活的參考輸入方式,包括全差分輸入、兩個獨立的單端輸入和 16.67 MHz 至 33.33 MHz 晶體振蕩器輸入,并可選擇參考時鐘倍頻器。

- 時鐘分配:芯片的時鐘分配由四個時鐘通道組成,每個通道有獨立的可編程分頻器,可對輸入時鐘進行 1 至 32 的整數(shù)分頻。VCO 分頻器可對 CLK 輸入進行 1 至 6 的分頻,以滿足不同的頻率需求。通道分頻器還支持可選的占空比設置、占空比校正功能和粗相位偏移設置,能靈活調(diào)整輸出時鐘的特性。

應用場景:廣泛應用,彰顯實力

- 通信領(lǐng)域:在 SONET、10Ge、10GFC、同步以太網(wǎng)和 OTU2/3/4 等高速通信系統(tǒng)中,為數(shù)據(jù)傳輸和處理提供低抖動、低相位噪聲的時鐘信號,保障數(shù)據(jù)的準確傳輸和處理。

- 測試測量:ATE 和高性能儀器設備對時鐘信號的精度和穩(wěn)定性要求極高,AD9520 - 5 可滿足這些設備對時鐘信號的嚴格要求,確保測量結(jié)果的準確性和可靠性。

- 無線通信:在高性能無線收發(fā)器中,為射頻前端和基帶處理提供精確的時鐘信號,提高通信系統(tǒng)的性能和穩(wěn)定性。

- 數(shù)據(jù)采集:在高速 ADC 和 DAC 中,其低抖動時鐘信號能顯著提高采樣精度和動態(tài)范圍,減少噪聲和失真對數(shù)據(jù)采集的影響。

實際設計要點:細節(jié)把控,優(yōu)化性能

在使用 AD9520 - 5 進行設計時,需關(guān)注以下要點以確保其性能充分發(fā)揮。

- 電源設計:為保證芯片穩(wěn)定運行,需注意不同電源引腳的電壓要求和紋波控制。VS 和 VS_DRV 電源引腳需提供穩(wěn)定的電壓,VCP 電源引腳需根據(jù)芯片工作狀態(tài)提供合適的電壓范圍。同時,使用合適的去耦電容和電源濾波電路,減少電源噪聲對芯片性能的影響。

- 環(huán)路濾波器設計:PLL 的環(huán)路濾波器對系統(tǒng)的穩(wěn)定性和性能至關(guān)重要。需根據(jù) VCO 頻率、KVCO、PFD 頻率、CP 電流和所需的環(huán)路帶寬等參數(shù)精心設計濾波器的組件值。可借助 ADIsimCLK 等工具進行設計和優(yōu)化。

- 時鐘輸出配置:根據(jù)具體應用需求,合理配置時鐘輸出的類型、頻率和占空比等參數(shù)。在使用 LVPECL 輸出時,需注意其直流偏置和終端匹配問題;使用 CMOS 輸出時,需注意負載電容和信號完整性問題。

總結(jié)

AD9520 - 5 作為一款高性能的時鐘發(fā)生器,憑借其低相位噪聲、豐富的輸出配置、靈活的控制接口和廣泛的應用場景,成為電子工程師在高速時鐘設計中的得力助手。在實際設計中,只要我們深入理解其工作原理,注意關(guān)鍵設計要點,就能充分發(fā)揮其優(yōu)勢,為各類電子系統(tǒng)提供穩(wěn)定、精準的時鐘信號。大家在使用 AD9520 - 5 過程中有什么特別的經(jīng)驗或者遇到的問題,歡迎在評論區(qū)交流分享。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

時鐘發(fā)生器

+關(guān)注

關(guān)注

1文章

349瀏覽量

70106

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

ADF4030:高精度時鐘同步利器的深度剖析

ADF4030:高精度時鐘同步利器的深度剖析 在當今的電子系統(tǒng)設計中,高精度時鐘同步是許多應用的關(guān)鍵需求,尤其在5G通信、相控陣雷達和自動測

AD9520-4:高性能時鐘發(fā)生器的深度解析與應用指南

AD9520-4:高性能時鐘發(fā)生器的深度解析與應用指南 引言 在電子設計領(lǐng)域,時鐘發(fā)生器的性能對整個系統(tǒng)的穩(wěn)定性和可靠性起著至關(guān)重要的作用。AD9520 - 4作為一款12 LVPEC

AD9520 - 2:高性能時鐘發(fā)生器的深度剖析

AD9520 - 2:高性能時鐘發(fā)生器的深度剖析 在電子設計領(lǐng)域,時鐘發(fā)生器是確保系統(tǒng)穩(wěn)定運行的關(guān)鍵組件之一。今天,我們將深入探討AD9520

AD9520-1:高性能時鐘發(fā)生器的全方位解析

AD9520-1:高性能時鐘發(fā)生器的全方位解析 在電子電路設計領(lǐng)域,時鐘發(fā)生器是至關(guān)重要的組件,它為系統(tǒng)提供穩(wěn)定、精確的時鐘信號,保障系統(tǒng)的

AD9520-0:高性能時鐘發(fā)生器的深度解析與應用指南

AD9520-0:高性能時鐘發(fā)生器的深度解析與應用指南 在電子設計領(lǐng)域,時鐘發(fā)生器是確保系統(tǒng)穩(wěn)定運行的關(guān)鍵組件。AD9520-0作為一款12 LVPECL/24 CMOS輸出的

汽車電源設計利器:MAX15004/MAX15005控制器深度剖析

汽車電源設計利器:MAX15004/MAX15005控制器深度剖析 在汽車電子領(lǐng)域,電源設計一直是一個關(guān)鍵且具有挑戰(zhàn)性的任務。汽車環(huán)境復雜,對電源的穩(wěn)定性、可靠性和效率要求極高。今天,我們就來

LTM4602 6A高效DC/DC μModule:設計利器深度剖析

LTM4602 6A高效DC/DC μModule:設計利器深度剖析 在電子設備日新月異的今天,電源模塊的性能直接影響著整個系統(tǒng)的穩(wěn)定性和效率。Linear Technology

74LVC08 四 2 輸入與門:設計利器深度剖析

74LVC08 四 2 輸入與門:設計利器深度剖析 在數(shù)字電路設計領(lǐng)域,邏輯門是構(gòu)建復雜系統(tǒng)的基礎(chǔ)組件,其中 74LVC08 四 2 輸入與門以其出色的性能和廣泛的適用性,成為電子工程師們的常用之選

CDCE925與CDCEL925:靈活低功耗LVCMOS時鐘發(fā)生器的設計利器

CDCE925與CDCEL925:靈活低功耗LVCMOS時鐘發(fā)生器的設計利器 一、引言 在電子系統(tǒng)設計中,時鐘信號猶如系統(tǒng)的心跳,穩(wěn)定而精確的時鐘對于各種設備的正常運行至關(guān)重要。CDC

高速單P溝道MOSFET驅(qū)動器LTC1693 - 5:設計利器

高速單P溝道MOSFET驅(qū)動器LTC1693 - 5:設計利器 在電子工程師的日常設計工作中,MOSFET驅(qū)動器是一個常見且關(guān)鍵的元件。今天就來詳細聊聊Linear Technology公司

高速MOSFET驅(qū)動芯片MAX17603:設計利器與應用指南

高速MOSFET驅(qū)動芯片MAX17600 - MAX17605:設計利器與應用指南 在電子設計領(lǐng)域,高速MOSFET驅(qū)動芯片的性能直接影響著整個電路系統(tǒng)的效率和穩(wěn)定性。今天,我們就來深入探討一下

MAX941/MAX942/MAX944高速低功耗比較器:設計利器解析

MAX941/MAX942/MAX944高速低功耗比較器:設計利器解析 在電子工程師的日常設計工作中,比較器是一種常用的基礎(chǔ)器件。而MAX941/MAX942/MAX944這幾款高速、低功耗、3V

高速低功耗單電源比較器MAX9140/9141/9142/9144:設計利器

高速低功耗單電源比較器MAX9140/9141/9142/9144:設計利器 在電子設計領(lǐng)域,比較器是不可或缺的基礎(chǔ)元件。今天給大家分享一款高性能的比較器產(chǎn)品——Analog Devices公司

高速數(shù)據(jù)傳輸利器:SNx5LVDx3xx系列LVDS接收器深度剖析

高速數(shù)據(jù)傳輸利器:SNx5LVDx3xx系列LVDS接收器深度剖析 在高速數(shù)據(jù)傳輸領(lǐng)域,低電壓差分信號(LVDS)技術(shù)憑借其低功耗、

AD9520-5 12 LVPECL/24 CMOS輸出時鐘發(fā)生器技術(shù)手冊

AD9520-5提供多路輸出時鐘分配功能,具有亞皮秒級抖動性能,并且片內(nèi)集成鎖相環(huán)(PLL),可以配合外部VCO使用。

高速時鐘設計利器:AD9520 - 5全方位剖析

高速時鐘設計利器:AD9520 - 5全方位剖析

評論