外延工藝是指在襯底上生長完全排列有序的單晶體層的工藝。一般來講,外延工藝是在單晶襯底上生長一層與原襯底相同晶格取向的晶體層。外延工藝廣泛用于半導體制造,如集成電路工業的外延硅片。MOS 晶體管的嵌入式源漏外延生長,LED襯底上的外延生長等。根據生長源物相狀態的不同,外延生長方式可以分為固相外延、液相外延、氣相外延。在集成電路制造中,常用的外延方式是固相外延和氣相外延。

固相外延,是指固體源在襯底上生長一層單晶層,如離子注入后的熱退火實際上就是一種固相外延過程。離于注入加工時,硅片的硅原子受到高能注入離子的轟擊,脫離原有晶格位置,發生非晶化,形成一層表面非晶硅層;再經過高溫熱退火,非晶原子重新回到晶格位置,并與襯底內部原子晶向保持一致。

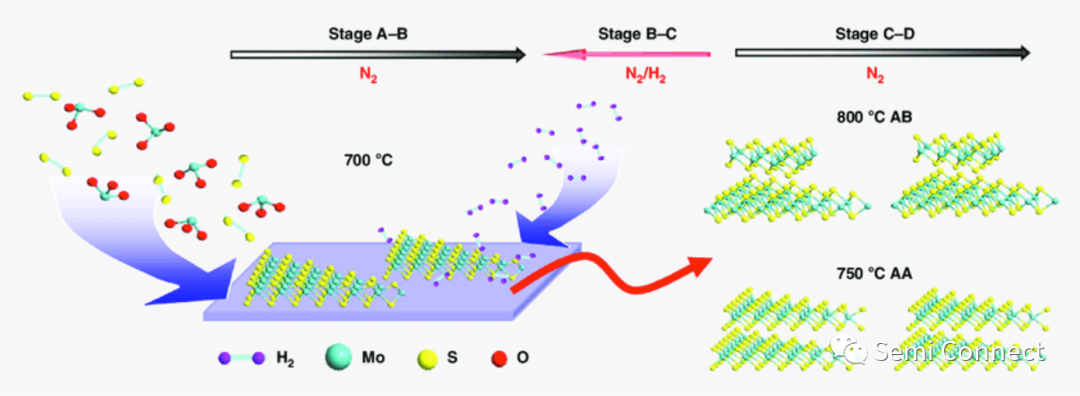

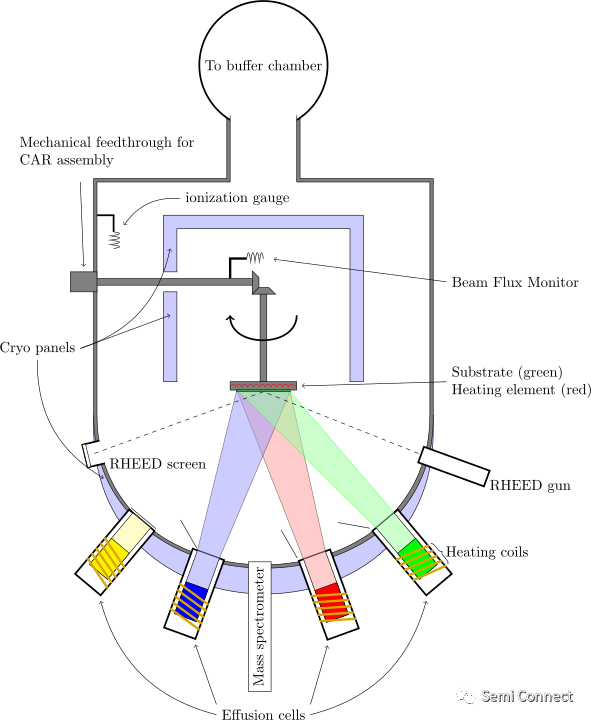

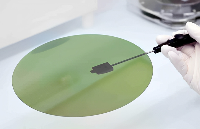

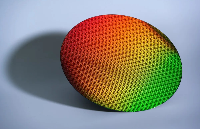

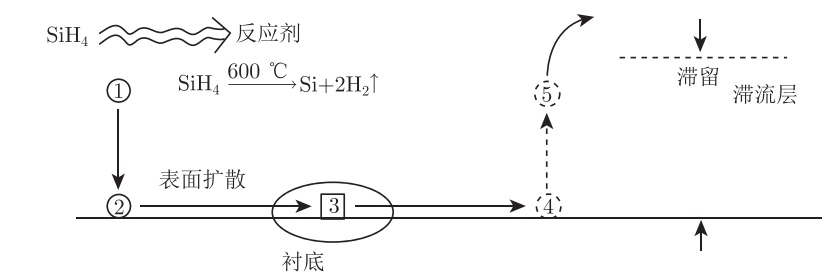

氣相外延的生長方法包括化學氣相外延生長(CVE)、分子束外延( MBD)、原子層外(ALE)等。在集成電路制造中,最常用的是化學氣相外延生長(CVE)。化學氣相外延與化學氣相沉積(CVD) 原理基本相同,都是利用氣體混合后在晶片表面發生化學反應,沉積薄膜的工藝;不同的是,因為化學氣相外延生長的是單晶層,所以對設備內的雜質含量和硅片表面的潔凈度要求都更高。早期的化學氣相外延硅工藝需要在高溫條件下(大于 1000°C)進行。隨著工藝設備的改進,尤其是真空交換腔體(Load Lock Chamber)技術的采用,設備腔內和硅片表面的潔凈度大大改進,硅的外延已經可以在較低溫度 (600~700°C)下進行。 在集成電路制造中,CVE 主要用于外延硅片工藝和 MOS 晶體管嵌人式源漏外延工藝。外延硅片工藝是在硅片表面外延一層單晶硅,與原來的硅襯底相比,外延硅層的純度更高,晶格缺陷更少,從而提高了半導體制造的成品率。另外,硅片上生長的外延硅層的生長厚度和摻雜濃度可以靈活設計,這給器件的設計帶來了靈活性,如可以用于減小襯底電阻,增強襯底隔離等。 嵌入式源漏外延工藝是在邏輯先進技術節點廣泛采用的技術,是指在 MOS 晶體管的源漏區域外延生長摻雜的鍺硅或硅的工藝。引入嵌入式源漏外延工藝的主要優點包括:可以生長因晶格適配而包含應力的贗晶層,提升溝道載流子遷移率;可以原位摻雜源漏,降低源漏結寄生電阻,減少高能離子注入的缺陷。

審核編輯 :李倩

-

單晶體

+關注

關注

0文章

15瀏覽量

8608 -

半導體制造

+關注

關注

8文章

515瀏覽量

26117

原文標題:外延工藝(Epitaxy)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

高純熱壓碳化硅陶瓷外延基座的性能優勢與制造工藝解析

12英寸碳化硅外延片突破!外延設備同步交付

外延片氧化清洗流程介紹

【新啟航】碳化硅外延片 TTV 厚度與生長工藝參數的關聯性研究

從襯底到外延:碳化硅材料的層級躍遷與功能分化

半導體外延和薄膜沉積有什么不同

半導體外延工藝在哪個階段進行的

晶圓清洗后表面外延顆粒要求

臺階儀應用 | 半導體GaAs/Si異質外延層表面粗糙度優化

一文詳解外延生長技術

半導體選擇性外延生長技術的發展歷史

外延工藝(Epitaxy)

外延工藝(Epitaxy)

評論