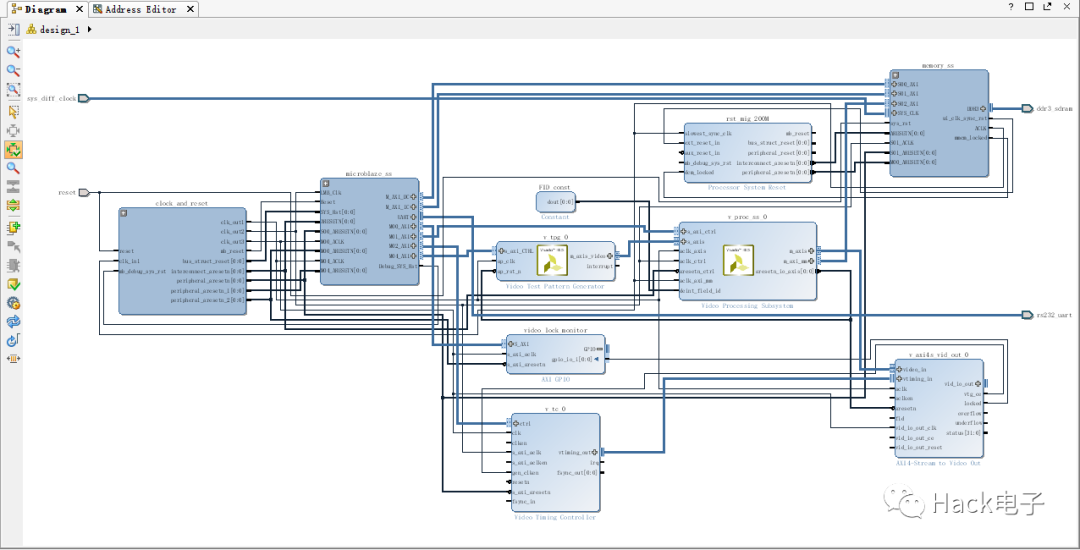

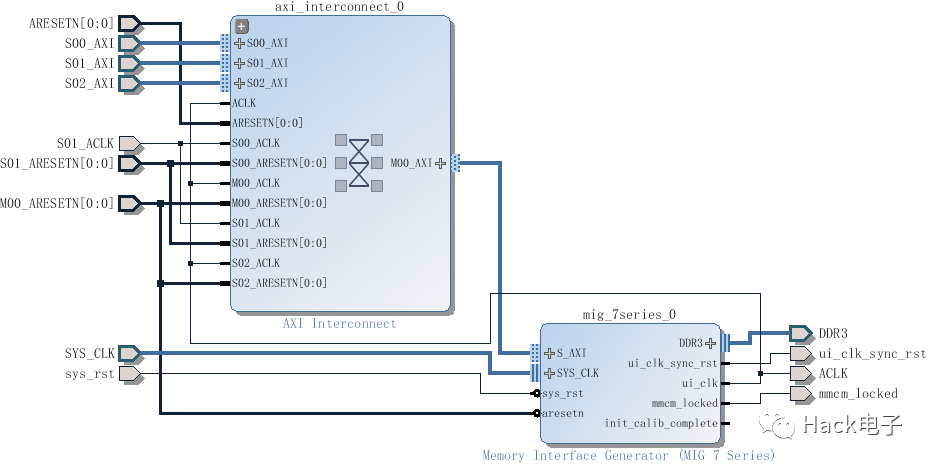

1.memory_ss模塊

slave端口:

S00:

連接設(shè)備:microblaze_ss----M_AXI_DC

時(shí)鐘來(lái)源:S01_ACLK---clk_out2(clock_and_reset)---100MHz

復(fù)位來(lái)源:S01_ARESETN---peripheral_aresetn(clock_and_reset)

S01:

連接設(shè)備:microblaze_ss---M_AXI_IC

時(shí)鐘來(lái)源:S01_ACLK---clk_out2(clock_and_reset)---100MHz

復(fù)位來(lái)源:S01_ARESETN---peripheral_aresetn(clock_and_reset)

S02:

連接設(shè)備:v_proc_ss_0---m_axi_mm(接收video_processing_subsystem master端口傳過(guò)來(lái)的數(shù)據(jù))

時(shí)鐘來(lái)源:mig_7series_0---ui_clk/ACLK

復(fù)位來(lái)源:M00_ARESETN

master端口:

M00:

連接設(shè)備:mig_7series_0---S_AXI(將數(shù)據(jù)傳遞給DDR3)

時(shí)鐘來(lái)源:mig_7series_0---ui_clk/ACLK

復(fù)位來(lái)源:M00_ARESETN

S02,M00公用時(shí)鐘和復(fù)位原因是,對(duì)同一個(gè)數(shù)據(jù)流進(jìn)行操作,接收數(shù)據(jù)與發(fā)送數(shù)據(jù)。

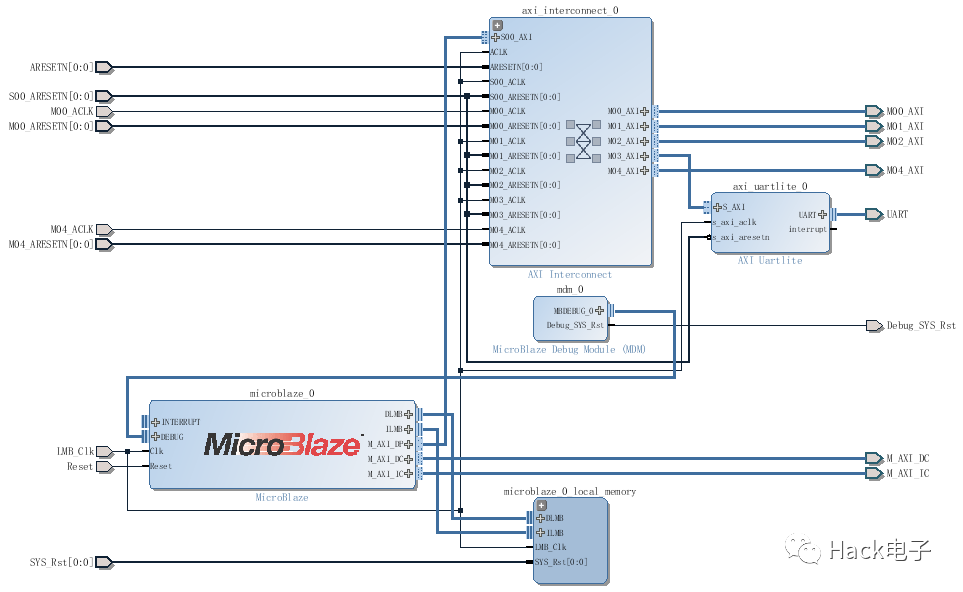

?2.microblaze_ss模塊

?2.microblaze_ss模塊

slave端口:

S00_AXI:

連接設(shè)備:microblaze----M_AXI_DP

時(shí)鐘來(lái)源:LMB_Clk---clk_out2(clock_and_reset)---100MHz

復(fù)位來(lái)源:S00_ARESETN---peripheral_aresetn(clock_and_reset)

master端口:

M00_AXI:

連接設(shè)備:video_lock_monitor(AXI GPIO)---S_AXI

時(shí)鐘來(lái)源:M00_ACLK---clk_out3(clock_and_reset)---9MHz

復(fù)位來(lái)源:M00_ARESETN---peripheral_aresetn_2(clock_and_reset)

M01_AXI:

連接設(shè)備:v_proc_ss_0(video processing subsystem)---s_axi_ctrl

時(shí)鐘來(lái)源:LMB_Clk---clk_out2(clock_and_reset)---100MHz

復(fù)位來(lái)源:S00_ARESETN---peripheral_aresetn(clock_and_reset)

M02_AXI:

連接設(shè)備:v_tc_0(video Timing Controller)---ctrl

時(shí)鐘來(lái)源:LMB_Clk---clk_out2(clock_and_reset)---100MHz

復(fù)位來(lái)源:S00_ARESETN---peripheral_aresetn(clock_and_reset)

M03_AXI:

連接設(shè)備:axi_uartlite_0(AXI Uartlite)---S_AXI

時(shí)鐘來(lái)源:LMB_Clk---clk_out2(clock_and_reset)---100MHz

復(fù)位來(lái)源:S00_ARESETN---peripheral_aresetn(clock_and_reset)

M04_AXI:

連接設(shè)備:v_tpg_0(video Test Pattern Generator)---s_axi_CTRL

時(shí)鐘來(lái)源:M04_ACLK---clk_out1(clock_and_reset)---200MHz

復(fù)位來(lái)源:M04_ARESETN---peripheral_aresetn_1(clock_and_reset)

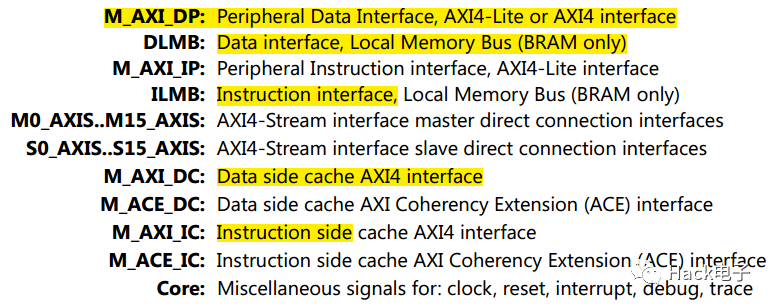

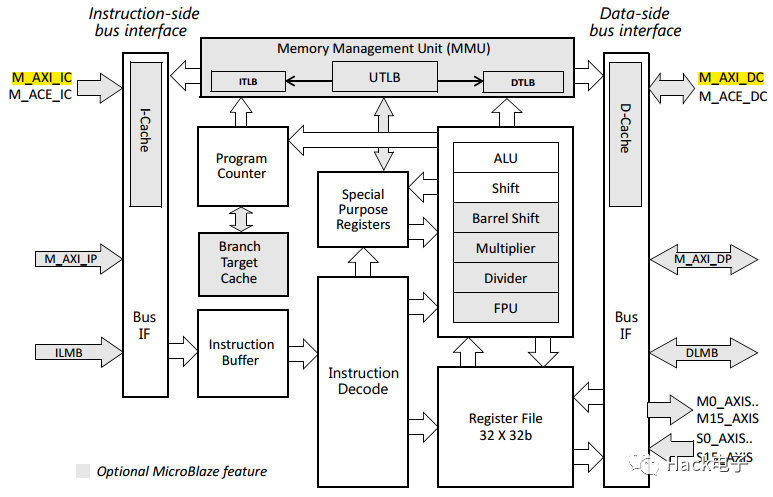

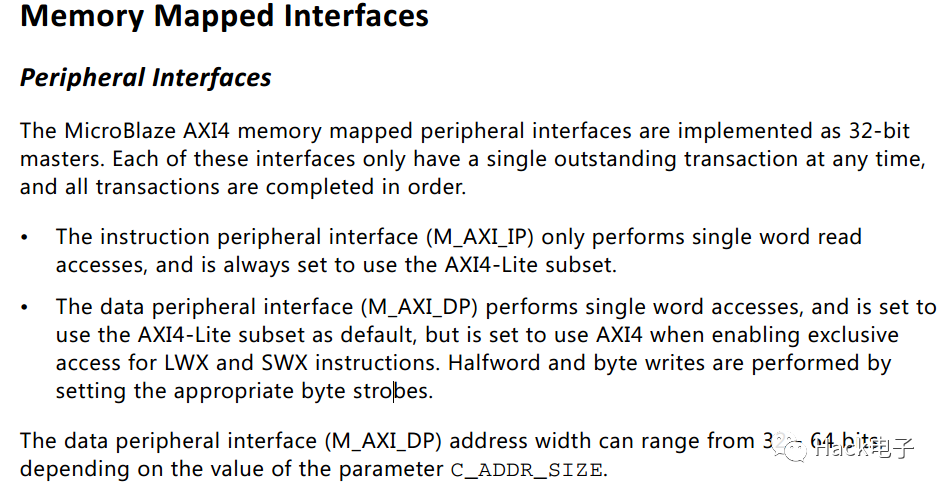

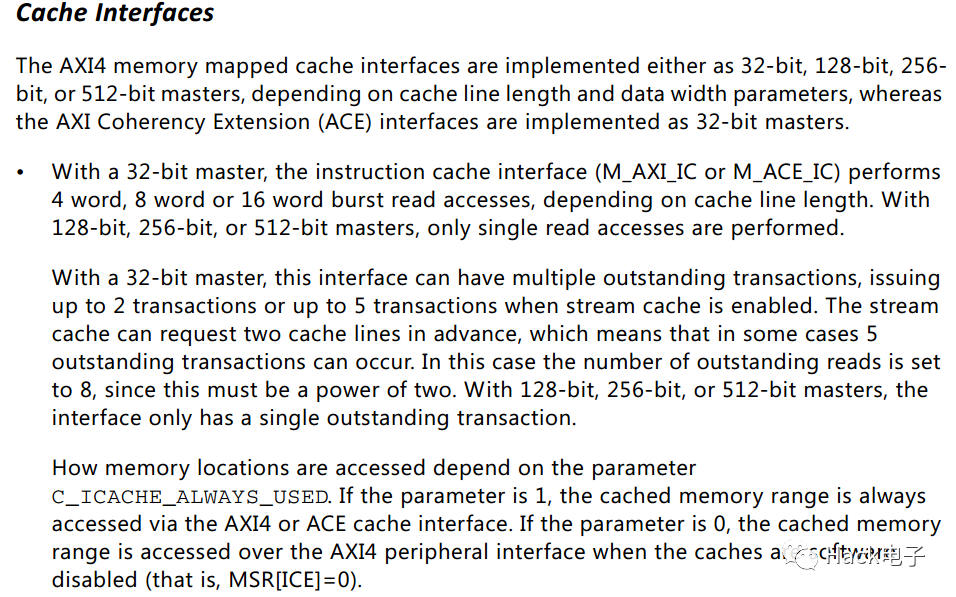

關(guān)于M_AXI_DC,M_AXI_IC端口描述:

MicroBlaze Core Block Diagram

什么是instruction-sdie bus interface, Data-side bus interface:

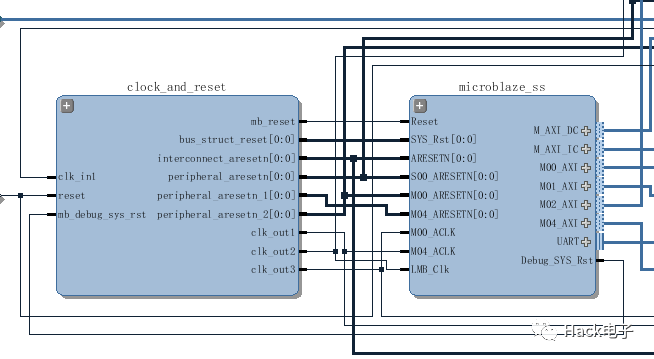

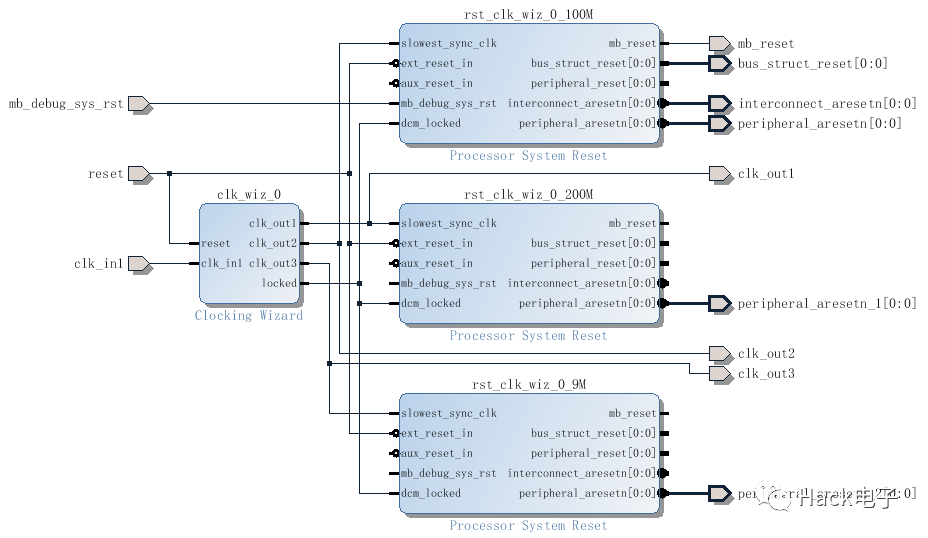

3.Clock_and_reset模塊

clk_wiz_0:

Clk_in1---clk_in1---ACLK(memory_ss)

Clk_out1---200MHz (reset is peripheral_aresetn_1)

Clk_out2---100MHz(reset is peripheral_aresetn)

Clk_out3---9MHz(reset is peripheral_aresetn_2)

審核編輯 :李倩

-

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7342瀏覽量

94938 -

Video

+關(guān)注

關(guān)注

0文章

197瀏覽量

46595

原文標(biāo)題:Video Processing subsystem例程分析

文章出處:【微信號(hào):Hack電子,微信公眾號(hào):Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Video Processing Subsystem與HDMI示例設(shè)計(jì)

如何使用Nexys Video開(kāi)發(fā)板移植e203

GraniStudio:視覺(jué)和運(yùn)控例程

GraniStudio:獲取軸信息例程

SSD2829TQL9 VIDEO BIST無(wú)法正常使用問(wèn)題

QDMA Subsystem for PCI Express v5.0產(chǎn)品指南

test_ff_video_encode編碼報(bào)bmvpu_malloc_device_byte_heap failed怎么解決?

SE5 ffmpeg例程內(nèi)存不釋放的原因?

S-Video接口概述和分類(lèi)

一文詳解Video In to AXI4-Stream IP核

Video Processing subsystem例程分析

Video Processing subsystem例程分析

評(píng)論