在撰寫本文時(shí),HDMI Transmitter Subsystem IP 核與 Video Processing Subsystem IP 核均有多個(gè)示例設(shè)計(jì)可供使用,但并沒(méi)有演示將兩者功能結(jié)合在一起來(lái)使用的設(shè)計(jì)。

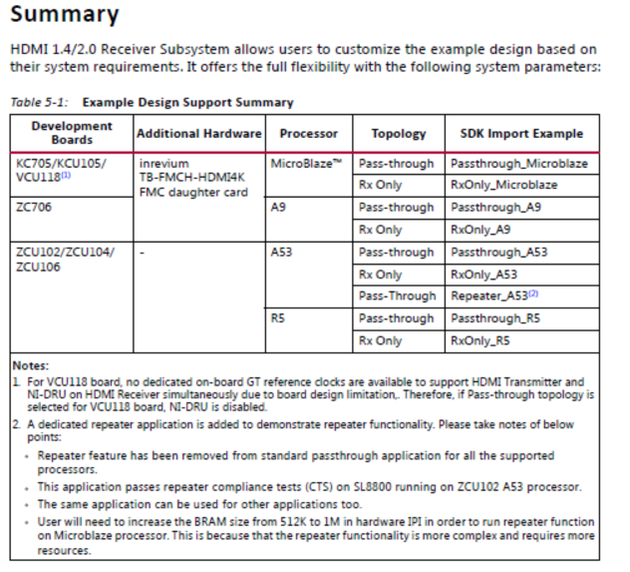

如需了解有關(guān)這些設(shè)計(jì)的信息,請(qǐng)參閱 PG235 和 PG231。

PG235:

https://docs.amd.com/access/sources/dita/map?isLatest=true&url=pg235-v-hdmi-tx-ss&ft:locale=en-US

PG231:

https://docs.amd.com/access/sources/dita/map?isLatest=true&url=pg231-v-proc-ss&ft:locale=en-US

本篇博文將側(cè)重于概述如何創(chuàng)建和運(yùn)行設(shè)計(jì)以將這兩個(gè) IP 結(jié)合在一起來(lái)實(shí)現(xiàn)。

注釋:此設(shè)計(jì)按現(xiàn)狀提供,不含任何保證。它是在正常發(fā)布/測(cè)試流程外構(gòu)建的,僅用于提供指示信息。

SR 門戶不支持本設(shè)計(jì)。如果您對(duì)本設(shè)計(jì)有疑問(wèn),請(qǐng)?jiān)诖?a href="http://www.3532n.com/article/bbs/" target="_blank">論壇板塊上發(fā)帖:

https://adaptivesupport.amd.com/s/topic/0TO2E000000YKY8WAO/video?language=zh_CN

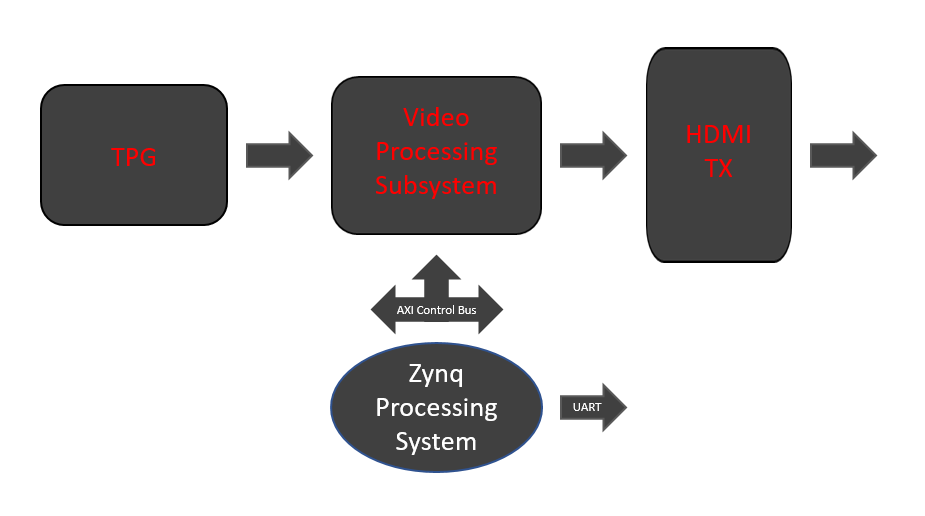

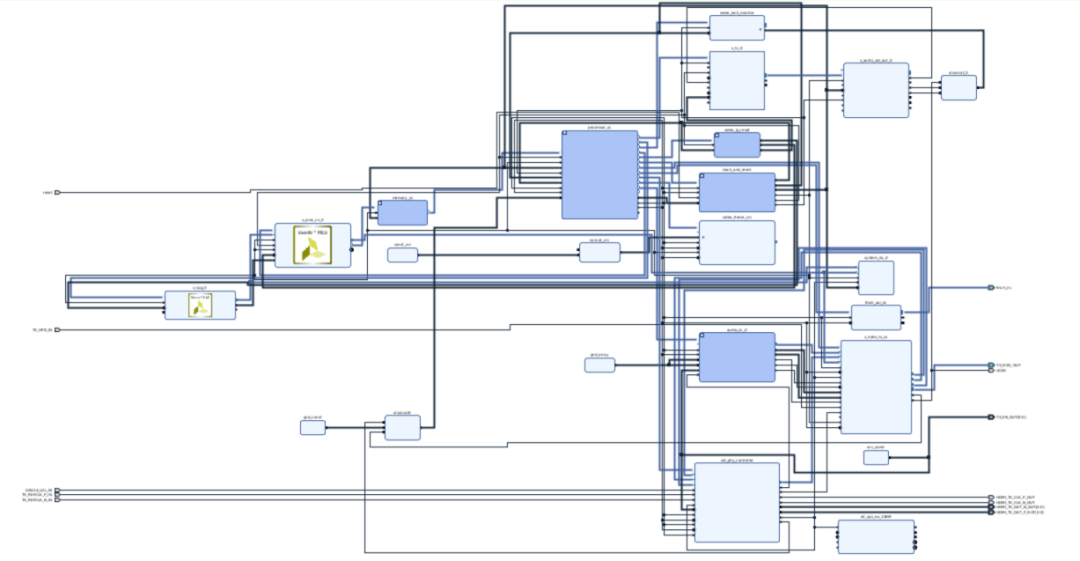

本設(shè)計(jì)演示了如何在 ZCU102 評(píng)估板上使用 AMD Vivado 設(shè)計(jì)套件 2022.1 來(lái)構(gòu)建和運(yùn)行 Video Processing Subsystem + HDMI TX 設(shè)計(jì)。本設(shè)計(jì)基于產(chǎn)品指南中的 HDMI TX Only 設(shè)計(jì)創(chuàng)建,隨后經(jīng)過(guò)更新,添加了 Video Processing Subsystem 功能。

其目的是為了演示如何將 Video Processing Subsystem 與 HDMI TX Subsystem 結(jié)合在一起來(lái)運(yùn)作并快速實(shí)現(xiàn)。

它包括下列組成部分:

復(fù)位功能

AMD Zynq 子系統(tǒng)例化,用于控制 IP

GPIO 用于監(jiān)控狀態(tài)(原示例設(shè)計(jì)保留不變)

Test Pattern Generator (TPG) 用于創(chuàng)建視頻數(shù)據(jù)

Video Processing Subsystem 用于轉(zhuǎn)換顏色格式和分辨率

Video PHY Controller

HDMI TX Subsystem

使用提供的腳本創(chuàng)建比特流:

1.在命令行或 Vivado 終端內(nèi),運(yùn)行來(lái)自以下目錄的 Tcl 腳本,同時(shí)確保 hdmi.xdc 文件與該 Tcl 腳本位于相同目錄下:

Vivado -source v_proc_ss_0_ex.tcl

2.等待腳本完成,然后運(yùn)行 Vivado 生成比特流。

此操作能以腳本模式完成,也可以打開 Vivado GUI 并遵循典型的綜合、實(shí)現(xiàn)、比特流生成流程來(lái)完成。

3.生成比特流后,導(dǎo)出 XSA 文件。

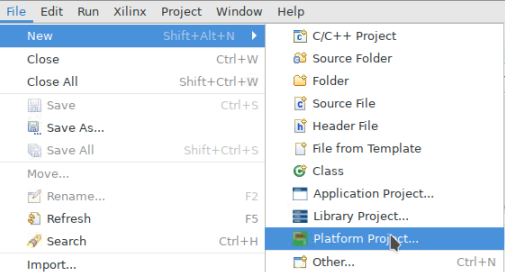

如何基于 XSA 來(lái)創(chuàng)建 ELF 文件:

1.打開 AMD Vitis 統(tǒng)一軟件平臺(tái)的 GUI。

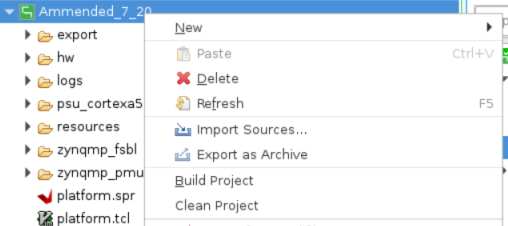

2.創(chuàng)建新的平臺(tái)工程并指向從 Vivado 工程導(dǎo)出的 XSA。

3.使用構(gòu)建工具來(lái)構(gòu)建 BSP。

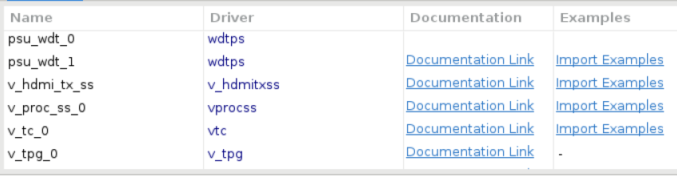

4.構(gòu)建好 BSP 后,選擇“Drivers”中的“Import Examples”。

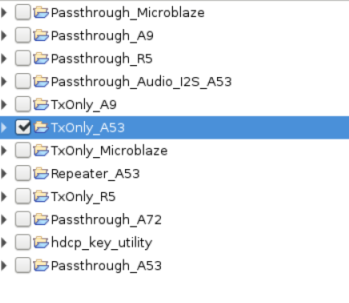

5.導(dǎo)入 HDMI TX Only。

6.將 /src 下的文件替換為 /SW 內(nèi)的文件。

這些文件均已經(jīng)過(guò)編輯,適用于 VPSS + HDMI 示例。

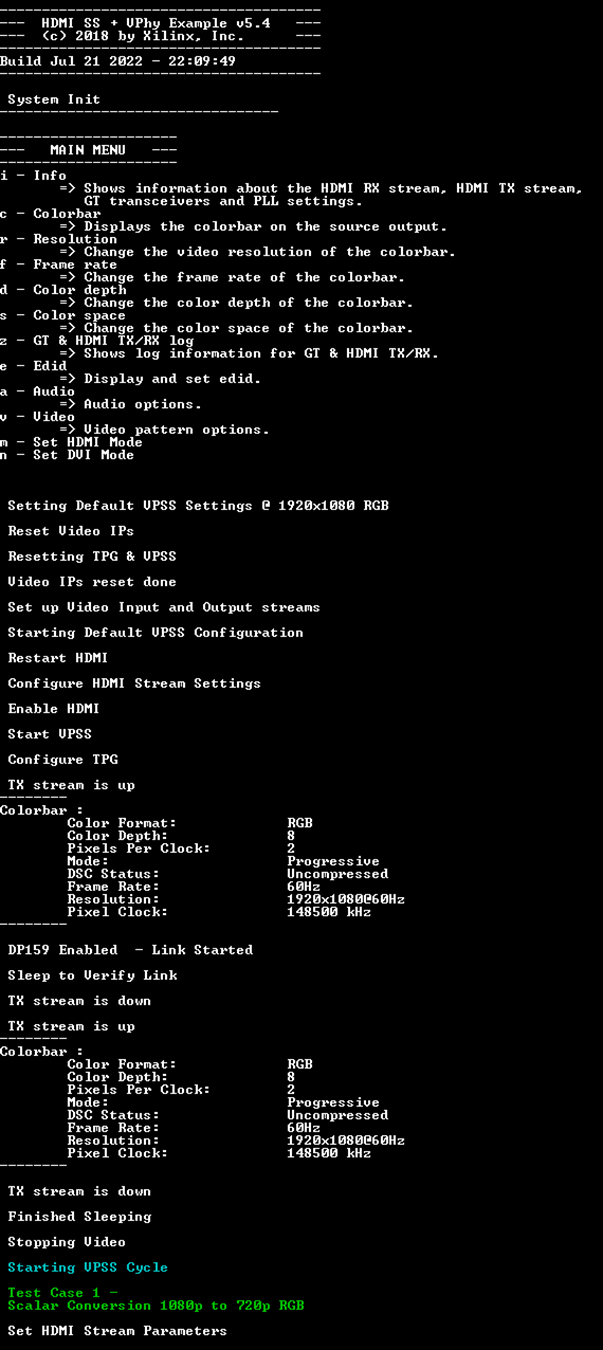

7.構(gòu)建并測(cè)試,下圖顯示了 UART 控制臺(tái)。

注釋:如需了解有關(guān)構(gòu)建和測(cè)試的更多信息,請(qǐng)參閱 PG235 和 PG231。

點(diǎn)擊閱讀原文,查看相關(guān)附件。

-

amd

+關(guān)注

關(guān)注

25文章

5693瀏覽量

140150 -

HDMI

+關(guān)注

關(guān)注

34文章

1906瀏覽量

161006 -

Video

+關(guān)注

關(guān)注

0文章

197瀏覽量

46572 -

IP核

+關(guān)注

關(guān)注

4文章

344瀏覽量

52006

原文標(biāo)題:開發(fā)者分享|Video Processing Subsystem + HDMI 示例設(shè)計(jì)

文章出處:【微信號(hào):gh_2d1c7e2d540e,微信公眾號(hào):XILINX開發(fā)者社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

HDMI VCU118設(shè)計(jì)移植到VCU128開發(fā)板的步驟解析

Video Processing Subsystem與HDMI示例設(shè)計(jì)

Video Processing Subsystem與HDMI示例設(shè)計(jì)

評(píng)論