文章首發于《中國集成電路》,由國家工業和信息化部主管,中國半導體行業協會主辦的官方專業期刊。感謝《中國集成電路》對芯華章的認可! FPGA(Field Programmable Gate Array)原型驗證,基于其成本適中、速率接近真實系統環境等優點,受到了驗證工程師的青睞。正是由于廣泛豐富的應用場景,FPGA 原型系統上往往需要設計各種不同的接口,用以和外界進行數據信號的交換互通,滿足不同的使用需求。不同的接口設置與選擇,也會極大影響原型驗證系統產品的應用范圍以及驗證效率。因此,如何合理規劃接口設置,就成為了一款優秀的原型驗證系統必須要考慮的重要問題。 首先和大家介紹下目前常見的接口類型。

子卡擴展接口

考慮到使用場景通用性,一套原型平臺不可能覆蓋到所有協議接口,因此會布局一些用于擴展特定功能子卡的連接器,支持各類協議。這類接口少則幾個,多達幾十個。

多FPGA互聯接口

在較大的邏輯設計中,用于多片FPGA 切割處的互聯IO之間的連接,一般通過互聯電路板或特制線纜這兩種形式進行互聯。此類接口和上一點談到的子卡擴展接口往往能夠兼容使用。

高速接口GTH/GTY

用來和外部高速數據傳輸的鏈路設備或測試儀器相連;接口形式包括如PCI Express、QSFP+、MiniSAS等等。

時鐘輸入/輸出接口

原型系統自身產生時鐘輸出到外部的設備或其他原型系統的通道;反之,也可以接收外部輸入的時鐘源。在多個系統互聯時,起到時鐘同步的作用。

低速接口

FPGA原型系統通過其連接調試上位機、不同協議的仿真器及邏輯分析儀、低速外設元件等,包括JTAG、UART、I2C、SPI、GPIO、PMOD等。

關于“擴展子卡和用于多片FPGA IO互聯的接口”

此類應用場景最為普遍,我們先列出幾種業界較為主流的用于該類功能的連接器:

1

PHC連接器

PHC連接器的全稱為Prototyping High-performance Connector. 從信號的組成來看,其種類較為豐富,包含了電源信號(含管理信號)、接地信號、I2C信號(地址/時鐘/數據)、全局時鐘信號、數據信號及保留信號。

以芯華章科技(X-EPIC)出品的樺捷HuaPro-P1 高性能FPGA原型驗證系統為例,上面搭載了48個PHC連接器;每個PHC連接器的可用IO為50個。經過實測,HuaPro-P1 PHC 連接器IO的單端數據速率最高可達到1.4Gbps,處于業界領先水平。

PHC連接器的好處是顆粒度小,使用方便靈活,對于寶貴及有限的FPGA IO資源,能夠做到高利用率而不造成浪費。

2

FMC連接器

FMC的英文全稱為FPGA Mezzanine Card。而這里談到的FMC連接器(FMC Connector)是其中的組成部分,遵循 VITA 57.1 標準;

按物理Pin的數量來區分,包括400 Pin的FMC HPC(high pin connector)及160 Pin的FMC LPC(low pin connector)兩種。

圖1:母板上適用的FMC母頭插座

圖2: 子卡上適用的FMC公頭插座

總體上看,FMC接口從標準上就是為“扣板”形式而定義的,對線纜連接的支持不太理想,成本高而且容易損壞。

3

Prodigy連接器

Prodigy為部分廠商的FPGA系統所采用的連接器,總體看,其信號組成及電氣特性同FMC連接器相仿,區別在于體積略小和總的信號數量相應減少。

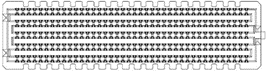

綜合考慮上述三種連接器的特性,目前看,以PHC連接器的“小型、靈活”的特點,更加適合于子卡的擴展及FPGA系統之間進行互聯布局。

其主要的原因是:

連接器比較小巧,則在進行線纜或子卡插拔的時候,更容易操作;

其次,連接線纜不會很粗,布局起來更方便走線;

PHC連接器的顆粒度小,那么在子卡的使用率上,IO使用率最高;不會因為一個大連接器占用很多IO,但實際只用到其中一部分,從而造成系統性浪費的風險;

根據實際情況,可以定制PHC轉其他連接器的轉接卡(比如FMC或用戶自定義接口),這樣對于用戶已有的子卡,可以繼續兼容使用而不造成浪費;

最后,互聯線纜的成本都不低,從幾十、幾百乃至幾千美金一根;而包含IO數較少的電纜,在成本方面有優勢,一旦出現有損壞、老化的情況,以單根電纜為單位更換的成本最低。

高速接口GTH/GTY

新技術發展下的FPGA芯片,都已基本帶有高速Serdes通道。Serdes,是英文Serializer(串行器)/Deserializer(解串器)的簡稱。它采用的是點對點(Point to Point)的串行通信技術,充分利用傳輸媒體的信道容量,減少所需的傳輸信道和器件引腳數目,提升信號的傳輸速度,從而降低通信成本。這些通道往往也以不同的接口方式連接到FPGA原型系統的接口上。其中包括了PCIE/SATA/Ethernet/QSFP+/MiniSAS和MCIO等。通過對應的不同接口cable,能夠和外部的高速設備或是儀器進行連接。

1

PCIe(Peripheral Component Intercon-

nect express)是一種高速串行計算機擴展總線標準,獨占通道帶寬;傳輸高速可靠。目前市售的,較為高端的FPGA芯片都原生支持PCIe傳輸協議。HuaPro-P1系統自帶 PCIe 3.0的接口可以實現雙向 128Gbps的高速數據傳輸。

2

QSFP+ 是一種能夠支持熱插拔的光模塊,結構緊湊,因其包含四條高速通道,故傳輸速率可達40Gbps。QSFP+ 在High Performance Network,Data Center等場景應用廣泛。從協議上看,QSFP+支持的是SFF-8436協議和QSFP 多源協議。

由于光模塊優越的物理特性,它能夠把電信號轉換為光信號,通過光纖達到遠距離傳輸的效果,然后在對端再轉回電信號;并且這樣也不會影響信號的質量。

3

另一種較為常見的高速傳輸的接口為Mini SAS。Mini SAS連接器符合SFF-8643標準,是一款36針的高密度SAS連接器,符合最新的SAS 3.0規范,并支持12Gb/s數據傳輸協議。支持最多4通道的高速數據傳輸。一種典型的應用是Host PC通過Mini SAS的cable連接到FPGA原型系統,這樣可以實現主機和FPGA之間高速通信,達到軟硬件協同驗證的目的。

時下熱門的Chiplet技術和高速接口也有著很大的聯系,因為裸片之間的超短距離和鏈路上(裸片間互聯)數據傳輸速率將超過100Gbps。這在普通接口上的實現是個幾乎不可能完成的任務;而擁有高速傳輸通道的FPGA平臺為Chiplet互連的驗證提供了很大的可能性。

值得一提的是,芯華章科技(X-EPIC)出品的樺捷HuaPro-P1 高性能FPGA原型驗證系統,規劃時候充分考慮了用戶的潛在高速應用需求,因此,在系統的主體已經集成了上述三種高速接口;而市面上其他的原型系統,很少有做到同時集成,一般需要外接子卡才能使用;這樣在進行如服務器機架部署的時候,在空間上產生一定的阻礙及局限性。

時鐘輸入/輸出接口

現代的芯片設計規模日益增大,通常有用到多個FPGA系統級聯使用的情況,除了前述數據通道的傳輸,還有一個必要的部分就是進行時鐘的傳輸。這對于同步數字系統尤為重要。

1

一種方式是采用獨立走線的同軸射頻連接器;常見的如SMA,SMB,MMCX等接口;當多路時鐘傳輸時,因為線束以‘對’的方式單獨走線,故會顯得比較雜亂。

2

另外一種更優化的傳輸方式是采用如下的連接器:Samtec出品的 Q Strip High-Speed Ground Plane Socket Strip;它可以同時傳輸多路時鐘、復位信號;且只需要一根扁平形狀的電纜接口。在整個布局上較為簡便、美觀。芯華章HuaPro-P1系統采用這種連接器,并支持最大16臺P1系統的級聯。

低速接口

最后我們來看一下FPGA系統上常用的低速接口:

1

JTAG(Joint Test Action Group,聯合測試工作組)接口

主流分為若干種不同IO數,用以FPGA 廠商的JTAG調試器、ARM 調試仿真器等連接使用。JTAG調試接口必須使用VCC、GND電源信號,以及TMS、TCK、TDI、TDO四根調試信號,分別對應為模式選擇、時鐘、數據輸入和數據輸出線。隨著可用針數增大,另外可選TRST、RESET復位信號和RTCK(同步時鐘)信號。

2

UART接口

通用異步收發器 (Universal Asynchronous Receiver/Transmitter),以一種串行形式的,全雙工異步通信協議。其通信格式分為起始位、數據位、奇偶校驗位、停止位和空閑位等。通過UART接口,FPGA系統和Host上位機相連,可以發送硬件測試中的調試log信息到主機中;相反,主機也可以通過UART口下發一些測試命令及少量的測試數據到FPGA中去。

3

I2C 接口

最早由飛利浦公司開發的雙向的二進制雙線同步串行總線,它屬于一種半雙工模式;只需SDA(串行數據線)和SCL(串行時鐘線)即可連接位于總線上的器件。它的好處是電路接口簡單,總線長度達25英尺和支持組件多達40個。在通常的FPGA開發中,I2C往往被用來連接EEPROM或LED顯示屏、傳感器等元件。

4

SPI(Serial Peripheral Interface,串行外圍設備接口)通訊協議

一種同步的串行接口,需用四根管腳用來控制及數據傳輸,廣泛用于EEPROM、Flash、ADC(數模轉換器)及數字信號解碼器上,是比較常用及較為重要的通訊協議之一。

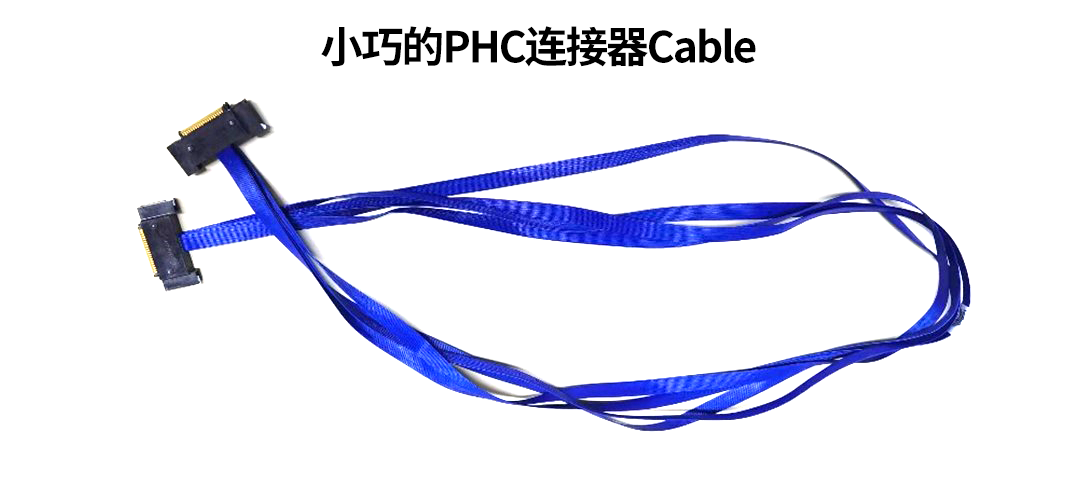

針對用戶對于低速接口的需求,HuaPro-P1系統配套的GPIO子卡,單卡上集成了例如多種JTAG、UART、CAN、DB9等接口,同時也支持如1.8V/2.5V/3.3V/5V多種電壓的GPIO,用戶只需通過一些簡單的跳線設置就可以兼容支持。

小結

以上就是關于FPGA原型驗證系統的常見接口介紹。各種接口,不論尺寸大小、速度快慢都有其獨到的作用。基于這些五花八門的接口,對用戶來說若要人工手動去做原型項目分割、IO復用和時鐘處理等工作,是非常麻煩的;因此還是需要原型系統的配套軟件工具具有從ASIC設計到FPGA設計的轉換、FPGA綜合、自動分割、自動化后處理等上述這些技術要點的能力。

用戶在選擇原型產品的時候,需從長遠使用狀況,綜合考慮選用擴展能力強、支持外部協議豐富、子卡/線纜配件成本相對較低,互聯形式靈活、方便,及配套軟件自動化集成度高的產品。芯華章的HuaPro系列FPGA原型系統產品,給用戶提供了軟硬件全套的FPGA原型實現工具和平臺,能夠幫助客戶最快完成系統集成驗證和軟件提前開發的工作。

審核編輯 :李倩

-

FPGA

+關注

關注

1660文章

22394瀏覽量

634786 -

連接器

+關注

關注

102文章

16110瀏覽量

146706 -

FMC

+關注

關注

0文章

112瀏覽量

20693

原文標題:如何在N多選擇中,為FPGA原型驗證系統規劃實用高效的接口?

文章出處:【微信號:X-EPIC,微信公眾號:芯華章科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RDMA設計35:基于 SV 的驗證平臺

關于MT6901的直線DEMO介紹

Altera FPGA的Avalon MM總線接口規范介紹

思爾芯原型驗證系統助力昆明湖V2成功啟動GUI OpenEuler

FPGA原型驗證實戰:如何應對外設連接問題

FPGA測試DDR帶寬跑不滿的常見原因及分析方法

如何在智多晶FPGA上使用MIPI接口

西門子桌面級原型驗證系統Veloce proFPGA介紹

超大規模芯片驗證:基于AMD VP1902的S8-100原型驗證系統實測性能翻倍

關于FPGA原型驗證系統的常見接口介紹

關于FPGA原型驗證系統的常見接口介紹

評論