新思科技近日宣布,全面升級其高性能硬件輔助驗證(HAV)產品組合,推出全新一代HAPS-200原型驗證系統和ZeBu仿真系統。

這兩種解決方案都基于新款的AMD Versal Premium VP1902自適應片上系統(SoC),運行時性能、編譯時間和調試效率都得到了顯著提升。

相較于業界容量最高、密度最佳的硬件加速系統ZeBu Server 5,全新升級的ZeBu仿真系統,運行速度更高,能夠處理高達154億邏輯門的設計規模。這讓開發者能夠在性能、容量與密度之間擁有更大的靈活性。

此外,開發者還將受益于更快的軟件啟動體驗(如在移動應用中啟動Android系統)。同時,混合仿真現在支持更新、更快的新思科技Virtualizer虛擬原型多線程技術。

最為重要的是,新思科技正在與客戶合作,通過將模塊化HAV方法從HAPS原型設計擴展到ZeBu硬件加速,克服超過600億邏輯門規模先進設計的驗證挑戰。

推動這些擴張的因素是什么?

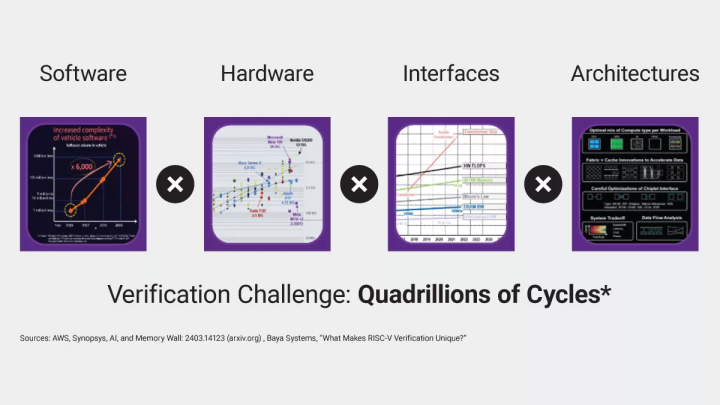

復合復雜性(涵蓋軟件、硬件、接口和工作負載優化架構)為當前最先進芯片、系統級芯片(SoC)和Multi-Die設計的開發者帶來了巨大的挑戰。特別是驗證和軟件開發過程可能需要在仿真、硬件加速和原型設計階段完成數千萬億個測試和驗證周期。因此,人們明顯需要更快的HAV解決方案,以加速先進芯片設計的開發和驗證,并為其所支持的軟件定義系統的優化功能提供保障。

▲圖1:日益復雜的形勢推動著硬件輔助驗證需求的發展

新思科技始終處于HAV創新的前沿。HAPS-200原型驗證系統和ZeBu仿真系統均采用新思科技在2022年推出的突破性概念:硬件加速和原型就緒(EP-Ready)硬件概念,并采用AMD最新的現場可編程門陣列(FPGA)技術發展創新,進而為不同設計規模和用例提供業界領先的性能。

通過這種方式,HAPS-200原型驗證系統和ZeBu仿真系統可實現超強靈活性,提高客戶投資回報率,并最終改變先進芯片和軟件定義系統的驗證流程。

針對性能進行了優化:新一代原型HAPS-200

HAPS-200以業界領先的運行效率,為高性能硬件和軟件驗證任務提供出色支持。同時,它也是接口協議驗證、合規性測試及高速認證的理想選擇。

與其前代產品HAPS-100相比,新產品的性能提高至2倍,調試帶寬增加至4倍

使用異步設計架構,實現高達數十MHz的速度,接口協議子系統的速度可達400MHz以上

可與現有的HAPS-100原型環境、HT3連接器和配件一同使用

從單個FPGA擴展到多機架設置,容量高達10.8 BG

輕松重新布線,以優化性能

可通過ZeBu軟件,利用EP-Ready硬件配置為硬件加速用例

針對靈活性進行了優化:ZeBu高性能硬件加速

ZeBu仿真系統為硬件加速用例(包括RTL驗證和性能/低功耗分析)、軟件啟動和高級調試提供業界領先的性能。

與其前代產品ZeBu EP1和ZeBu EP2相比,新一代ZeBu產品的性能提高至2倍、調試帶寬增加至8倍、容量擴大至6倍,編譯速度也有一定的提升。

最大容量擴展至154億邏輯門。

提供更強大的跟蹤內存,能夠快速實時捕獲設計波形和調試軌跡。

EP-Ready硬件可通過HAPS ProtoCompiler配置為原型設計用例。

EP-Ready硬件提供出色的投資回報率和極致靈活性

HAPS-200原型驗證系統和ZeBu仿真系統均基于EP-Ready硬件,支持通過軟件和布線重新配置,以適應從詳細RTL驗證至高速軟件驗證等所有硬件加速和原型設計用例。除了提供優越的投資回報率(ROI)之外,這種靈活性還直接解決了驗證規劃中的一大挑戰性難題。

長期以來,設計團隊在做出硬件決策和投資時,往往需要依賴對驗證需求的早期預測。在這種情況下,隨著項目和需求的發展,他們經常會遇到資源短缺(需要進行更多預測和投資)或利用不足(浪費預算)等問題。

我們的EP-Ready硬件平臺消除了這種不確定性和相關投資需求,在以下方面有顯著改善:

資源優化:團隊可以使用單一硬件平臺支持所有驗證用例(并同時管理多個項目),而無需維護用于硬件加速和原型設計的各種異構硬件池。

降低風險:重新配置硬件的能力降低了與早期驗證規劃決策相關的風險。隨著項目需求的變化,團隊可以調整其驗證方法,而無需額外購置新硬件。

運營效率:管理用于硬件加速和原型系統的單一硬件平臺可以減少操作復雜性、培訓和維護。

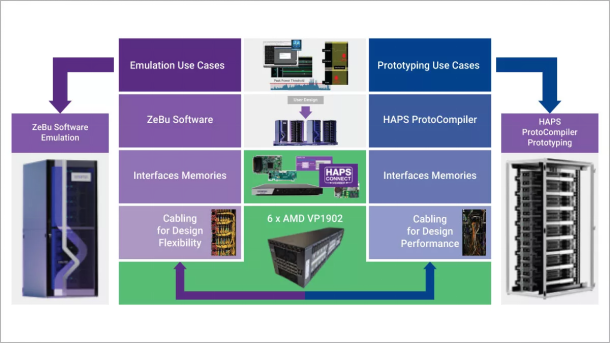

▲圖2:新思科技EP-Ready硬件平臺具有兩個用于硬件加速和原型系統的軟件堆棧

我們的EP-Ready硬件基于統一的計算平臺,集成了最新的AMD VP1902自適應SoC、電纜、內存和接口協議解決方案。通過靈活的布線和軟件配置,用戶可以根據需求選擇同步時鐘實現設計靈活性,或采用異步時鐘優化性能表現。隨著多個(通常是并行的)項目需求的變化,EP-Ready硬件能夠快速重新配置,滿足不同場景的需求。

模塊化HAV方法可擴展容量,減少軟件啟動的時間和成本

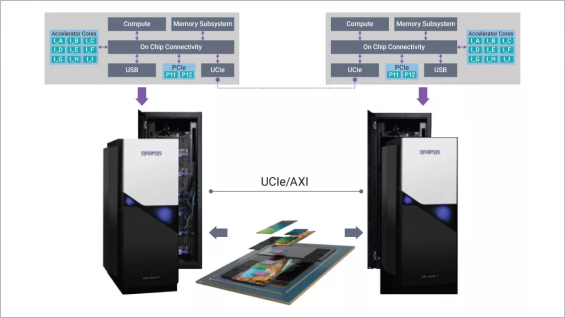

現代芯片架構本質上是模塊化的,多個小芯片通過UCIe等標準以及AXI和CHI等協議連接。硬件和軟件復雜性的不斷增加,導致小芯片呈分散化趨勢,驗證方法也隨之向模塊化發展。

▲圖3:新思科技模塊化HAV方法

我們的模塊化HAV方法使用戶能夠將大型設計分解為可以獨立驗證的單個組件,然后便可以將其集成到更大的SoC或Multi-Die封裝中。團隊可以在自然邊界處分割設計,例如UCIe接口和AXI/CHI協議。

驗證完成后,就可以使用廣泛的接口協議解決方案組合連接這些單獨的組件。這些方案針對每個協議的延遲容忍度都進行了優化,使得SoC和系統驗證團隊能夠維護現有的功能驗證結構,讓每個組件以最佳速度執行。

模塊化HAV方法支持經過擴展的新思科技HAV產品組合,并在以下方面有所改進:

可擴展性:支持超過600億邏輯門的驗證容量,團隊可以高效驗證用于AI訓練、先進數據中心處理器和高性能計算的最大SoC和Multi-Die設計。

生產效率:多個團隊可以并行處理不同的子系統,大幅提高驗證速度和效率。更改某個子系統時不需要重新驗證其他子系統。使用較小的子系統時,軟件啟動速度也更快。

新思科技HAV產品組合:半導體和設計創新的基石

HAPS-200原型驗證系統和ZeBu仿真系統代表了硬件輔助驗證領域的重大飛躍。作為我們高性能HAV產品組合的擴展,它們為用戶提供了優化的性能、容量、可擴展性和密度。通過軟件和電纜的重新配置,這些工具展現出超強的靈活性,能夠支持多個項目或根據項目需求動態調整系統資源。

隨著行業向更集成、更復雜、軟件定義的系統發展,早期軟件驗證和高效芯片驗證流程變得愈發重要。HAPS-200原型驗證系統和ZeBu仿真系統和完整的新思科技HAV產品組合正在幫助行業應對并克服軟件、硬件、接口和架構的復合復雜性,為半導體設計的未來奠定堅實基礎。

-

soc

+關注

關注

40文章

4599瀏覽量

229628 -

原型驗證

+關注

關注

0文章

24瀏覽量

10977 -

新思科技

+關注

關注

5文章

968瀏覽量

52962 -

仿真系統

+關注

關注

1文章

105瀏覽量

21715

原文標題:新思科技新一代HAPS-200原型驗證和ZeBu EP硬件仿真系統如何全面提升驗證效率?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

新思科技發布全新軟件定義硬件輔助驗證解決方案

新思科技首屆Converge大會隆重舉行

是德科技推出一系列全新Scale-up驗證解決方案

新思科技首屆Converge大會全新升級啟航

思爾芯榮登“國產EDA工具口碑榜”,以“芯神瞳”原型驗證解決方案賦能芯片創新

思爾芯原型驗證系統助力昆明湖V2成功啟動GUI OpenEuler

新思科技HAPS-200助力阿里巴巴達摩院加速玄鐵C930開發驗證

思科Cisco 8223:51.2Tbps P200芯片助力AI數據中心

綠氫系統 PEM 電解槽直流接入仿真驗證深度解析

超大規模芯片驗證:基于AMD VP1902的S8-100原型驗證系統實測性能翻倍

綠氫系統篇丨PEM電解槽模型交流接入模式仿真驗證

綠氫系統篇丨PEM電解槽模型交流接入模式仿真驗證

新思科技推出全新HAPS-200原型驗證系統和ZeBu仿真系統

新思科技推出全新HAPS-200原型驗證系統和ZeBu仿真系統

評論