本文參考Altera文檔:1. Introduction to the Avalon Interface Specifications

Avalon總線是一種協議較為簡單的片內總線,主要用于連接片內處理器與外設,以構成片上可編程系統(SOPC)。使用Avalon接口能夠輕松連接Intel FPGA中的各個組件,從而簡化了系統設計。Avalon接口常用于高速數據流傳輸、讀寫寄存器和存儲器、控制片外器件等。此外,也可以使用Avalone接口自定義組件,以增強設計的互操作性。

Avalon共有以下七種接口:

Avalon Clock Interface, Avalon時鐘接口 -- 驅動或接收時鐘信號的接口。

Avalon Reset Interface, Avalon復位接口 -- 驅動或接收復位信號的接口。

Avalon Memory Mapped Interface (Avalon-MM), Avalon存儲器映射接口 -- 基于地址的讀/寫接口,是主-從連接的典型接口。

Avalon Streaming Interface (Avalon-ST), Avalon Streaming接口 --支持單向數據流的接口,包括多數據流、數據包和DSP數據的傳輸。

Avalon Conduit Interface, Avalon Conduit接口 -- 適用于不適合任何其他Avalon類型的單個/多個信號。使用該接口可以將信號導出到頂層SOPC系統,這樣就可以將它連接到設計的其他模塊。

Avalon Tri-State Conduit Interface (Avalon-TC), Avalon 三態Conduit接口 -- 與片外設備的接口。多個外設可以通過信號的多路復用共享引腳,從而減少FPGA引腳數和PCB走線數。

Avalon Interrupt Interface, Avalon 中斷接口 -- 允許組件向其他組件發送事件信號的接口。

一個組件可以包含多個不同類型的接口,也可以包含多個相同類型的接口。

Avalon接口通過屬性(property)描述它們的行為。每種接口類型的規范定義了所有接口的屬性和默認值。比如,Avalon-ST接口的maxChannel屬性指定接口支持的通道數量,Avalon Clock接口的clockRate屬性描述時鐘信號的頻率。

每個Avalon接口都定義了一系列的信號及其行為,并且多數信號都是可選的,這允許組件設計者能夠更加靈活地選擇需要的信號類型。例如,Avalon-MM接口包含可選的beginbursttransfer和burstcount信號,用于那些支持突發(bursting)傳輸的組件。Avalon-ST接口包含可選的startofpacket和endofpacket信號,用于那些支持數據包的接口。

每種接口都有時序方面的信息,這些時序信息描述了針對單個類型的傳輸。

注:本實驗只用了到Avalon時鐘接口、Avalon復位接口、Avalon存儲器映射接口和Avalon Conduit接口,下面將著重介紹這四種接口,其余接口請參考請參考Intel FPGA的Avalon Interface Specification文檔。

Avalon時鐘接口

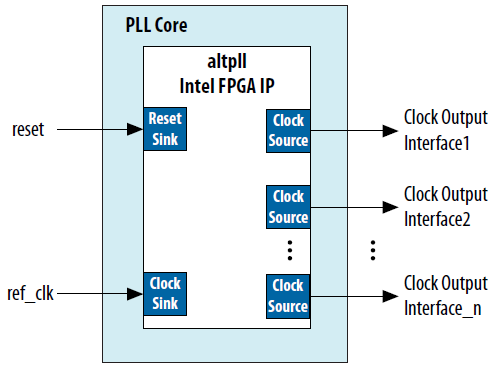

Avalon時鐘接口定義了組件使用的時鐘,一個組件可以有時鐘輸入、時鐘輸出或時鐘輸入輸出都含有。例如,鎖相環(PLL)是一個包含了時鐘輸入和時鐘輸出的組件,如圖所示。

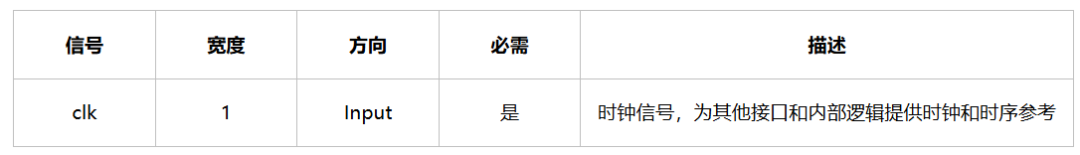

Clock Sink信號

Clock sink為其他接口和內部邏輯提供時鐘和時序參考,clock sink的屬性有clockRate,用來表示clock sink接口的頻率(Hz),默認值為0。

表1 Clock Sink信號

表2 Clock Sink屬性

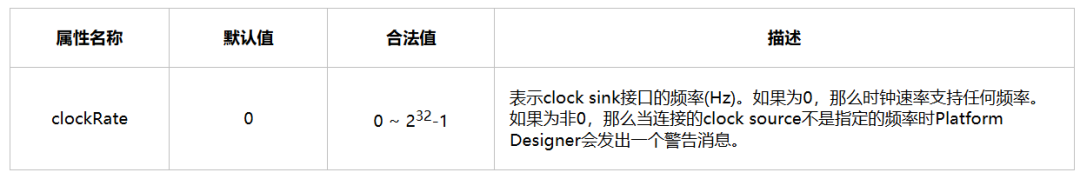

所有同步接口都有一個associatedClock 屬性,該屬性指定組件上的哪個時鐘源(clock source)用作接口的同步參考,如圖所示。

Clock Source信號

Clock source接口從一個組件中輸出一個時鐘信號。clock source有三個屬性,associatedDirectClock表示直接驅動該時鐘的時鐘名稱,clockRate表示時鐘輸出的頻率,clockRateKnown指示時鐘頻率是否已知。

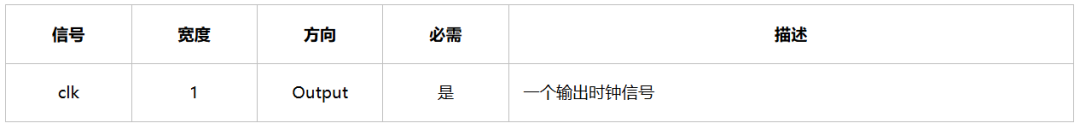

表3 Clock Source信號

表4 Clock Source屬性

Avalon復位接口

與Avalon時鐘接口類似,Avalon復位接口也分為Reset Sink和Reset Source。

Reset Sink

Reset sink包含兩個信號,reset/reset_n和reset_req,reset_req是一個可選的信號。Reset sink有兩個屬性,associatedClock表示與該接口同步的時鐘,synchronous-Edges表示復位所需要的同步類型,NONE表示不需要同步,DEASSERT表示復位是異步的,取消復位是同步的,BOTH表示復位和取消復位都是同步的。

所有同步接口都有一個associatedReset屬性,用于指定哪個復位信號對接口邏輯進行復位。

表5 Reset Sink信號

表6 Reset Sink屬性

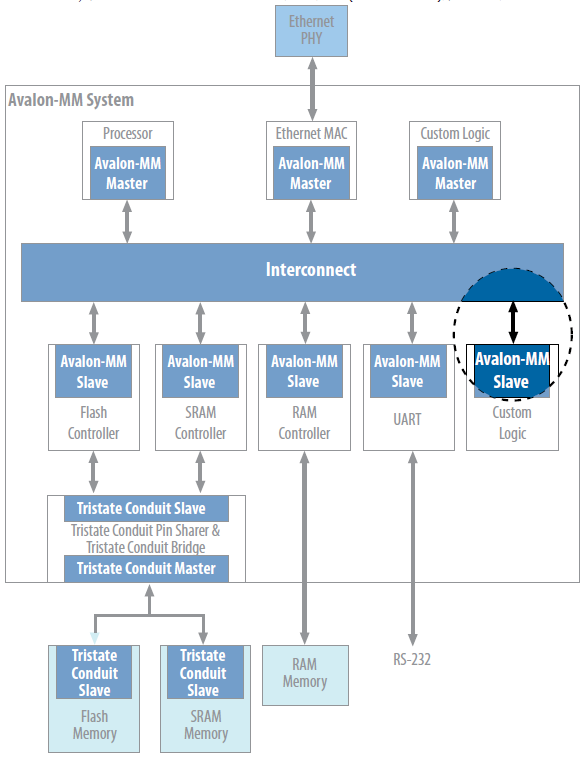

Reset Source

Reset source也是包含兩個信號,reset/reset_n和reset_req,reset_req是一個可選的信號。Reset source有四個屬性,associatedClock表示與該接口同步的時鐘;associatedDirectReset表示復位輸入的名稱,此復位輸入通過one-to-one 鏈路直接驅動此復位源;associatedResetSinks用來指定復位輸入,使復位源對復位進行復位;synchronous-Edges表示復位所需要的同步類型,NONE表示不需要同步,DEASSERT表示復位是異步的,取消復位是同步的,BOTH表示復位和取消復位都是同步的。

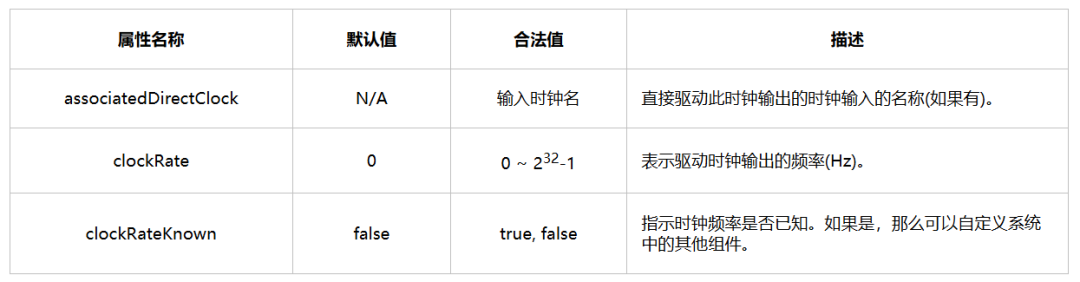

表7 Reset Source信號

表8 Reset Sink屬性

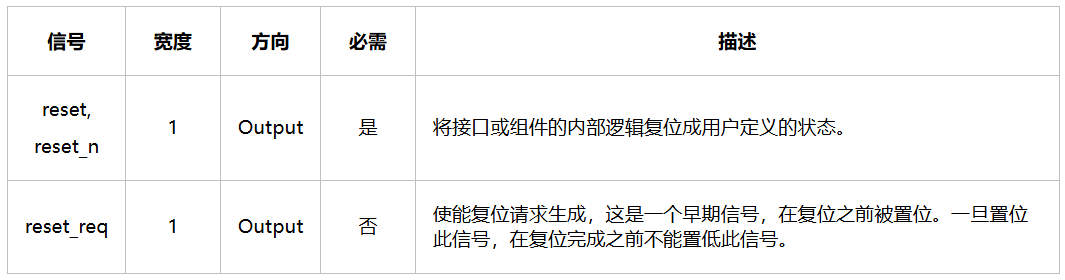

Avalon存儲器映射接口

Avalon存儲器映射接口主要用于實現主-從(Master-Slave)組件的讀寫接口,微處理器、存儲器、UART、DMA、定時器(Timer)是常用的包含Avalon存儲器映射接口的組件。Avalon-MM接口有簡單的也有復雜的。例如,SRAM接口有固定周期的讀寫傳輸,具有簡單的Avalon-MM 接口。能夠進行突發傳輸的流水線接口(pipelined interface)有更為復雜的Avalon-MM接口。這里我們只介紹簡單的Avalon-MM接口,較為復雜的流水線接口請參考Intel FPGA的Avalon Interface Specification文檔。

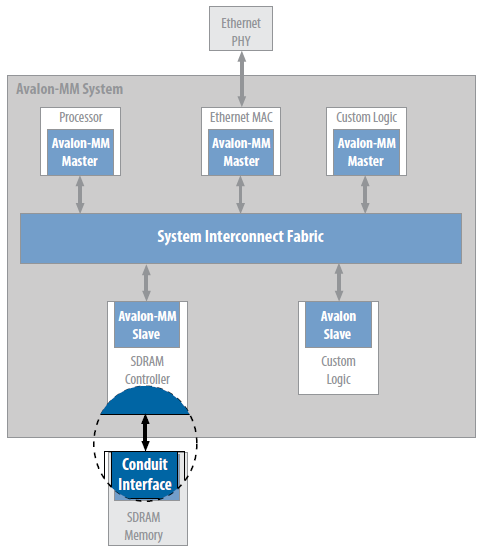

下圖是一個典型的系統,圖中加亮并畫圈的是Avalon-MM slave接口與互連(interconnect)架構的連接。

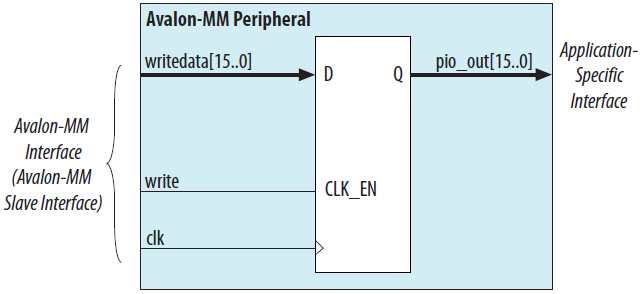

下圖為16-bit通用I/O外設僅響應寫請求,該組件只包含寫傳輸所需的從信號。

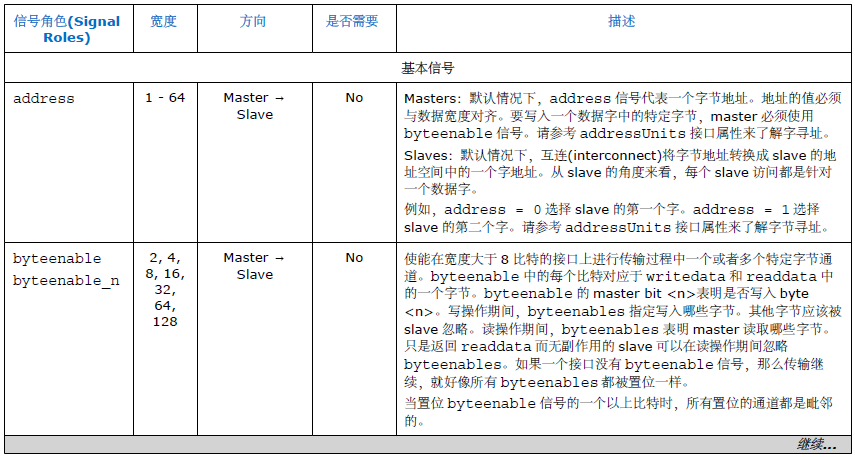

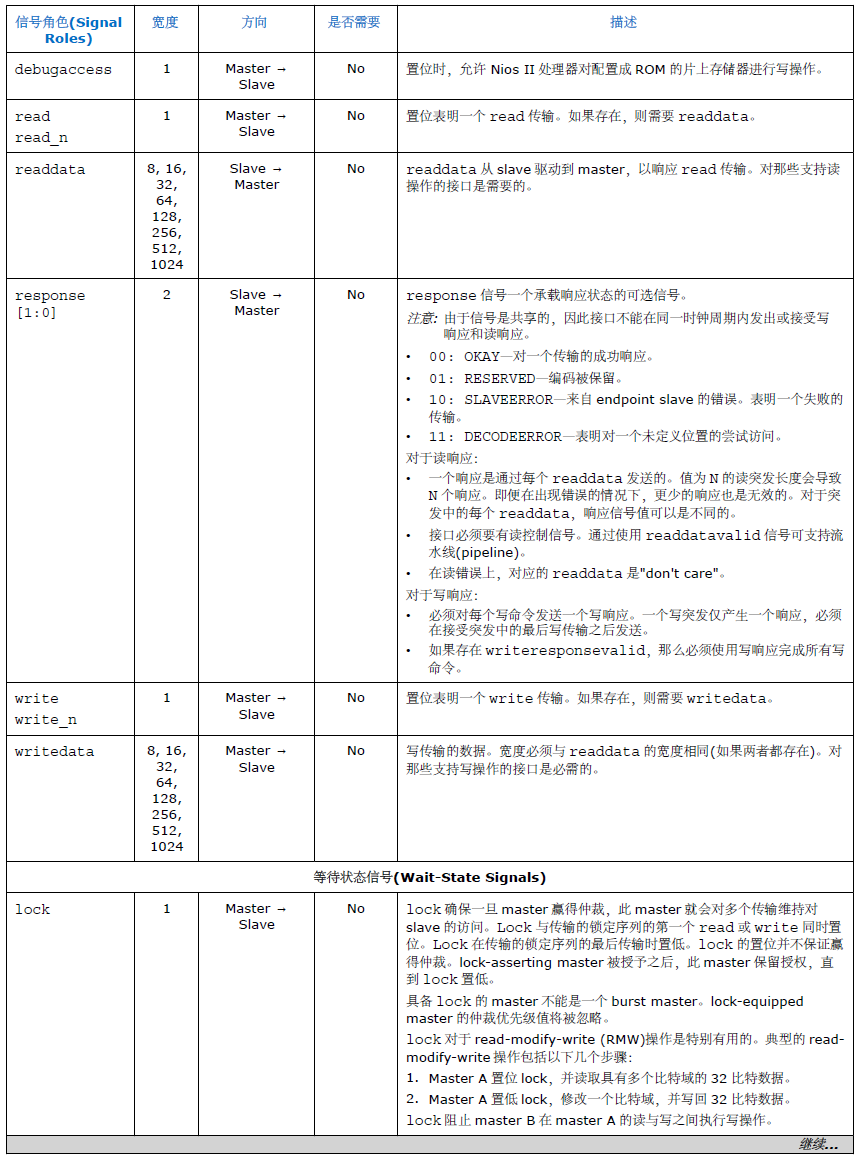

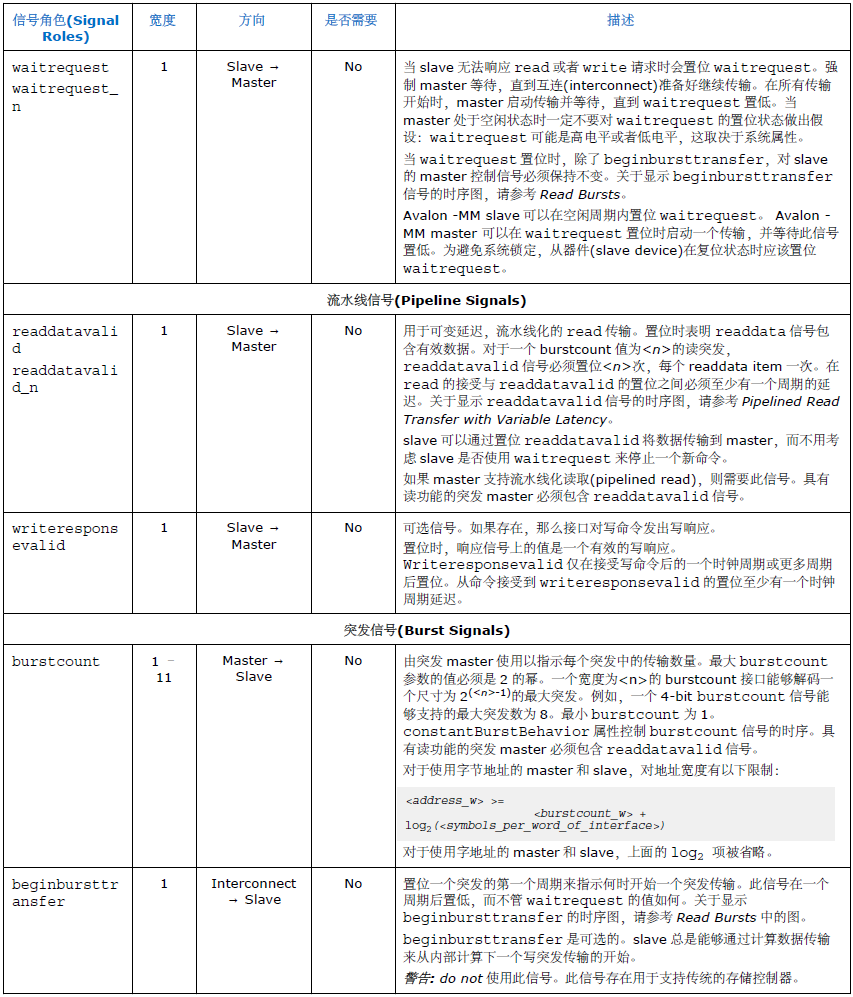

Avalon存儲器映射接口信號及屬性

Avalon Interface Specifications文檔的 Table 9列出了Avalon-MM接口的信號。。注意:Avalon規范不要求所有信號都存在于一個Avalon-MM接口中,即當一個接口為Avalon-MM接口時,只包含所需要的某些信號即可。例如,對于只支持讀操作(read-only)的接口,最少可只包含readdata信號;對于只支持寫操作(write-only)的接口,最少可只有writedata和wrtie信號。

表9 Avalon-MM接口信號

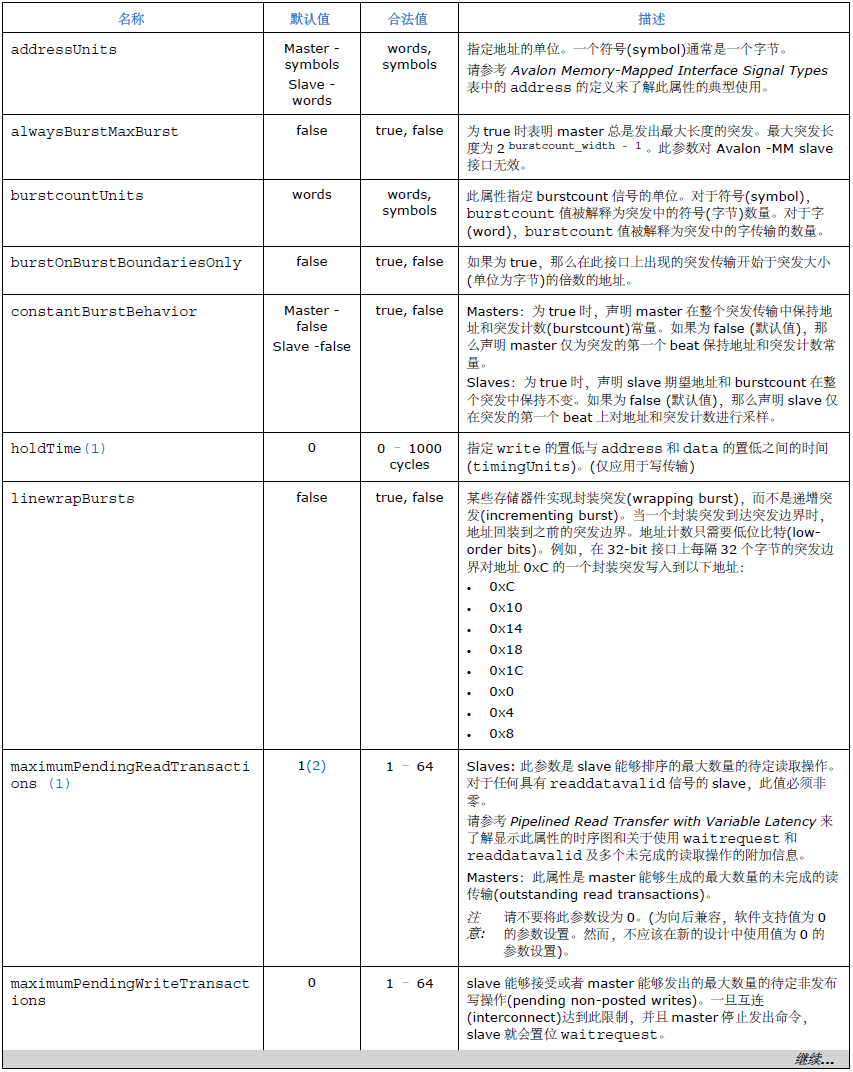

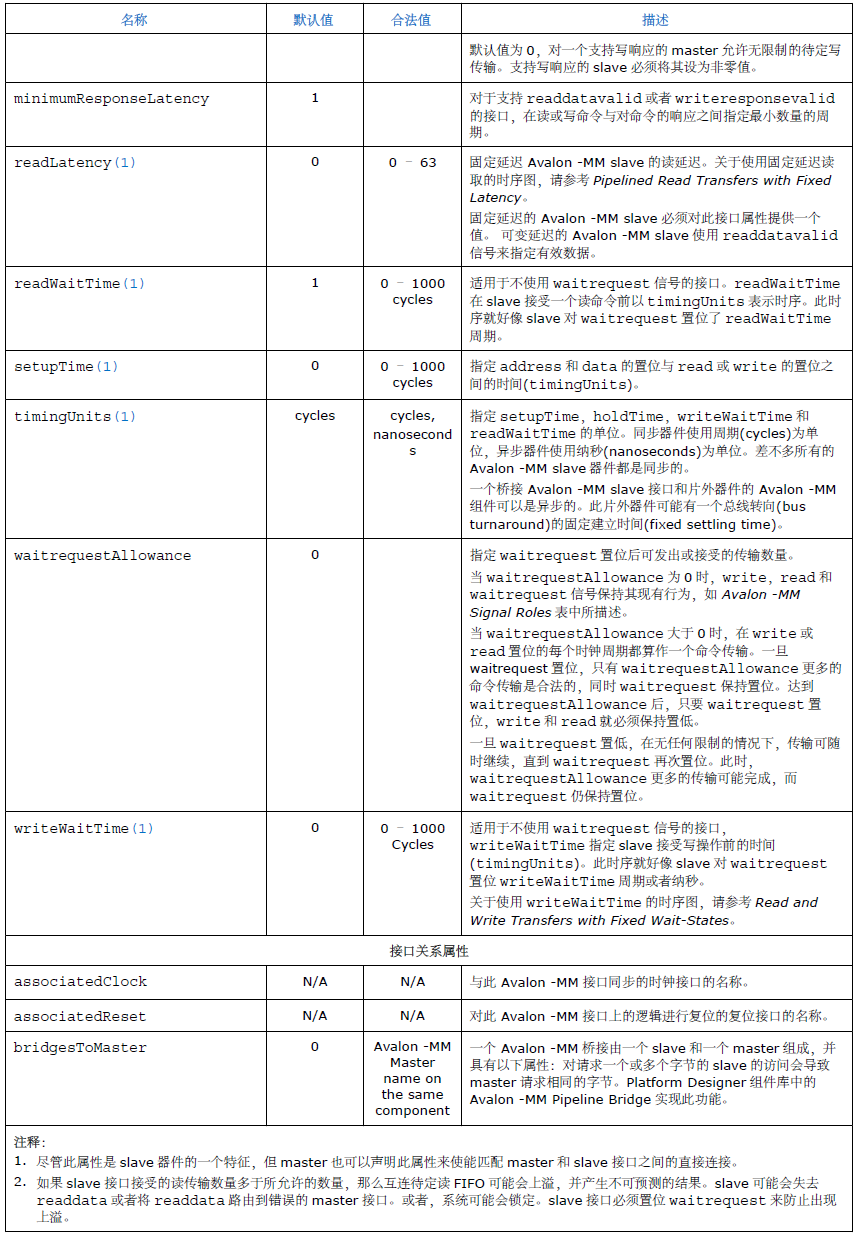

表10列出了Avalon-MM接口信號的屬性。

表10 Avalon-MM接口信號屬性

Avalon-MM典型的讀傳輸和寫傳輸

在介紹Avalon-MM典型的讀寫傳輸之前,先來介紹兩個基本概念:

傳輸(Transfer) -- 傳輸是一個字或者一個或多個符號的數據的讀或寫操作。傳輸發生在Avalon-MM 接口與互連之間。傳輸需要一個或多個時鐘周期才能完成。master和slave都是傳輸的一部分。Avalon -MM master啟動傳輸, Avalon -MM slave作出響應。

Master-slave pair -- 指在一個傳輸中涉及到master接口和slave接口。在一個傳輸過程中,master接口控制和數據信號遍歷互連架構,并與slave接口進行交互。

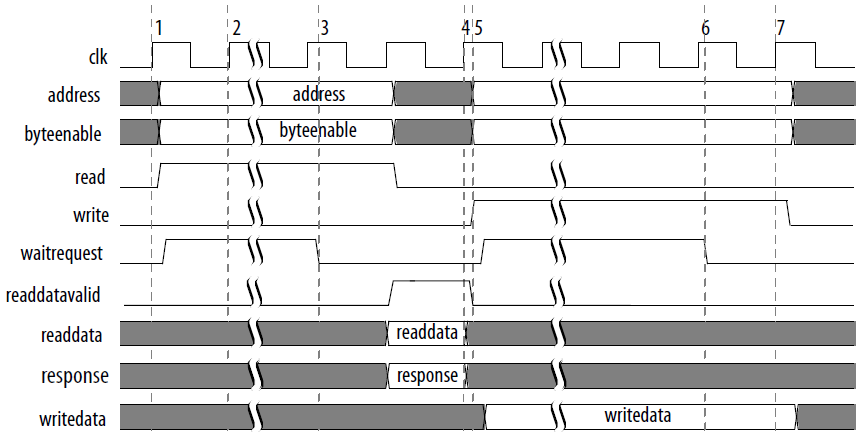

下面介紹一個典型的Avalon-MM接口進行讀寫傳輸的范例,該接口包含waitrequest信號,通過將waitrequest(高電平有效)信號置為高電平,slave可將互連暫停。

通常,slave在時鐘上升沿之后接收address、byteenable、read 或者write和writedata信號,在時鐘上升沿之前將waitrequest置為高電平來暫停傳輸。當slave拉高waitrequest信號時,數據傳輸被延遲,此時地址線和其他控制信號保持不變。在slave將waitrequest拉低后的第一個時鐘上升沿,讀寫傳輸完成。

Slave可以無期限的拉高waitrequest信號,但是在設計中必須確保slave接口不要無期限的拉高waitrequest信號,以免出現slave一直不響應、master一直等待的現象。下圖為使用了waitrequest的讀傳輸和寫傳輸。

我們來分析上圖中每個數字標注的時刻,Avalon-MM總線上的操作:

clk上升沿后,address、byteenable、read信號被置為有效;slave將waitrequest拉高,暫停數據傳輸。

clk上升沿,waitrequest被master采樣;由于waitrequest有效,此時處于等待狀態(wait-state),address、read和byteenable保持不變。

slave 在clk上升沿之后將waitrequest置為低電平,之后將readdata、responese置為有效。

clk上升沿,master檢測到waitrequest拉低,捕獲readdata、response,讀數據傳輸完成。

clk上升沿后,address、writedata、byteenable和write信號被置為有效;slave將waitrequest拉高,暫停數據傳輸。

slave 在clk上升沿之后將waitrequest置為低電平。

clk上升沿,slave捕獲到writedata,寫數據傳輸完成。

地址對齊

互連僅支持地址對齊的訪問方式。Master只能發送其數據位寬倍數的地址。Master可通過拉低byteenable_n的某幾位來寫入部分數據。例如,向地址2寫入2字節的數據時,byteenable_n = 4’b1100。

Avalon-MM尋址

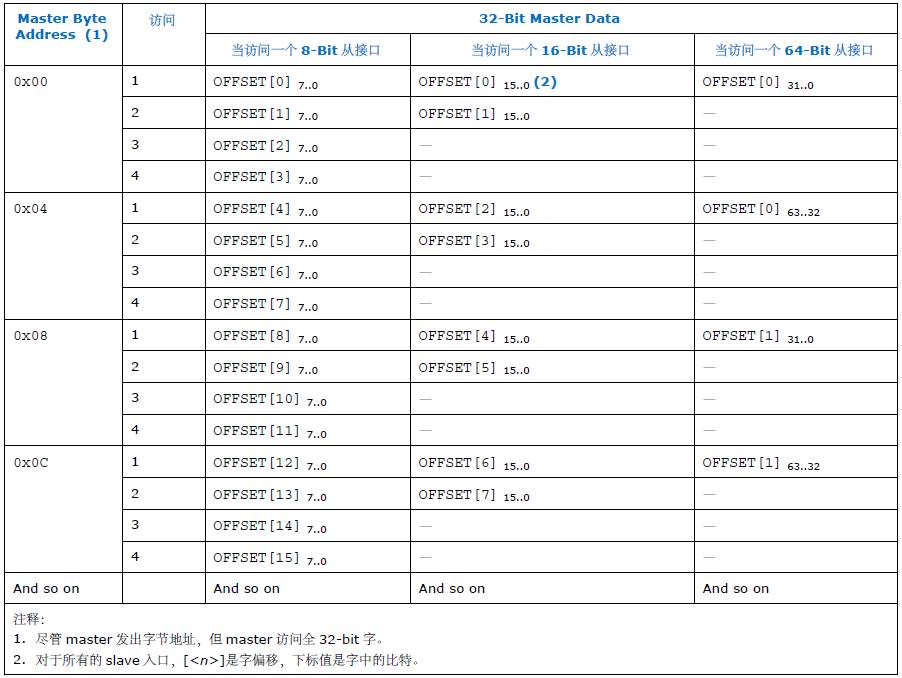

動態地址對齊(Dynamic bus sizing)在不同數據寬度的master-slave對傳輸期間管理數據。從機數據在主機地址空間中以連續字節的方式對齊。

如果master的數據寬度大于slave的數據寬度,mster地址空間中的字會映射到slave地址空間中的多個位置。例如,32位的master讀取16位的slave時,會在slave端進行兩次讀傳輸,這兩次讀傳輸的地址是連續的。

如果master的數據寬度小于slave的數據寬度時,互連會管理slave的各個字節通道。當master從slave讀取數據時,互連只會把相應的字節通道的數據傳輸給master。當master向slave寫數據時,互連會自動將相應字節通道的byteenables信號置為有效。

Slave的數據寬度必須是8、16、32、64、128、256、512 或者1024位。下表列出了32位的master按字訪問不同位寬的slave數據時是如何與master對齊的,OFFSET[N]表示slave地址空間字的偏移量。

表11 動態地址對齊的Master-Slave之間的地址映射

Avalon Conduit接口

Avalon Conduit接口是那些不適合任何其他Avalon類型的單個/多個信號的集合,使用該接口可以將信號導出到頂層SOPC系統,這樣就可以將它連接到設計的其他模塊。一個Avalon Conduit接口可以包括輸入、輸出和雙向信號,并且一個模塊/組件可以有多個Avalon Conduit接口。

管道(Conduit)接口通常用于驅動片外器件信號,比如SDRAM的地址、數據和控制信號線,如下圖所示。

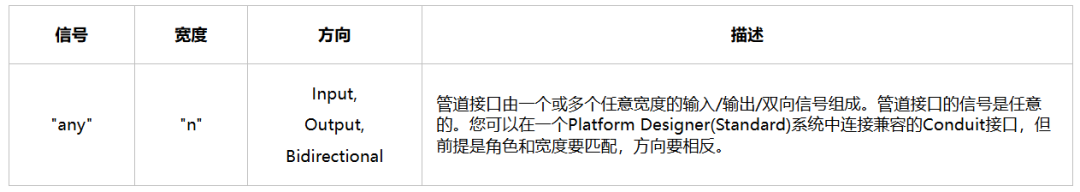

Avalon conduit接口的信號可以是任意的,并且該接口的信號沒有任何屬性。

表12 Conduit接口信號

-

處理器

+關注

關注

68文章

20289瀏覽量

253312 -

FPGA

+關注

關注

1662文章

22448瀏覽量

637593 -

Altera

+關注

關注

37文章

825瀏覽量

158910 -

總線接口

+關注

關注

0文章

94瀏覽量

31474

原文標題:Altera FPGA 的 Avalon MM總線接口規范介紹(精簡版)

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

轉載 --- altera_avalon_pio_regs.h中的函數意義

例說FPGA連載52:NAND Flash實例之總線的概念

例說FPGA連載53:NAND Flash實例之Avalon-MM總線

例說FPGA連載54:NAND Flash實例之Avalon-ST總線

如何設計一個基于Avalon總線接口的UPFC控制器IP核?

基于FPGA的SDX總線與Wishbone總線接口設計

通過Altera FPGA系統實現FPGA接口的簡化設計

Nios II處理器的體系結構及Avalon總線接口規范

設計一種跳轉到Avalon總線的簡單方法

Avalon總線規范介紹

Altera FPGA的Avalon MM總線接口規范介紹

Altera FPGA的Avalon MM總線接口規范介紹

評論