PCI-SIG 工作組打算發(fā)布每代信號速率翻倍的 PCI Express (PCIe) 版本。從 Gen1 開始,2.5 GT/s 的信令速率在 Gen2 中翻倍至 5 GT/s,原計劃在 Gen3 中翻倍至 10 GT/s。PCIe Gen1 和 Gen2 協(xié)議中的編碼需要 20% 的開銷,因此有效數(shù)據(jù)鏈路速率分別為 2 GT/s 和 4 GT/s。

該小組為 Gen3 確定了兩個選擇:將信令速率提高到 10 GT/s,保持協(xié)議的 20% 開銷不變,或者指定 8 GT/s 的較低信令速率和較低的編碼開銷。在對擴(kuò)展 PCIe 互連帶寬的技術(shù)可行性進(jìn)行了六個月的分析后,該小組確定可以采用主流硅工藝技術(shù)制造 8 GT/s。他們還確定 PCIe 可以與現(xiàn)有的低成本材料和基礎(chǔ)設(shè)施一起部署,同時保持與 PCIe 堆棧的完全兼容性。

通過將編碼要求從 8b/10b 提高到 128b/130b,新協(xié)議將編碼開銷降低到 1-2%。因此,PCIe Gen3 提供了 7.99 GT/s 的有效鏈接速率,從而使 PCIe Gen2 的有效鏈接速率翻了一番。編碼方案的改變還包括如下的加擾/解擾算法:x23 + x21 + x16 + x8 + x5 + x2 + 1。

PHY 實(shí)施挑戰(zhàn):發(fā)送、接收

抖動會阻礙大多數(shù)通信鏈路的完整性。這在高數(shù)據(jù)速率通信的情況下更為明顯。為了有效應(yīng)對這些挑戰(zhàn),工程師需要最大限度地減少產(chǎn)生的抖動并最大限度地提高抖動容限。在傳輸過程中,鎖相環(huán)形式的時鐘生成需要產(chǎn)生盡可能少的噪聲和抖動。

為此,一些設(shè)計人員實(shí)施了環(huán)形振蕩器,而其他設(shè)計人員則選擇了電感電容 (LC) 振蕩器。環(huán)形振蕩器會產(chǎn)生更多抖動,但在 5 GT/s PCIe Gen2 PHY 中仍然可以管理。然而,對于 8 GT/s 的 Gen3,LC 振蕩器的較低抖動,特別是降低隨機(jī)抖動,有助于將誤碼率降低到優(yōu)于所需的 10 -12。

PCIe Gen3 還集成了可選的擴(kuò)頻時鐘生成 (SSCG),以降低電磁干擾 (EMI) 的頻譜密度。如果沒有 SSCG,PCIe Gen3 將在時鐘頻率及其諧波上分布的許多窄帶上輻射 EMI。這導(dǎo)致頻譜在某些頻率下可能超過 FCC 和其他監(jiān)管限制(日本的 JEITA 和歐洲的 IEC)的 EMI。出于這個原因,一些制造商使用 SSCG 在消費(fèi)產(chǎn)品中實(shí)施 PCIe Gen3 并且仍然滿足 EMI 監(jiān)管要求。

PCIe Gen3 的最大損耗通道需要傳輸去加重和接收均衡。隨著數(shù)據(jù)速率增加到 8 GT/s,板載數(shù)據(jù)損失增加,因?yàn)閭鬏斁€充當(dāng)?shù)屯?a href="http://www.3532n.com/tags/濾波器/" target="_blank">濾波器并衰減更高頻率的傳輸。結(jié)果:數(shù)據(jù)看起來已損壞。Gen3 建議對發(fā)射機(jī)進(jìn)行去加重以提升高端頻率并去加重低頻。在 Gen3 中,去加重已增加到 7.5 dB,最小上升時間為 19 ps,而 Gen2 規(guī)范為 6.5 dB,最小上升時間為 30 ps。建議為 PCIe Gen3 發(fā)送器使用三抽頭前饋均衡器。

在接收端,傳輸需要從盡可能多的抖動和噪聲中恢復(fù)。不同的 PHY 實(shí)現(xiàn)使用不同的均衡方案。一些使用連續(xù)時間線性均衡 (CTLE),已證明足以滿足 5 GT/s 傳輸。但是,除了 CTLE,8 GT/s 傳輸還需要接收端的另一個階段,即決策反饋均衡 (DFE)。當(dāng)適當(dāng)平衡時,與完全依賴 DFE 相比,這兩種方案可以最大限度地降低功耗。這種平衡的兩級方法以盡可能低的功耗實(shí)現(xiàn)開放式眼圖。

具有較少抽頭數(shù)的 DFE 實(shí)施可降低功耗。通過使用必要的通道模型和平衡的 CTLE-DFE 進(jìn)行廣泛的系統(tǒng)分析,設(shè)計人員可以優(yōu)化 DFE 中使用的抽頭數(shù)量。MoSys 的 PHY 實(shí)施已經(jīng)在 10 GT/s SERDES 芯片中驗(yàn)證了該架構(gòu)。

控制器-PHY 互操作

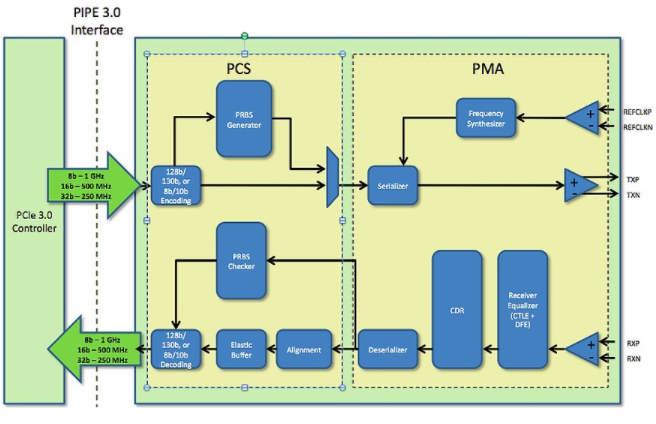

集成 PCIe Gen3 鏈路的片上系統(tǒng) (SoC) 設(shè)計必須同時處理控制器(也稱為 MAC 或鏈路層)和 PHY,如圖 1 所示。控制器與 SoC 的其余部分接口一方面通過片上總線,另一方面通過 PHY。PHY 接口由 PHY Interface for PCI Express (PIPE) 規(guī)范明確定義。因此,作為起點(diǎn),控制器和 PHY 都必須遵守 PIPE 規(guī)范,以保持合規(guī)性并確保互操作性。

圖 1:為確保互操作性,控制器和 PHY 必須與符合 PIPE 規(guī)范的 SoC 設(shè)計接口。

其他關(guān)鍵點(diǎn)

PCIe Gen3 需要幾個其他相關(guān)實(shí)現(xiàn),包括 3 dB、12 dB 和 20 dB 的三個不同的分線通道;800 mV 至 1,200 mV 的差分輸出電壓,具有 400 mV 的低功率選項(xiàng);和交流耦合和標(biāo)稱 100 歐姆差分終端。直流和奈奎斯特頻率下的差分回波損耗分別為 10 dB 和 15 dB。

MoSys 的 PCIe Gen3 IP 塊實(shí)現(xiàn)滿足當(dāng)前在 v0.71 中發(fā)布的所有要求,并提供 GDSII 文件中的物理介質(zhì)附件 (PMA) 解決方案和作為可綜合 Verilog 寄存器傳輸級別的物理編碼子層 (PCS)。

IP 準(zhǔn)備就緒

借助128b/130b 編碼方案和加擾多項(xiàng)式,PCIe Gen3 提出了許多傳輸和接收問題,所有這些問題都在最新規(guī)范中得到解決。MoSys 在當(dāng)前可用的電氣兼容 IP 塊中集成了 PCIe Gen3 功能,使 SoC 設(shè)計團(tuán)隊能夠繼續(xù)設(shè)計過程并在新產(chǎn)品中利用更高的 8 GT/s 速度。根據(jù)規(guī)范,這些模塊向后兼容早期規(guī)范的 2.5 GT/s 和 5 GT/s 速度。

作者:Ali Burney,Prasad Saggurti

審核編輯:郭婷

-

控制器

+關(guān)注

關(guān)注

114文章

17787瀏覽量

193090 -

寄存器

+關(guān)注

關(guān)注

31文章

5608瀏覽量

129968 -

PCIe

+關(guān)注

關(guān)注

16文章

1460瀏覽量

88400

發(fā)布評論請先 登錄

PCIe 接口-4路光纖處理卡-青翼科技高性能FPGA板卡

9FGV0441:PCIe Gen 1 - 4 應(yīng)用的低功耗時鐘發(fā)生器

【PCIE732】光纖卡,具備PCIe接口的萬兆光纖卡

深入剖析DS80PCI102:PCIe鏈路擴(kuò)展的得力助手

Amphenol ICC的PCIe? M.2 Gen 5卡邊緣連接器:高性能連接新選擇

Amphenol HD Express?:滿足PCIe? Gen 6需求的高性能互連系統(tǒng)

Amphenol Cool Express Link? EDSFF E3 2C PCIe? Gen 5/6 電纜連接器:高性能存儲連接的新選擇

Amphenol PCIe? Gen 6 Mini Cool Edge IO連接器:下一代高速互連解決方案

Xilinx高性能NVMe Host控制器IP+PCIe 3.0軟核控制器IP,純邏輯實(shí)現(xiàn),AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

鎵未來 Gen3 平臺重磅發(fā)布|六大核心突破,助力功率半導(dǎo)體產(chǎn)業(yè)再度升級!

PCIe Gen 5 CEM連接器技術(shù)解析與選型指南

PCIe Gen5/Gen6 信號傳輸可以用極細(xì)同軸線束嗎?

今日看點(diǎn):我國科學(xué)家研制出高精度可擴(kuò)展模擬矩陣計算芯片;Microchip 推出首款 3nm PCIe Gen 6 交換芯片

陸芯科技推出IGBT單管AU40N120T3A5

克服向PCIe Gen3遷移的SoC設(shè)計挑戰(zhàn)

克服向PCIe Gen3遷移的SoC設(shè)計挑戰(zhàn)

評論